allegro设计PCB操作(记录用)

目录

NOTES

输入

结构图DXF导入/导出

查看结构图

导入网表

布局

摆放

移动

查看器件坐标

定位器件到指定坐标

与结构图对齐

丝印

布线

测试点/开关等处添加泪滴

高亮

铺铜

电源岛

添加电源岛

编辑电源岛

禁铺区

DRC检查

Package to Package Spacing

显示丝印/封装

Line to Route Keepin Spacing

Line to Route Keepout Spacing

skill集成工具整板检查

danglingline

No Silkscreen Ref Error丝印缺失

更新钻孔表

阻焊开窗

NOTES

为尽量减少软件卡顿造成的文件丢失,需要注意:

1)随时保存,尤其是在编辑铜皮前后

2)减少快捷键的使用

3)万一还是不幸卡顿了,在任务管理器强制退出后,在文件夹里找到后缀为brd.clk的文件删除,然后打开autosave或是之前已保存的文件

输入

结构图DXF导入/导出

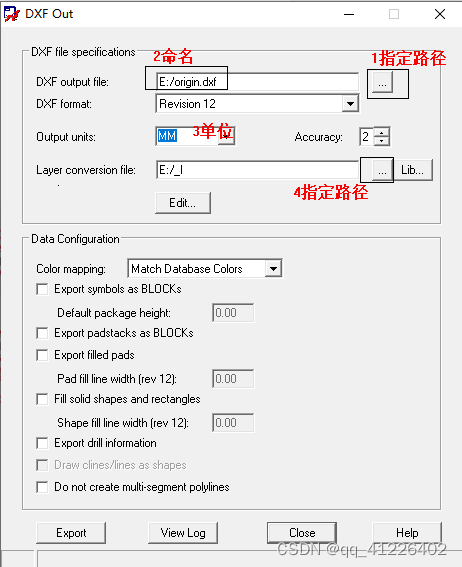

Allegro如何导入导出DXF

1.不止根目录,整个路径都不能包含非法字符(比如中文)

2.在.dxf前输入文件名,依然不能出现非法字符

4.指定路径后无需更改命名,容易出现软件卡顿

5.edit

查看结构图

在PCB文件里使用F3/F4快捷键可以查看正/反面的结构图

导入网表

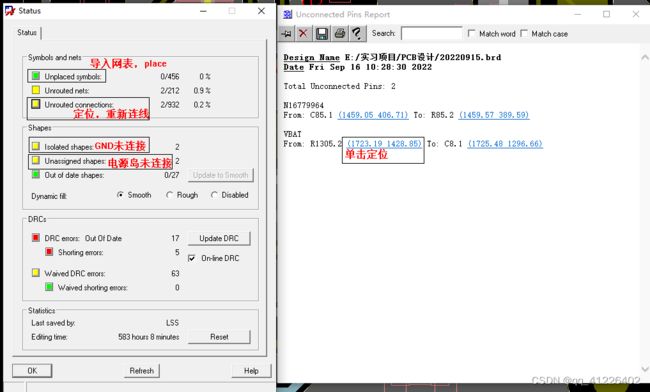

file -> import -> logic -> 选择网表根路径 -> import cadence -> import successfully -> place -> quick place -> OK

导入后在BRD的文件夹里会生成eco文件,显示新放置的器件。后面在PCB板打样时,也可以用这个文件检查PCB与原理图文件是否对应。

错误:

#1 WARNING(SPMHNI-192): Device/Symbol check warning detected. [help]

WARNING(SPMHNI-194): Symbol '0402 {RefDes C4}' for device 'C_0402_1UF_10V_0402' not found in PSMPATH or must be "dbdoctor"ed.

原因:在“D:\Allegro_Lib\allegro_lib_dra”封装库里没有“0402”封装,询问了CAD部门,0402和0201没有兼容封装,将C4封装改回默认类型,导入成功。

布局

摆放

1、插件器件的摆放要尽可能一致(尤其是有极性的器件),插件电解电容的方向不多于两个

检查全板器件摆放方向:Options栏选Package geometry

移动

查看器件坐标

选中器件 -> 右键“show element”

定位器件到指定坐标

选中器件 -> 右键“move” -> 命令窗口输入坐标,如“x 10 y 10” -> 回车

与结构图对齐

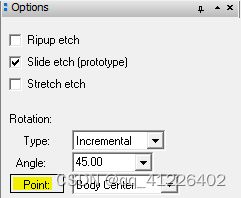

在移动状态下设置point,然后在目标位置附近右键 -> snap pick to -> circle center(圆孔中心)/intersection(交叉处)

丝印

自动调整丝印:

命令窗口键入refs -> silkscreen_top/silkscreen_bottom/assembly_top/assembly_bottom(依次选取) -> textblock autoset -> 字号small -> refs error check -> 全选 -> fix -> refresh

手动调整丝印:命令窗口键入refs -> silkscreen_top/silkscreen_bottom/assembly_top/assembly_bottom(依次选取) -> 对话框最小化不要关闭 -> find栏只选text

要求:

– 文字不能太靠近pad,至少保持6mil间距

– 文字不可放置于零件实体下面

– 文字的方向应保持一致,至多可以有两种方向

布线

测试点/开关等处添加泪滴

泪滴常使用场景:插件焊盘添加泪滴,常用于加强插件焊盘与较细走线的连接强度,避免在焊接拆

卸不顺时或受其他作用力时焊环被抬起脱离PCB表面并撕短走线;阻抗控制的部分贴片焊盘位置添

加泪滴。

工具栏Route -> gloss -> add fillet / parameters -> Find栏选中pins -> 单击焊盘

高亮

Find栏选中nets -> 右键highlight

取消高亮:Dehighlight

取消高亮之前先判断是不是报错导致的高亮

差分线

铺铜

编辑铜皮之后切记要保存!保存!!

动态敷铜

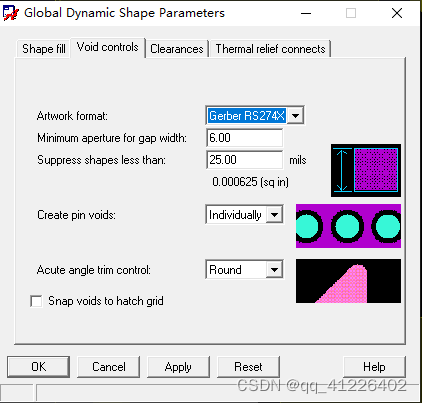

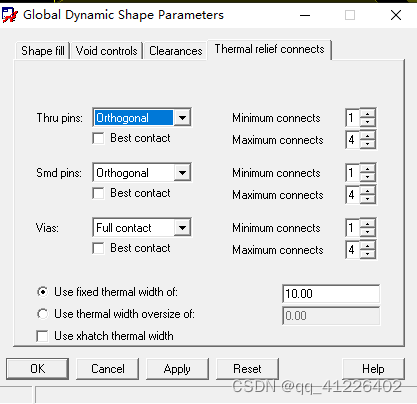

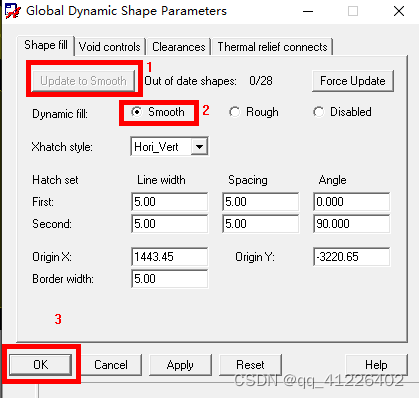

设置全局参数

shape -> global dynamic parameters

铜皮避线

allegro铺动态铜皮时并没有自动避线是什么原因_飞向蓝天2的博客-CSDN博客_allegro铜皮不避让

全局敷铜

框线:board geometry -> outline(与DXF外形相同)

Route Keepin 用来标记PCB允许Layout的区域

步骤:设置全局动态参数 -> shape -> rectangle -> etch -> top/bottom -> assign net name :GND -> 画出比框线大的矩形

电源岛

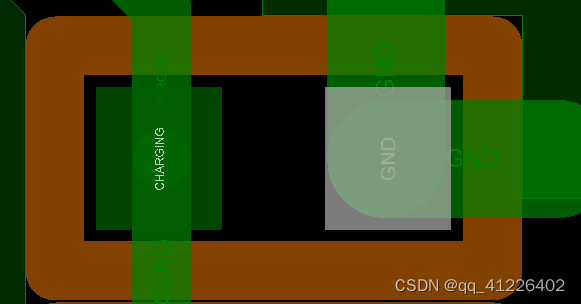

添加电源岛

工具栏shape -> polygon或rectangular -> options栏选择etch、选择分层 -> assign net name选择网络名

编辑铜皮

Find栏选Shapes -> 选中电源岛 -> 工具栏Shape -> edit boundary

禁铺区

在功率电感、晶体下方要进行禁铺处理。

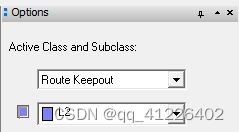

步骤:工具栏Shape -> polygon / rectangle -> Options栏选route keepout -> 选择分层并点击前面方块(删除禁铺区的步骤类似)

孤岛

孤岛可以用禁铺处理去除(不过最好选择调整走线位置或打孔来去除孤岛)。

或使用图中的删除孤岛功能:shape选中孤岛,点island_delete,再点一次孤岛,done

DRC检查

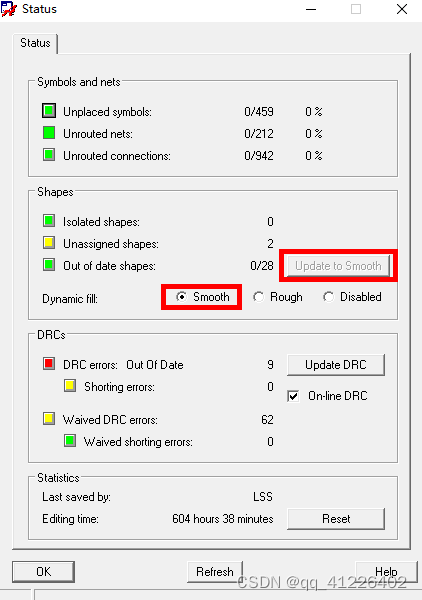

display -> status出现左图 -> 点击左图中的方框可以打开右图

一般情况下要求前六项全绿

Package to Package Spacing

显示丝印/封装

display -> color/visibility -> package geometry -> 勾选display_bottom、silkscreen_bottom -> apply

元器件距离问题可以看下面两栏信息,方便定位

Line to Route Keepin Spacing

原因:走线在Route Keepin之外

解决:定位发现是标题栏,忽略

Line to Route Keepout Spacing

原因:走线在Route Keepout之内

解决:在侧边的options栏选route keepout,然后勾选分层,可以查看禁铺区

skill集成工具整板检查

skil -> multitools -> 整板检查 -> 一键执行 -> 弹出“选择热焊盘” -> OK -> done

danglingline

这里介绍一个简单的去除掉dangling线的方法,不需要你对着cline segs一点点寻找和删除:

route——Gloss—–parameters

弹出选项窗口点 line smoothing 这一任务项,然后ok,然后点gloss即可消除dangling线。

Allegro技巧:删除dangling线_RhythmWANG的博客-CSDN博客_allegro dangling line如何解决

No Silkscreen Ref Error丝印缺失

Setup -> Application Mode -> Placement Edit -> 在Find侧边栏下选中Symbols -> 光标放置在封装上面 -> 右键选择Refresh Symbol Instance

Cadence Allegro PCB中误删封装丝印如何恢复_廖光铖的博客-CSDN博客

更新钻孔表

manufacture -> NC -> drill legend

阻焊开窗

allegro学习之如何开窗_weixin_37879993的博客-CSDN博客_allegro开窗