【Verilog-HDLBits刷题】2022.02.22学习笔记

1、ripple-carry adder:行波进位加法器,别名:逐位进位加法器。

半加器:HA,Half-Adder

全加器:FA,Full-Adder

设计逐位进位加法器时,可以多次实例化全加器模块。见例一。

2、generate的结构类型:

①可用来构造循环结构,用来多次实例化某个模块;

②构造条件generate结构,用来在多个块之间最多选择一个代码块,条件generate结构包含if–generate结构和case–generate形式。;

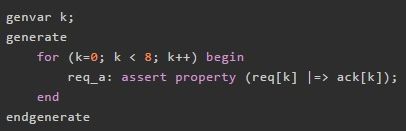

③用来断言。

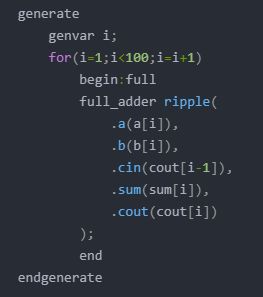

对于①generate循环结构:在使用时必须在genvar声明中声明循环中使用的索引变量名(整数类型),then才能使用它;必须要在引用实例时对模块进行命名,也就是需要begin:**命名** 实例化 end; genvar只有在建模的时候才会出现,在仿真时就已经消失了。

通常,generate for循环和普通 for循环之间的主要区别在于generate for循环正在为每次迭代生成一个实例。

例子如下:

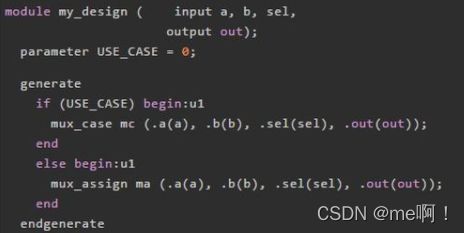

对于②条件if-generate构造:从很多的备选块中选择最多一个generate块(也可能一个也不选择)。例子如下:

对于②条件case-generate构造:与if-generate类似,case-generate也可用于从几个块中有条件地选择一个代码块。它的用法类似于基本case语句,并且if-generate中的所有规则也适用于case-generate块。例子如下:

对于③断言:例子如下

例一:1与2结合的例子

题目:Create a 100-bit binary ripple-carry adder by instantiating 100 full adders. The adder adds two 100-bit numbers and a carry-in to produce a 100-bit sum and carry out. To encourage you to actually instantiate full adders, also output the carry-out from each full adder in the ripple-carry adder. cout[99] is the final carry-out from the last full adder, and is the carry-out you usually see.

分析:用全加器创建一个100位的行波进位加法器。

解答:

module top_module(

input [99:0] a, b,

input cin,

output [99:0] cout,

output [99:0] sum );

assign {cout[0],sum[0]}=a[0]+b[0]+cin;

generate

genvar i;

for(i=1;i<100;i=i+1)

begin:full

full_adder ripple(

.a(a[i]),

.b(b[i]),

.cin(cout[i-1]),

.sum(sum[i]),

.cout(cout[i])

);

end

endgenerate

endmodule

module full_adder(

input a,b,cin,

output sum,cout

);

assign {cout,sum}=a+b+cin;

endmodule

3、判断多bit数是否相等,可以直接:assign z = (A[1:0] == B[1:0] ) ? 1 : 0 ;

或者:assign z = (A[1:0]==B[1:0]);

因为==本身就是用来判断的,不用写后面的选择项也可。

4、判断第i位与第i+1位是否相同,不仅可以用for循环,还可以直接赋值比较

例如:assign out_different = in ^ {in[0], in[99:1]};代表[99:0]位宽的in,其第i位与第i+1位进行比较,第99位与第0位比较,所得结果如上代码所示。

5、题目:Create a 4-bit wide, 256-to-1 multiplexer. The 256 4-bit inputs are all packed into a single 1024-bit input vector. sel=0 should select bits in[3:0], sel=1 selects bits in[7:4], sel=2 selects bits in[11:8], etc.

分析:

我起初写的答案是in[ sel*4+3 : sel*4 ],但报错“… is not a constant”这个问题是it couldn’t prove that the select width is constant,后续更改答案为:assign out = {in[sel*4+3], in[sel*4+2], in[sel*4+1], in[sel*4+0]}; 正确,这是因为verilog中只允许起始或终点发生变化,其他保持常量,以保证宽度不发生改变。

后记:今天是2022.02.22,周二,农历正月二十二,据说这是含爱量最高的一天,但其实,爱,和日期并没有什么关系,它只是它,恒久微妙的存在。