汇编语言程序设计--基于ARM

环境 :DOSbox

自动挂载:无需每次打开都要手动挂载

设置Dosbox自动挂载_柬纸的博客-CSDN博客_dosbox自动挂载

第一章 基础知识

进制数:按位权展开

字符编码:ASCII / Unicode

数字编码:BCD(4位代表一个数字)

奇偶校验码:设置一个监督位,表明奇校验或偶校验,通过异或位来校验结果

海明码:能够检验和纠错

反码,补码:符号位不用变

补码运算:符号位也参加运算,且有以下规则

可以通过OF或双符号位来判断是否溢出

定点:分为定点小数和定点整数 ---- 但只能处理纯小数或纯整数,所以引入了浮点数

浮点数:分为尾数,解码,阶符,数符-----------EEE二进制浮点数算术标准

第二章:ARM微处理器

嵌入式系统:

系统内核小,专用性强,系统精简,高实时性的系统软件,多任务操作系统,需要专用的开发工具和环境

基本结构:

设备驱动层:

1) 硬件抽象层: 位于操作系统内核与硬件电路之间的接口层,目的在于将硬件抽象化,可以通过程序来控制硬件操作,提高了移植性

2)板级支持包:位于主板硬件 和 操作系统驱动层程序 之间的一层,主要实现对操作系统的支持,一般认为属于操作系统第一部分

3)设备驱动程序: 驱动程序为上层软件提供设备的操作接口,软件不用理会设备的具体内部函数;

-------------

操作系统的应用程序接口:API

某些操作可以通过操作系统或硬件本身具有的标准指令来调用,而无需重新编写程序;

ARM 概述:

ARM: advanced RSIC Machines -- 先进的精简指令集机器

计算机体系结构的分类:

冯诺依曼体系:数据和指令都储存在一个储存器中

哈佛体系结构:数据和指令各自分开

ARM特点:

RISC

随着ARM的架构不断地变换升级,最主要的是指令集在不断地变化

CISC:复杂指令集计算机 但只有20%的指令被频繁使用,所以提出了RISC

主要改变:

1 减少指令

2 将指令长度固定,指令格式和寻址方式种类减少;

3 以控制逻辑为主

流水线技术:

简单的三级流水线:

取指级,译址级,执行级 ----每一级中的硬件都可以独立操作

不用等一个进程全部执行完再执行下一个

超标量技术:

重复设置多套指令执行部件,实现并行操作

ARM硬件结构:

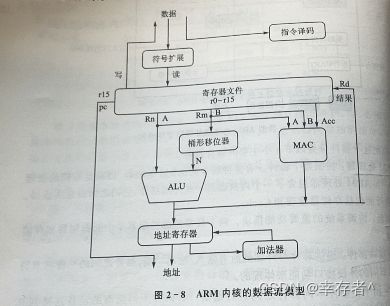

数据流模型:

ALU:运算器-来运算地址

MAC:乘累加单元

每一条指令都属于一个指令集。与所有的RISC处理器一样,采用Load-store 体系结构:

没有直接操作存储器的数据处理指令-只能通过寄存器来完成

ARM处理器的工作模式和 工作状态

处理器工作模式:

7种

工作状态:

ARM状态: 执行32位的ARM指令集

Thumb:执行16位的thumb指令集

可以随意切换,不影响数据内容和 工作模式

ARM寄存器

一共有37个32位寄存器: 31个为通用寄存器,6个状态寄存器

最多有18个寄存器同时活动:16+2(状态)

分为:

1) 通用寄存器:用于保存数据和地址

2) 状态寄存器:用来标识或设置工作模式,状态等功能

注意: thumb寄存器是ARM状态下寄存器的一个子集

通用寄存器

1)未分组寄存器: 在所有工作模式下,未分组寄存器都指向同一个物理寄存器

2) 分组寄存器:访问的寄存器跟当前的工作模式有关

3)程序计数器(PC):program counter ,指向CPU运行的下一条指令

状态寄存器

1个当前程序状态计数器(CPSR):current program system Register-可在任何工作模式下被访问,用来保存ALU中当前的操作信息,控制允许,禁止中断,设置处理器,工作模式等

5个备份的状态寄存器(SPSRs):用来进行异常处理

条件标识码:可以被运算结果改变,也可以决定指令是否被执行(条件码)

控制位:当发生异常时可以被改变

1) 中断禁止位:I (IRQ) F(FIQ):当标志为1时,表示禁止此类中断

2)T标识位:用来表示工作状态 1位 thumb 状态

3) 工作模式为:有不同组合

保留位:用于ARM的扩展

ARM储存结构

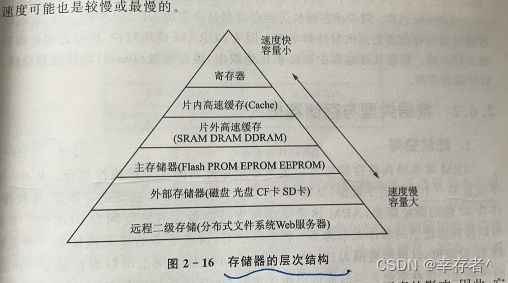

储存器可分为(内存):

1)随机存储器RAM

SRAM:静态随机存储器

DRAM:动态随机存储器 DDRAM-双倍速率-

2) 只读存储器ROM

掩膜ROM, prom,eprom,eeprom,flash memory (NOR / NAND)等

存储器的层次结构(宏观):

数据类型与存储器格式

地址空间:从0开始的线性组合

数据类型:可以最大为32位指令或向下兼容(16位)

储存格式:小端---低地址放在低字节 ---DOSbox默认显示此类

当非对齐指令时:要么结果不可预知,要么相应位被舍弃

第三章: ARM的指令系统

ARM指令集总览:

ARM指令集详解_流岚虹霓的博客-CSDN博客_arm指令集

Thumb指令集

为了兼容16位的指令集,允许16位编码

通常在32位数据总线宽度时,ARM指令集效率更好,16位则Thumb

每一条Thumb指令都有一条32位ARM指令相关--译码成等效的ARM指令

周期

时钟周期:一个时钟脉冲的长度称为一个时钟周期,是计算机系统时间基准,也是重要的性能指标

时钟频率(主频):时钟周期的倒数,很大程度上决定了微处理器的处理能力

指令周期:微处理器执行一条指令所需的时间,不同指令的周期不同

1) 不连续周期N:和上一个地址没关联

2) 连续周期S:地址相连接

3) 内部周期I:不请求传输,执行一个内部功能

4) 协处理器传输周期C:与协处理器在总线上传输一个字的周期

各种周期至少与时钟周期一样长

执行过程

像流水线特点一样分为取值指,译码,执行等阶段:通过三种总线和PC来完成

指令和指令格式:

指令

格式

<条件操作码>{条件域}{S-决定是否影响标志位}<目的寄存器><第一个操作数-寄存器>{第二个操作数}

<>为必须具有

{}为可选择后缀

后缀S:

加在操作码后面表示影响条件标志位,永远在在最后面,例如和条件执行码一起时

后缀!:

表示改变基地址的值,若用在单个寄存器后,必须有隐形的偏移量

条件执行

当加上条件标识码,符合该条件时,才执行

注意:是执行前检测,与S不冲突

ARM寻址方式

立即数寻址:#前缀

寄存器寻址:用寄存器里的数据当做操作数

寄存器间接寻址:寄存器的数据当做操作数的地址,通常用[]表示

移位寻址:配合指令 如LSL+# * 等来对寄存器进行移位,然后当做操作数

基地址寻址:用寄存器的数值当做基地址,立即数当做偏移地址 如ds[4] ==[ds+4]

多寄存器寻址:寄存器用{}包括 逗号隔开,连续的用-表示

相对寻址:用符号跳转(当做偏移量,其实也是偏移地址)

stack寻址:用LIFO的方式来获得地址 pop,push等

数据处理指令

传送指令:

mov

movn:将数据取反传送

移位操作(搭配寄存器使用)

LSL: logical shift right 逻辑左移

LSR: 逻辑右移

ASR:算术右移(左边补符号)

ROR:循环右移

RRX:带进位的循环右移

算术指令:

一般三个操作数,第一个是目的寄存器

数字常量表达式:

add:加法

adc:带进位的加法--->RD=Rn+op2+c(进位)

sub:减法

sbc:带借位的减法-->

rsb:逆向减法,RD=op2-RN

rsc:带借位的逆向减法

位运算指令:

and:与运算

or:或运算

xor:异或

bic:位清除 Rd=Rn and (!operand2),清除某些特定位置位置

比较指令:

会自动改变spsr中的标志位

cmp:比较

cmn:反向比较

TST:位测试 --------------与另一个操作数进行与操作,常用与检查特定位

TEQ:与另一个数进行 异或操作 , 常用与比较

乘法指令:

乘加:先乘之间两个,再加最后一个,再移动

数据加载与存储指令

分为LDR(Load R):寄存器<------存储器 str(store):寄存器---->存储器

总览:

注意 后面的一个操作数一定是个地址!

根据是否改变基地址 分为三种类型:

都是先操作[ ] 里的内容

1) 前索引(不改变基地址的值)

- 表示 基地址减去后面的立即数/寄存器内容

2)自动索引 :加上! 改变基地址

3)后索引 :最后改变基地址

后面两种在遍历时很有用,相当于两条指令合一起,避免了额外的指令时间和代码空间开销

----------------

第四章:ARM汇编程序设计

伪指令一览:

关于ARM伪指令_乱舞春秋丶的博客-CSDN博客_arm伪指令

C+汇编

C语言&汇编混合编程 - 知乎 (zhihu.com)

C语言与汇编语言混合编程_zhengqijun_的博客-CSDN博客_c语言和汇编语言混合编程实例

第五章:异常和中断

ARM中的异常和中断_bird67的博客-CSDN博客

ARM异常及中断处理介绍(中断是异常的一种)_凡人不会死的博客-CSDN博客_arm中断和异常的区别

7种异常(内含两中断)

概述:当ARM处理器执行协处理器指令时,它必须等待一个外部协处理器应答后,才能真正执行这条指令。若协处理器没有响应,则发生未定义指令异常。若试图执行未定义指令,也会出现未定义指令异常。未定义指令异常可用于在没有物理协处理器的系统上,对协处理器进行软件仿真,或通过软件仿真实现指令集扩展。

3.软中断异常

概述:软件中断异常指令SWI进入特权模式,执行一些特权模式下的操作系统功能。

4.预取异常

概述:预取异常是由系统存储器报告的。当处理器试图去取一条被标记为预取无效的指令时,发生预取异常。如果系统中不包含MMU,指令预取异常中断处理程序只是简单地报告错误并退出;若包含MMU,引起异常的指令的物理地址被存储到内存中。

5.数据异常

概述:数据异常时由存储器发出数据中止信号,它由存储器访问指令Load/Store产生。当数据访问指令的目标地址不存在或者该地址不允许当前指令访问时,处理器产生数据访问中止异常。

6.外部中断异常

概述:当处理器的外部中断请求引脚有效,并且CPSR寄存器的I控制位被清除时,处理器产生外部中断异常。系统中各外部设备通常通过该异常中断请求处理器服务。

7.快速中断异常

概述:当处理器的快速中断请求引脚有效且CPSR寄存器的F控制位被清除时,处理器产生快速中断异常。

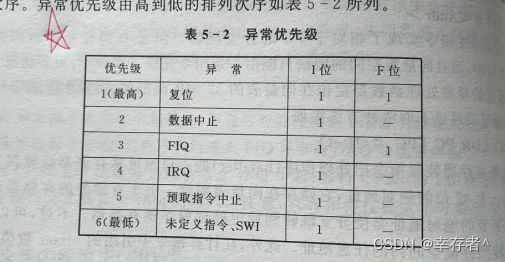

优先级:

对于两种中断请求,主要还是看 I位和 F位

注意点:

1)ARM把中断(IRQ,FIQ)定义为一类特殊的异常。默认中断是不可重入的(不能同时再发生同样中断)

2)FIQ和IRQ一般由外部设备引起的

FIQ优先级比IRQ高,FIQ处理比较紧急的事物

FIQ异常处理程序放在向量表的后面,这样避免了跳转的损耗,可以直接顺序执行

3)CPSR标志寄存器中 I位置1表示禁止IRQ中断 F位置1表示禁止FIQ中断

4)SWI中断为软件中断,用户请求的功能,如dos下的 int 21h +特定寄存器参数来进行主动调用