PCI Express解析——系列文章【4】:PCIe原理分析之——PCI Express系统模块、PCIe体系结构

PCI Express解析——系列文章【4】:PCIe原理分析之——PCI Express系统模块、PCIe体系结构

- 2.3 PCI Express系统模块图

- 2.4 PCI Express体系结构

-

- 2.4.1 事务层

-

- 2.4.1.1 事务分类

- 2.4.1.2 事务层应答机制

- 2.4.1.3 TLP数据包格式

- 2.4.2.4 TLP路由类型

- 2.4.2 数据链路层

- 2.4.3 物理层

- TLP在PCIe数据包的位置解析

-

- (1)发送端:

- (2)接收端

前文我们了解了一下关于PCIe的拓扑结构,这节我们看一看PCIe在一个典型的系统中如何组织,以及最重要的其自身的体系结构(层级结构、事务等)。

学习整理,如果有用或者有一丢丢用可以关注收藏点赞嘻嘻,帮助理解,如果细小问题可联系修改。

Author: Nirvana Of Phoenixl

Proverbs for you:There is no doubt that good things will always come, and when it comes late, it can be a surprise.

PCI Express解析——系列文章【1】:基本概述PCI、PCI-X与PCIe的最大区别

PCI Express解析——系列文章【2】:PCIe原理分析之——PCI Express线路基础

PCI Express解析——系列文章【3】:PCIe原理分析之——PCI Express拓扑结构

PCI Express解析——系列文章【5】:PCIe原理分析之——PCI Express系统模块、PCIe体系结构

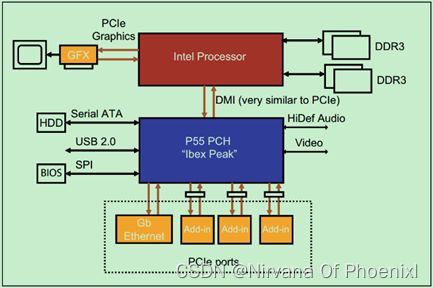

2.3 PCI Express系统模块图

PCIe总线是一种点对点(Point-to-Point)的总线,如果需要连接大量的设备,则需要很多的Switch来进行拓扑,这无疑会大大地增加系统的功耗与设计成本。在普通的PC或者小型计算机系统中,并不要连接很多的PCIe设备,因此Switch就显得并不是那么的必要了。一个典型的服务器PCIe总线系统的拓扑结构图如下图左所示,典型的PC的PCIe总线系统的拓扑结构图如下图右所示:

2.4 PCI Express体系结构

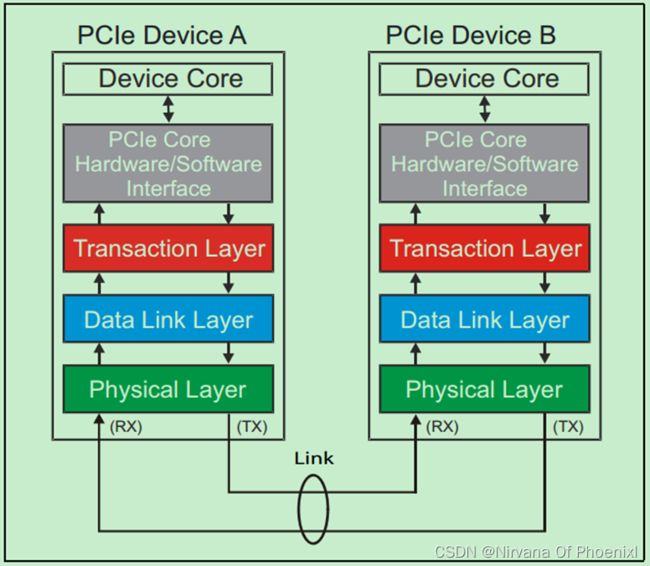

PCIe总线采用了串行连接的方式,并使用数据包(Packet)进行数据传输,采用这种结构有效的去除了在PCI总线中存在的一些边带信号,如INTx等。和很多的串行传输协议一样,在PCIe总线中数据报文在接收和发送过程当中,需要一个完整的PCIe体系结构包括应用层、事务层(Transaction Layer)、数据链路层(Data Link Layer)和物理层(Physical Layer)。

其中,应用层并不是PCIe Spec所规定的内容,完全由用户根据自己的需求进行设计,另外三层都是PCIe Spec明确规范的,并要求设计者严格遵循的。PCIe总线的层次结构如下图所示:PCIe总线的层次结构与网络中的层次结构有类似之处,但是PCIe总线的各个层次都是使用硬件逻辑实现的。在PCIe体系结构中,数据报文首先在设备的核心层(Device Core)中产生,然后在经过该设备的事务层(Transcation Layer)、数据链路层(Data Link Layer)和物理层(Physical Layer),最终发送出去,而接收的数据也需要通过物理层,数据链路层和事务层,最终到达核心层。

一个简化的PCIe总线体系结构如上图所示,其中Device Core and interface to Transaction Layer就是我们常说的应用层或者软件层。这一层决定了PCIe设备的类型和基础功能,可以由硬件(如FPGA)或者软硬件协同实现。

如果该设备为Endpoint,则其最多可拥有8项功能(Function),且每项功能都有一个对应的配置空间(Configuration Space)ID。如果该设备为Switch,则应用层需要实现包路由(Packet Routing)等相关逻辑。如果该设备为Root,则应用层需要实现虚拟的PCIe总线0(Virtual PCIe Bus 0),并代表整个PCIe总线系统与CPU通信ID。

需要注意的是,在PCIe体系结构中,事务层,数据链路层和物理层存在于每一个端口(Port)中,也就是说Switch中必然存在一个以上的这样的结构(包括事务层,数据链路层和物理层的)。一个简化的模型如下图所示:

2.4.1 事务层

事务层可以说是PCIe最为重要的一层,涉及PCIe协议的基本知识是理解PCIe原理最为直接的方式。

事务层定义了PCIe总线使用总线事务,其中多数事务与PCI总线兼容。这些总线事务可以通过Switch等设备传送到其他PCIe设备或者RC。RC也可以通过使用这些总线事务访问PCIe设备。

事务层接收来自PCIe设备核心层的数据,并将其封装为TLP(Transaction Layer Packet)后,发向数据链路层。此外事务层还可以从数据链路中接收数据报文,然后转发之PCIe设备的核心层。

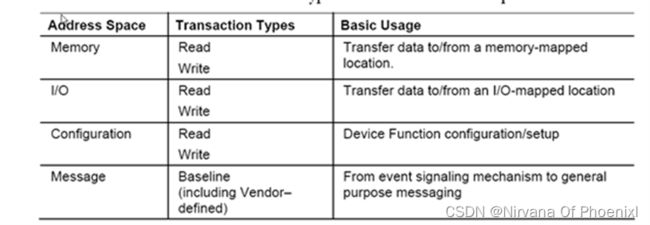

2.4.1.1 事务分类

事务层是PCIe总线层次结构的最高层,该层次将接收PCIe设备核心层的数据请求,并将其转换为PCIe总线事务,PCIe总线使用的这些事务在TLP中定义。PCIe总线继承了PCI总线的大多数事务,如存储器读写、IO读写、配置读写总线事务,并新增了Message消息总线事务等事务。如下表所示

所谓总线事务简单理解就是想让PCIe总线做什么样的事,前文提及的四种类型事务也就是不同的访问类型。

2.4.1.2 事务层应答机制

首先简单地了解一下PCIe总线的通信机制。假设某个设备要对另一个设备进行读取数据的操作,首先这个设备(称之为Requester)需要向另一个设备发送一个Request,然后另一个设备(称之为Completer)通过Completion Packet返回数据或者错误信息。在PCIe Spec中,规定了四种类型的请求(Request):Memory、IO、Configuration和Messages。其中,前三种都是从PCI/PCI-X总线中继承过来的,第四种Messages是PCIe新增加的类型。详细的信息如下表所示:

从表中我们可以发现,只有Memory Write和Message是Posted类型的,其他的都是Non-Posted类型的。

所谓Non-posted,就是Requester发送了一个包含Request的包之后,必须要得到一个包含Completion的包的应答,这次传输才算结束,否则会进行等待。

所谓Posted,就是Requester的请求并不需要Completer通过发送包含Completion的包进行应答,当然也就不需要进行等待了。很显然,Posted类型的操作对总线的利用率(效率)要远高于Non-Posted型。(可将其称为报告类型(no-posted)和非报告类型(posted),非报告类型就是需要应答的,报告类型是不需要应答的)

那么为什么要分为Non-Posted和Posted两种类型呢?对于Memory Writes来说,对效率要求较高,因此采用了Posted的方式。但是这并不意味着Posted类型的操作完全不需要Completer进行应答,Completer仍然可采用另一种应答机制——Ack/Nak的机制(在数据链路层实现的)。

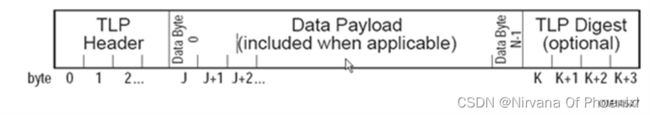

2.4.1.3 TLP数据包格式

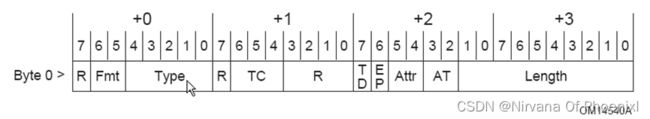

当处理器或者其他PCIe设备访问PCIe设备时,所传递的数据报文首先通过事务层被封装为一个或多个TLP,之后通过PCIe总线的各个层次发送出去。简单来看一下TLP数据包的格式,如下图所示

(1)TLP Header:包头用于对包的管理和控制,Header包包含了对于当前TLP包总线事务类型、路由信息等一系类标志头。

(2)Data Payload:有效数据负载,存放包有效数据信息,其可变最小为0,最大为1024DW。

(3)TLP Digest:32位ECRC

【注】:数据包的类型主要包含三种I/O请求、MEM请求、配置请求,根据类型不同数据包的一些细节内容有些许不同,后面有机会详细解析一下。

2.4.2.4 TLP路由类型

在PCIe总线中,不同的总线事务采用的路由方式也不同。可以分为地址路由、ID路由和隐性路由(间接路由)。其中隐性路由为PCIe新增的。

(1) 地址路由:Mem、IO读写请求(32bit、64bit)

(2) ID路由:配置寄存器,包括一些message包,ID为BDF信息

(3) 隐性路由:message、电源管理等,RC向EP发送广播报文

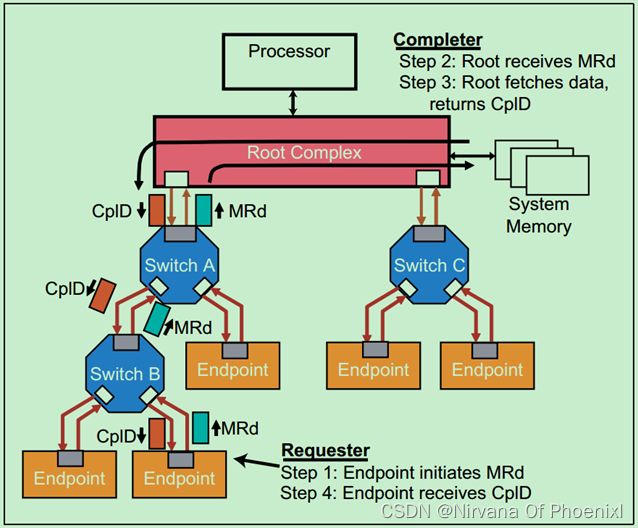

下图显示的是一个Endpoint向System Memory发送读请求(Read Request)的例子。

在这个例子中,Endpoint的读请求通过了两个Switch,然后到达其目标,即Root。Root对读请求的包进行解码后,并从中识别出操作的地址,然后锁存数据,并将数据发送至Endpoint,即包含数据的Completion包,ClpD。需要注意的是,PCIe允许每个包的最大数据量(Max Data Payload)为4KB,但实际上设计者往往会采用较小的Max Payload Size(比如128,256,512,1024和2048)。因此,常常一个读请求会对应多个ClpD,即将大于Max Payload Size的数据分成多个包发送。如果遇到错误,则Root会通过Completion包告知相应的Endpoint。

注:Root向发送请求的Endpoint发送Completion包,是通过Request包中的BDF信息(Bus,Device和Function)进行查找对应的Endpoint的。关于BDF后文系列由详细介绍。

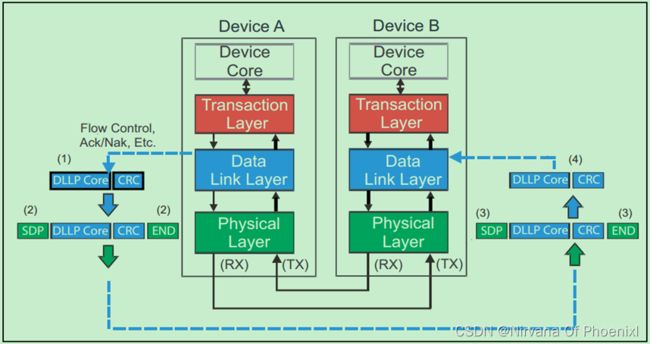

2.4.2 数据链路层

数据链路层保证来自发送端事务层的报文可以可靠、完整的发送到接收端的数据链路层。来自事务层的报文在通过数据链路层时,将被添加Sequence前缀和CRC后缀。数据链路层使用ACK/NAK协议保证报文的可靠传递。PCIe总线的数据链路层还定义的多种DLLP(Data Link Layer Packet),DLLP产生与数据链路层,终止与数据链路层。需要注意TLP与DLLP并不相同,也不是简单的田间前后缀。详解看PCIe协议即可。数据链路层(Data Link Layer)主要进行链路管理(Link Management)、TLP错误检测,Flow Control和Link功耗管理。

数据链路层不仅可以转发来自事务层的包(TLP),还可以直接向另一个相邻设备的数据链路层直接发送DLLP,比如应用于Flow Control和Ack/Nak的DLLP。如下图所示:

数据链路层还实现了一种自动的错误校正功能,即Ack/Nak机制。

2.4.3 物理层

物理层时PCIe总线的最底层,将PCIe设备连接在一起。PCIe总线的物理电气特性决定了PCIe链路只能使用端到端的连接方式。PCIe总线的物理层为PCIe设备间的数据通信提供了传送介质,为数据链路提供可靠的物理环境。物理层时PCIe体系结构最重要也是最难实现的组成部分。PCIe总线的物理层定义了LTSSM(Link Training and Status State Machine)状态机,PCIe链路使用该状态机管理链路状态,并进行链路训练、链路恢复和电源管理。

——————————————————————————————————————

整理不易,还有图自己画的有用、可以参考,有一丢丢帮助支持一下嘻嘻!后面还有会更新。

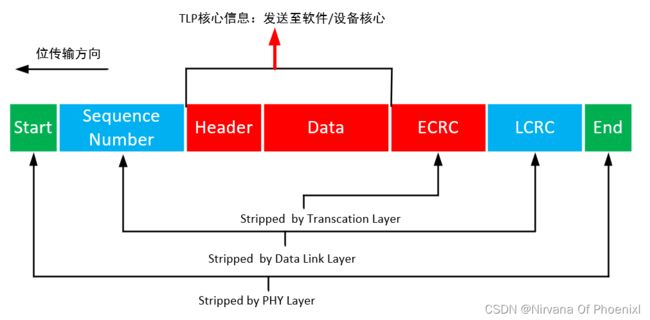

TLP在PCIe数据包的位置解析

(1)发送端:

在进行数据传输的时候,经历总线的三个层次,事务层位于最上层(核心数据信息)、数据链路居中(保证数据传输正确)、物理层次之(物理属性);在不同的层级数据包分别在前后两端附加各层级信息组成新的数据包,并进行发送;一次以低位优先进行数据传输。

(2)接收端

接收端在不同层级,依次剥离对应部分,将数据发送到对应的软件或者核心设备。

点赞收藏加关注,支持一下嘻嘻!

下一篇:PCI Express解析——系列文章【5】:PCIe原理分析之——PCI Express系统模块、PCIe体系结构