计算机里基本硬件的组成以及硬件协同

文章目录

-

- 冯·诺依曼体系

- 输入设备

- 输出设备

- 存储器

- 运算器

- 控制器

- 协同工作的流程

冯·诺依曼体系

世界上第一台通用计算机,ENIAC,于1946年诞生于美国一所大学。

ENIAC研发的前期,需要工作人员根据提前设计好的指令手动接线,以这种方式输入指令给计算机。显然,这种方式程序运行的效率受人工的影响,大部分时间消耗在人工手动接线上面。

ENIAC研发的中期,冯诺依曼加入研发小组。此后,三位大佬(包括冯诺依曼在内)基于对ENIAC的改进,研发了EDVAC机,冯诺依曼在研发EDVAC机时提出了“存储程序”的思想, 奠定了现代计算机的基本结构。

存储程序:将事先编制好的程序和数据送入主存才能执行,一旦程序被启动执行,就无需操作人员的干预,计算机会自动逐条执行指令,直至程序执行结束。

这个时候就不需要人工手动接线输入指令了,从而提升了效率。以这种概念为基础的计算机我们把它叫做冯·诺依曼机。冯·诺依曼体系结构如下图:

其特点

- 采用“存储程序”的方式

- 计算机硬件系统由运算器、控制器、存储器(主、外)、输入设备、输出设备五大部件组成

- 指令和数据以同等地位保存在存储器里,均用二进制表示,计算机可以区分。

- 指令由操作码和地址码组成,操作码指出操作的类型,地址码指出操作数的地址。

输入设备

输入设备的任务:用来接收原始内容,然后把程序和数据转换为计算机能够接受和识别的形式输入计算机。

例如:

- 键盘

- 鼠标

输出设备

输出设备的任务:将计算机内经过计算机处理的结果转换为我们能看懂的形式输出。

例如:

- 显示屏

- 打印机

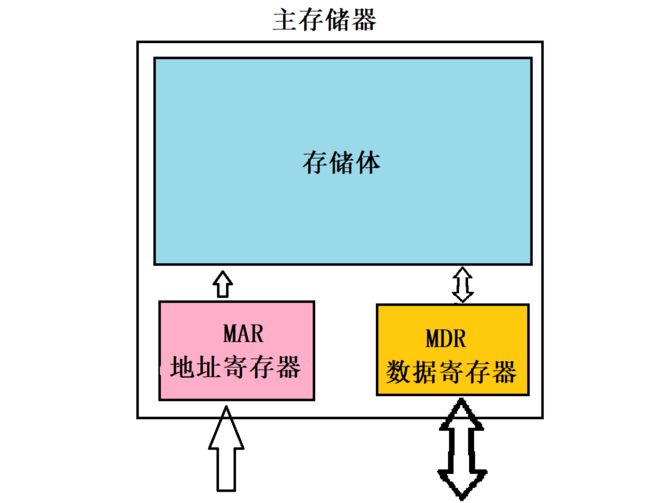

存储器

存储器分为主存储器和辅助存储器,主存储器又可以叫做内存储器,也就是我们平时经常提到的内存。主存储器 + CPU就构成了主机,和我们小时候提到的主机是不一样的。辅助存储器又可以叫做外存储器,磁盘是最常见的外存储器。

主存储器我们可以把它想象成一个非常大的中药柜子 + 取药、放药的柜台

主存储器的存储体 相当于 这个大中药柜子。

存储体由许多存储单元组成,存储单元相当于中药柜子里的一个个小柜子。

存储单元包含若干存储元件,每个存储元件存储一个二进制位。相当于一个小柜子里有若干的空间,每一个空间可以放一个草药(我把它抽象过度了)

一个存储单元里可以放一串二进制代码,这串代码我们呢把它叫做存储字,这串代码的位数为存储字长。存储字长就相当于小柜子里放了多少个草药。存储字长, 一个字只能是1字节,或者1字节的偶数倍。

现在来模拟主存储器的工作方式:

取数据的过程:

- CPU把它需要的数据地址,放到地址寄存器MAR里面。

- 主存储器根据地址寄存器里面的地址,去存储体内找数据

- 主存储器将数据,存入数据寄存器MDR,等待CPU来获取。

存数据的过程

- CPU把要存入的数据,放到数据寄存器MDR里

- CPU把地址(它想把数据放在哪一个位置的地址),放入地址寄存器MAR

- 主存储器根据地址寄存器MAR里的地址,将数据寄存器MDR里的数据放入存储体。

主存储器存取数据的方式,很容易联想到实际例子。

以中医师徒为例,类比主存储器取数据的过程。徒弟负责打杂,例如师傅想要柜子里的草药—党参,师傅就把党参的位置写在纸条上,然后徒弟根据纸条上的位置,去柜子里找,找到了就把党参放在柜台上,等待师傅拿就可以了。

现代计算机,地址寄存器MAR和数据寄存器MDR是放在CPU里面的。

CPU中的运算器和控制器,在"运算器"和"控制器"里并不讲解它们的工作原理,只介绍它们的基本部件,工作原理在“工作流程”中结合进行介绍。

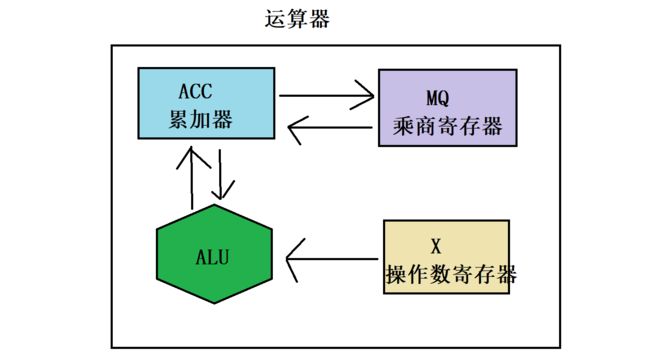

运算器

运算器是用来进行算术运算和逻辑运算的。

算术运算,例如加、减、乘、除

逻辑运算,例如

- 与

- 或

- 非

- 异或

- 移位

运算器的核心是算术逻辑单元,简称ALU。运算器里面有三个寄存器是必须存在的,分别是累加器ACC、乘商寄存器MQ和通用的操作数寄存器X。用于暂时存放操作数和中间结果。

- 累加器ACC。存放操作数和运算结果

- 乘商寄存器MQ。在乘、除运算时,存放操作数和运算结果

- 操作数寄存器X。通用的操作数寄存器,存放操作数和运算结果。

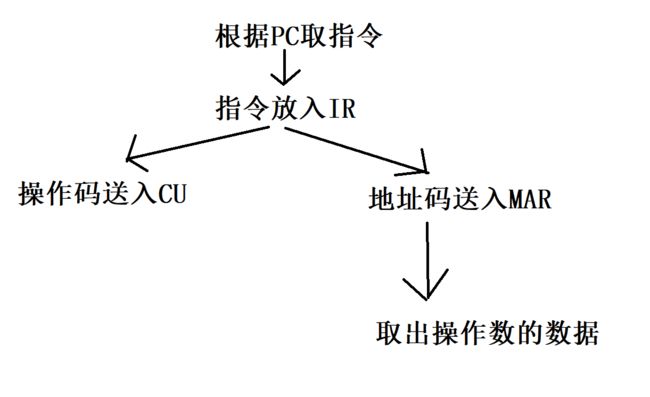

控制器

控制器相当于指挥中心。

程序计数器PC,存放当前想要执行的指令的地址。具备自动加1的功能,当PC里面的指令被取出来以后,PC里放下一条将要执行指令的地址。

指令寄存器IR,当PC把地址放到地址寄存器MAR里,主存储器就把该地址上的指令取出,放到数据寄存器MDR里,指令寄存器IR的内容来自MDR,放的是当前的指令。

指令由操作码和地址码组成,指令寄存器IR里的指令,的操作码,被送入控制单元CU用于分析指令并发出命令;而指令的地址码又被送入地址寄存器MAR里,用于取操作数的数据。

指令和数据在指令周期的不同阶段,所以CPU能够区分指令和数据。

协同工作的流程

#include 上述文件经历预处理、编译、汇编、链接四个大步骤,最终形成一个可执行文件。汇编阶段,汇编器会把程序翻译成机器语言指令,也就是二进制代码。可执行文件里的内容就是由上述步骤转化而来的二进制。

现在以该可执行文件演绎一部分过程。要执行该文件时,先将它的代码和数据加载到内存里面,并且把第一条指令的地址写入程序计数器PC中

第一条指令周期:

(1)(PC)->MAR 。PC程序计数器里的地址通过地址总线,输入到地址寄存器MAR里,主存储器收到CPU发送的读信号

(2)M(MDR)->MDR。从存储体内拿到指令, 放入数据寄存器MDR。此时MDR里的数据为000001 0000000101

(3)MDR->IR。将MDR里的指令通过数据总线给指令寄存器,IR = 000001 0000000101,指令由操作码和地址码组成。

(4)OP(IR)。IR里的指令,的操作码给控制单元CU,CU对操作码分析,得到这是一个取数指令

(5)AD(IR)。IR里的指令,的地址码继续给地址寄存器MAR,(MAR) = 5;

(6)主存储器根据地址码为5,去5地址取出数据,MDR = 0000000000000010 = 2

(7)将MDR里的数据,放入运算器里的累加器ACC = 2

(1)~(3)是取指令,取完指令后,程序计数器PC自动+1,现在PC里面保存的是地址1

(4)分析指令

(5)~(7)执行取数指令。

第二条指令周期:

(1)将程序计数器PC里的指令地址,通过地址总线,送入地址寄存器MAR内, (MAR)= 1

(2)主存储器根据地址找到指令,将指令放到数据寄存器MDR,此时MDR = 000100 0000000110

(3)将MDR里的指令,通过数据总线,送入指令寄存器IR,IR = 000100 0000000110

(4)IR内,指令的操作码送入控制单元CU,CU分析指令,这是 “乘法”指令

(5)IR内,指令的地址码送入地址寄存器MAR,此时(MAR)= 0000000110 = 6

(6)主存储器取出地址为6的数据0000000000000011 ,(MDR) = 0000000000000011 = 3

(7)将数据寄存器MDR里的数据,通过数据总线,送入运算器里的乘商寄存器MQ里, 此时(MQ) = 0000000000000011 = 3

(8)累加器ACC里的数据放入通用的操作数寄存器X里面。此时(x) = 2

(9)由算术逻辑单元ALU执行乘法运算,得到6,放入累加器ACC里面,此时(ACC)=6,如果乘积太大,就需要乘商寄存器MQ来辅助。

第三条指令周期:

…

…

…

综上,CPU工作的流程就是:取指令 ===>> 分析指令 ===>>执行指令。这种方式叫做流水线。还有一种机制比流水线要好得多,叫做超标量CPU。你可以这样理解,就是设计了一种机制,使得CPU的工作“超标量”了,把超标量理解为生活上的超标量就行。那么这种让CPU超标量的机制是如何的呢?

这种设计中,多了一个保持缓冲区。把多个指令同时取出并进行解码,放入保持缓冲区内,如果执行单元有“在偷懒的”(保持缓冲区内还有可处理的指令,但是执行单元有空闲),就从保持缓冲区取出并且执行。缺点在于:从保持缓冲区取出的指令,极大可能不按原来的顺序执行,这个应该比较好理解。