9.16~9.17数电

偶校验码生成器

?为什么需要校验?

接收端要判断信息的准确性

码距

码距是指合法码字之间的最小距离,表示是从一种合法状态转变为另一种合法状态所需要改变的最少字节数

码距越大越不容易发生错误,如码距为2时,表示至少发生两次位错误才有可能从一个合法状态转变为另一种合法状态导致检测不出来,如果只发生了一位,那么必定是从合法状态转变为了冗余状态,就一定可以被检测出来

发生错误就是因为一个合法码字发生了位错误,转变到了另一个合法码字,导致无法检测出来

合法码字就是正确,如果是冗余码字就说明传输发生了错误

检验码就是在原码的基础上通过某种规则,使合法码字间的码距增大,从而可以避免传输中产生的错误

?什么是检验码?

检验码:检验位+信息位

奇检验:信息位有奇数个1,则检验码为0,不然,则为1

偶检验:有偶数个1,则检验为0,不然,则为1

?这俩有啥区别,为什么要区分出来?

采用奇校验:如果原数据有奇数个1,就加0;有偶数个1,就加1;

然后给一串数据后,采用与记录相同的检验方式

就是两种对偶策略,等效

是说就是两种方式吗?还是说奇数位时用奇检验,偶数位时用偶检验?

奇检验码进行同或,偶 ~异或

p=1,出错;p=0,正常

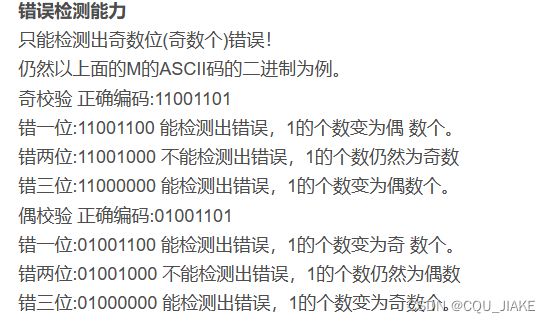

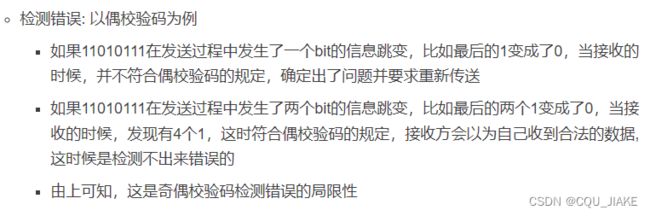

只能查奇数个错误,即原序列1的数量有奇数位(极限就是字节长度,1,3……n)是检查不出来错误,但是如果其间隔有0,有偶数位时,就检测不出来

1位错了,就说明1变成了0或者0变成了1,最后结果就是1的数量发生了变化,奇偶类型发生了变化

N字节长的数据,共有2^n种情况,其中1的数量

1的数量为奇数

只采用4个状态为合法状态,剩下4个为冗余的非法状态

说的是算上校验位后的1的总数,奇检验码要保证1的个数(算上了校验位)总为奇数

偶检验码要保证1的个数总为偶数,

即采用这种编码后,码字中1的必为奇数或偶数(即1的个数为奇数(或偶数)时才为合法状态,另一种时就是冗余的非法状态),如果不是就说明发生了错误,所以可以检测传输中码字的1的个数来确定

所以对于奇校验码,原码为奇数时就不需要加1(已经是奇数了,再加1就成偶数了),偶校验码需要补1(补个1使其从奇数个1转变为偶数个1);为偶数时,奇校验码要加1,偶检验码加0;

偶数个1异或出来的值是0,奇数个1异或出来的值是1

检验时就是让码字各位进行异或,采用偶检验码(要保证1的个数为偶数)时,如果异或出来的值是1(说明1的个数是奇数),则为非法状态,出现了错误;不然,则为合法状态。奇检验码时相反。

输入引脚数:

?什么是引脚?

传输数据为4位,数据交换按半字节

?数据交换是什么意思?

?半字节交换怎么进行?

8位二进制数为字节,4位2进制数为

`timescale 1ns/1ns

module odd_sel(

input [31:0] bus,

input sel,//sel是控制标识,为1时采用鸡校验,为0时采用偶校验

output check

);//31位原码,

//*************code***********//

wire odd;

assign odd =^bus;//获取原码的1的个数,为1则说明有奇数个1,为0则有偶数个

assign check =sel?odd:~odd;//如果sel是0,则采用偶校验,odd为1时,有奇数个1,是错误的,要返回0,odd为0时返回1

//sel为1时,采用鸡校验,如果odd为1,则说明是正确的,返回1,不然则为0,返回0表错误

//*************code***********//

endmodule半字节

题意就是说给定一个4位的数,来生成一个5位的偶检验码

module top_module(

input[4:0]a, b, c, d, e, f,

output[7:0]w, x, y, z

);

wire[31:0]data;

assign{w,x,y,z}={a,b,c,d,e,f,2'b11};

//信号合并,直接{}连接`timescale 1ns/1ns

module odd_sel(

input [3:0] bus,

output [4:0] fina

);

wire even;

assign even =^bus;//如果是奇数个1,则even为1,直接加在前面就可使数据的1的个数为偶数,如果是偶数个1,则even为0,直接加在前面可保持1的个数不变

assign fina={even, bus};

endmodule命令启停器

移动,注入I,停止S,点火ON,关火OF

前进F后退B,

网关命令有效

?什么是网关命令?

选择器

根据输入信号选择一个信号进行输出

在选择输入的控制下,将n个数据输入中的一个转接到单一的数据输出端

译码器

产生了对应于所需函数的每一个最小项的离散输出信号

多路分配器

译码器就是把存储时用的压缩码字转换为原始的码字(独热码,位数里只有一位是1,其他都是0)

如3-8译码器,就是将3位的编码转化为8位的独热码(3指输入的位数,8指输出的位数,可以把3看成2^3,即将1的位置转化为二进制)(代码转换器)

编码器就是将原始的码字通过某种方式进行编码与压缩,转化为位数更小的编码

格雷码

格雷码是原编码的另一种表现形式,即保留一个相同的一项,然后以此项为基础,向其他位做异或处理,最后可以再由异或推回去

竖线平的表示积,与,弯的表示和,或

二选一多路选择器:

不要看图形符号,图形符号只是表示这个器件是啥,干啥用的,长什么样子不重要

重要的是输入的信号与输出的信号(即接入接出的线)

输入信号里有shift,0,w3,输出y3

shift是选择输入信号,0,w3是输入信号,选择输入信号对0,w3进行选择,从而决定y3最终为这两者中的哪一个

四选一多路选择器:

输入信号:w3,w0,w2,w1

选择输入信号:s1,s0

输出信号:y3

采用译码器构建的4选1多路选择器:

采用译码器就不是从w(即4个输入信号)里选了,而是把2位码(表示1出现的位数,有0,1,2,3)转为4位的独热码(000,100,010,001),然后把独热码的各位(共4位)与4位w做与的操作,再拼在一起,从而完成选择

2个码信号拼在一起表示独热出现的位置00为000,01为100,10为010,11为001

输出信号的情况总数取决于拼接在一起的码的长度(即由1出现的最远位置(即最后一个字节,即原码长度对2取对数)决定)

4个输入信号(w0~w3),

输入选择信号:s0,s1

module mux4to1(w, s, f);

input[0:3]w;

input[1:0]s;

output f;

wire[0:3]y;

dec2to4 decoder(s, 1, y);

assign f = | (w & t);

endmodule

module dec2to4(w, en, y);

input[1:0]w;

input en;

output reg[0:3]y;

always@(w, en)

case({ en,w })

3'b100:y=4'b1000;

3'b101:y=4'b0100;

3'b110:y=4'b0010;

3'b111:y=4'b0001;

default:y=4'b0000;

endcase

endmodule一个时钟信号控制的时序电路称为同步时序电路

多个~为异步