Clock Domain Crossing Design & Verification Techniques Using System Verilog 学习

重要的设计考虑因素要求仔细构建多时钟设计时钟域交叉 (CDC) 边界。 本文详细介绍了一些最新策略和解决跨 CDC 边界传递一个或多个信号的最佳已知方法。论文中包含与 CDC 验证相关的技术和一个有趣的 2 深 FIFO用于在时钟域之间传递多个控制信号的设计。 虽然设计方法论文中描述的一般可以使用任何 HDL 来实现,示例如下使用高效的 SystemVerilog 技术。

亚稳态 p6

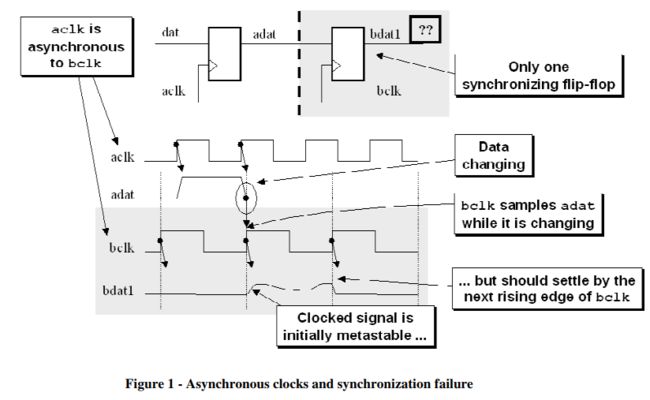

亚稳态是指在一段时间内不呈现稳定 0 或 1 状态的信号设计正常运行期间的某个点。 在多时钟设计中,亚稳态不能可以避免,但亚稳态的有害影响可以被抵消。

** 寄存器在进行保存数据的时候存在 建立时间 与 保持时间,如果没有满足建立时间与保存时间,数据发生改变,则可能出现亚稳态的现象**

为什么亚稳态是一个问题?

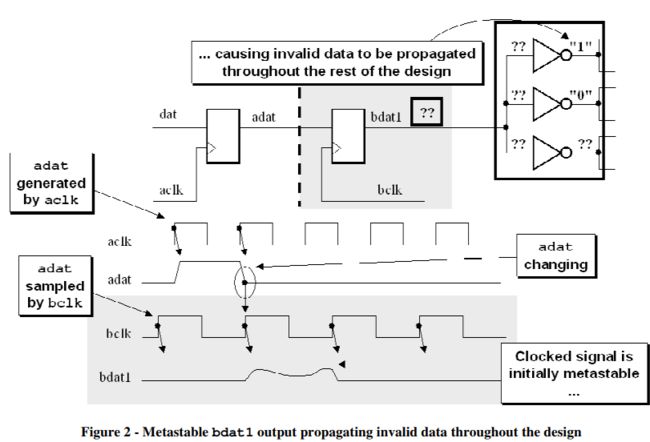

那么为什么亚稳态是一个问题呢? 图 2 显示了遍历的亚稳态输出接收时钟域中的附加逻辑可能导致传播非法信号值贯穿设计的其余部分。 由于 CDC 信号可能会在一段时间内波动,因此接收时钟域中的输入逻辑可能会识别波动信号的逻辑电平为不同的值,因此将错误信号传播到接收时钟域。

任何设计中使用的每个触发器都有指定的建立和保持时间,或者法律上不允许数据输入在时钟上升沿之前和之后更改的时间。 该时间窗口被指定为设计参数,精确地防止数据信号变化太接近另一个同步信号,从而导致输出进入亚稳态。

同步器(Synchronizers)

在时钟域之间传递信号时,要问的一个重要问题是,我需要对从一个时钟域传递到另一个时钟域的信号的每个值进行采样?

3.1 Two synchronization scenarios

跨越 CDC 边界传递信号时可能出现两种情况,确定哪种场景适用于您的设计很重要:

- 允许丢失在时钟域之间传递的样本。

- 时钟域之间传递的每个信号都必须被采样

第一种情况

有时不需要对每个值进行采样,但重要的是采样值准确。 一个例子是标准中使用的一组格雷码计数器异步FIFO设计。 在正确设计的异步FIFO 模型中,同步格雷码计数器不需要捕获来自相反时钟域的每个合法值,但它是采样值必须准确,以识别满载和空载情况,这一点至关重要发生。

第二种情况:

CDC信号必须被正确识别或识别并确认在 CDC 信号允许更改之前。

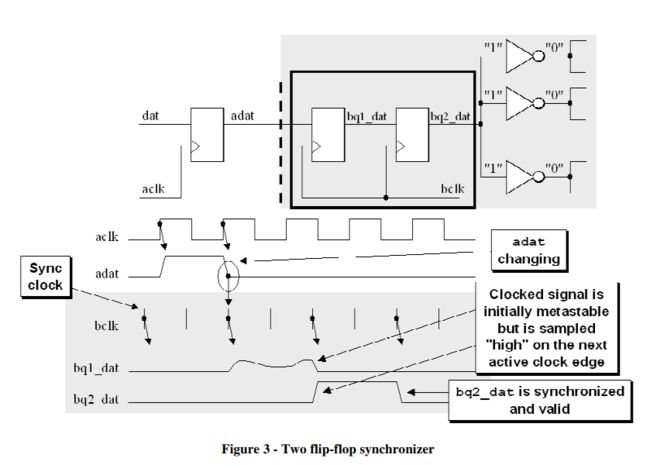

3.2 打两拍(Two flip-flop synchronizer )

第一个触发器将异步输入信号采样到新的时钟域并等待一个完整的时钟周期,以允许第一级输出信号上的任何亚稳态衰减,然后第一级 1 个信号由同一时钟采样到第二级触发器,其预期目标是第二阶段信号现在是一个稳定且有效的信号,已同步并准备好在新的时钟域。

在经过了两级Flip-flop synchronizer之后数据出现亚稳态的概率会大大的降低理论上,第一阶段信号在信号被计时进入第二级,使第二级输出信号也进入亚稳态。同步失败之间的时间(MTBF)的概率的计算是多个变量的函数,包括用于生成输入信号的时钟频率并对同步触发器进行计时。 可以找到 MTBF 计算的一种描述达利和波尔顿[9]。

对于大多数同步应用,两个触发器同步器足以消除所有同步可能的亚稳态。

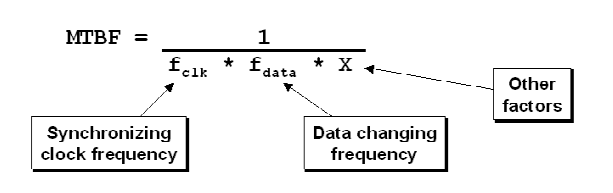

3.3 MTBF - mean time before failure

对于大多数应用程序,计算平均故障前时间非常重要(MTBF) 对于任何跨越 CDC 边界的信号。 从这个意义上说,失败意味着一个信号传递到同步触发器,在第一级同步器触发器上进入亚稳态,并且当采样到第二级同步器时,一个周期后继续亚稳态拖鞋。 由于信号在一个时钟周期后没有稳定到已知值,因此信号可能当采样并传递到接收时钟域时仍然处于亚稳态,从而导致潜在的相应的逻辑失败。

执行以计算同步器电路的 MTBF。 无需重复方程分析中,需要指出的是,有两个最重要的因素直接影响同步器电路的** MTBF 是采样时钟频率(信号传输的速度有多快)采样到接收时钟域)和数据变化频率(数据变化的速度有多快)**跨越 CDC 边界的更改)

所以,采样频率越快,数据的变化频率越快则出现MTBF的概率越大

3.4 Three flip-flop synchronizer

对于一些非常高速的设计,双稳态同步器的 MTBF 太短,而第三个同步器的 MTBF 太短。添加触发器可将 MTBF 增加到令人满意的持续时间。 当然满意的是由设计确定。

3.5 同步发送时钟域信号 (Synchronizing signals from the sending clock domain )

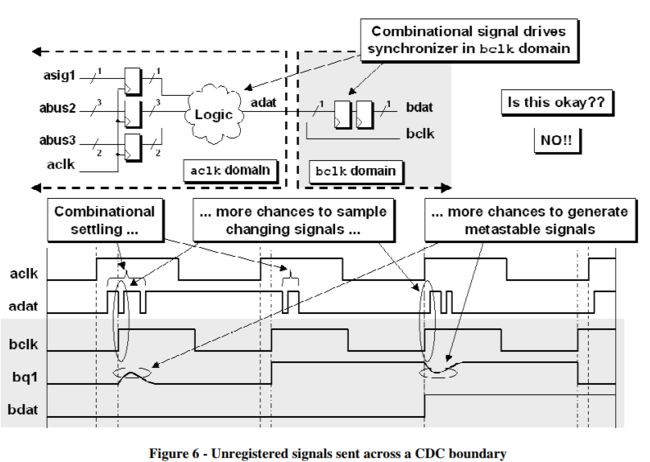

有关 CDC 设计的常见问题:在将信号传递到接收时钟域之前发送时钟域寄存来自的信号是个好主意吗? 隐含于问题是假设 CDC 信号将同步到接收时钟领域; 因此,它们不需要发送时钟域中的同步。 这合理化是不正确的,在发送时钟域中注册信号通常应该需要。(在发射之前,是否需要在发射时钟域打一拍信号将之在发射始终与同步,答案:需要)

在此示例中,发送时钟域的组合输出可能会经历CDC 边界处的组合沉降。 这种组合沉降有效地增加了数据更改频率可能会产生小量的振荡数据,从而增加改变时可以采样的边数,相应增加采样变化数据和生成亚稳态信号的潜力。

3.6 Synchronizing signals into the receiving clock domain

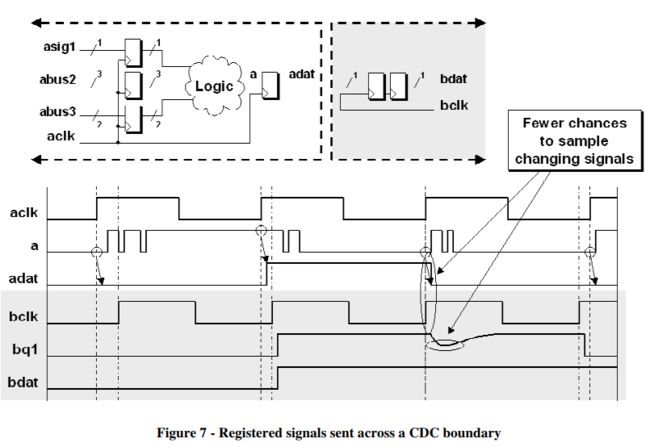

发送时钟域中的信号在传递到 CDC 之前应进行同步边界。 来自发送时钟域的信号的同步减少了可以在接收时钟域采样边沿,有效减少数据变化MTBF 方程中的频率,从而增加计算出的故障之间的时间(参见第 3.3 节描述了数据更改频率对 MTBF 的影响)(总结:在发送时钟前对数据进行打拍能够有效的减少数据的改变频率,从而增大MTBF)

在图 7 中,aclk 逻辑在传入 ADAT 触发器之前进行稳定和设置。bclk 域。 adat 触发器滤除触发器输入上的组合稳定 (a)并将干净的信号传递给 bclk 逻辑。

4.0 将快时钟域信号同步到慢时钟域(Synchronizing fast signals into slow clock domains )

正如 3.1 节中讨论的,如果 CDC 信号在时钟之间传递时不能被跳过当穿过时钟域时,重要的是要考虑信号宽度或同步技术。** **

与同步器相关的一个问题是来自发送时钟的信号可能会被域在采样之前可能会更改值两次,或者可能太接近较慢时钟域的采样边沿。 任何时间信号都必须考虑这种可能性从一个时钟域发送到另一个时钟域,必须确定是否丢失信号对于相关设计来说是或不是问题**(数据丢失)**

当不允许丢失样本时,有两种解决该问题的通用方法:

- 开环解决方案可确保无需确认即可捕获信号。(不带反馈)

- 一种闭环解决方案,需要确认接收到穿过网络的信号CDC边界** (带反馈)**

4.1 时钟域间信号可靠传递的要求(Requirement for reliable signal passing between clock domains )

将较慢的控制信号同步到较快的时钟域通常不是问题,如果较快的时钟域是较慢的时钟域频率的 1.5 倍(或更多),因为较快的时钟域的频率是较慢的时钟域的频率(或更多)。时钟信号将对较慢的 CDC 信号进行一次或多次采样。 认识到抽样与更快的采样相比,较慢的信号进入较快的时钟域导致的潜在问题更少信号进入较慢的时钟域,设计人员可以通过使用简单的方法来利用这一事实两个触发器同步器在时钟域之间传递单个 CDC 信号。**(慢时钟与到快时钟域很简单,快到慢需要进行处理)**

4.1.1 “三个时钟沿”要求 (The “three edge” requirement )

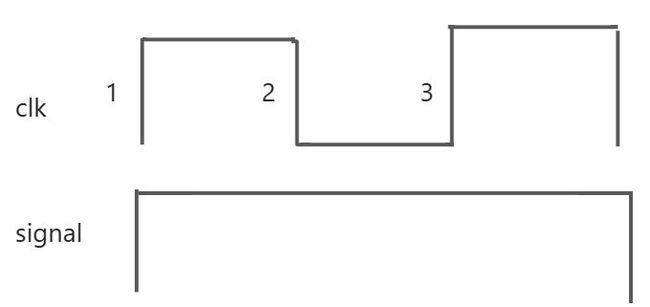

Mark Litterick[4] 指出,当通过一个时钟域在时钟域之间传递一个 CDC 信号时,双触发器同步器,CDC信号必须宽于1-1/2倍的周期宽度接收域时钟周期。 Littereick 将此要求描述为“输入数据值必须对于三个目标时钟边沿保持稳定。

个人理解:无论如何能够经过一个上升沿并且稳定的上升沿。

对于比较长的信号源与目的时钟频率,这个要求能够被放宽到1 - 1/4 倍的接收时钟域的时钟周期,但是利用“三边沿”法则能够更加的稳定,利用Systemverilog更容易验证相比于1/4

“三边”要求实际上适用于开环和闭环解决方案,但是闭环解决方案的实现自动确保至少三个边缘

检测到所有 CDC 信号。

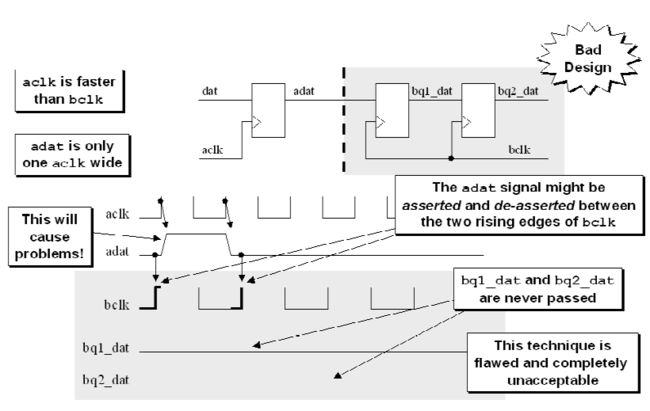

4.2 问题 - 通过快速 CDC 脉冲(Problem - passing a fast CDC pulse )

考虑发送时钟域具有较高频率的严重缺陷情况比接收时钟域宽,并且 CDC 脉冲在发送时钟域中只有一个周期宽领域。 如果 CDC 信号仅在一个快速时钟周期内产生脉冲,则 CDC 信号可能会变高

和较慢时钟的上升沿之间的低电平,并且不会被捕获到较慢的时钟中域如图8所示。

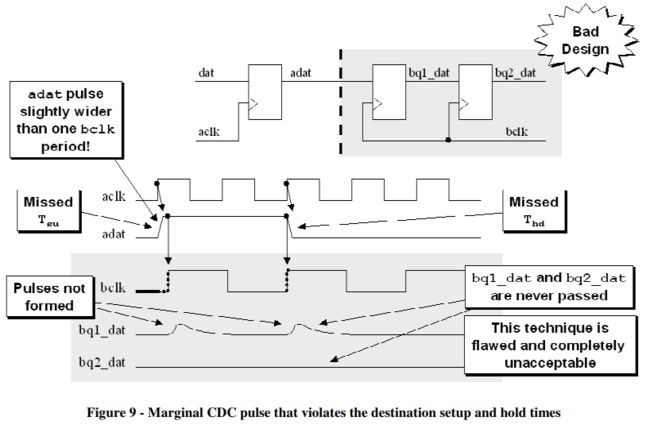

4.3 问题 - 对长 CDC 脉冲进行采样 - 但不够长!(sampling a long CDC pulse - but not long enough! )

考虑有些不直观且有缺陷的情况,其中发送时钟域向接收时钟域发送一个比接收周期稍宽的脉冲时钟频率。 大多数情况下,信号都会被采样并通过,但是有CDC 脉冲变化太接近两个时钟上升沿的可能性虽小但确实存在接收时钟域,从而违反第一个时钟沿的建立时间并违反第二个时钟边沿的保持时间并没有形成预期的脉冲。 这种可能的失败是如图 9 所示:

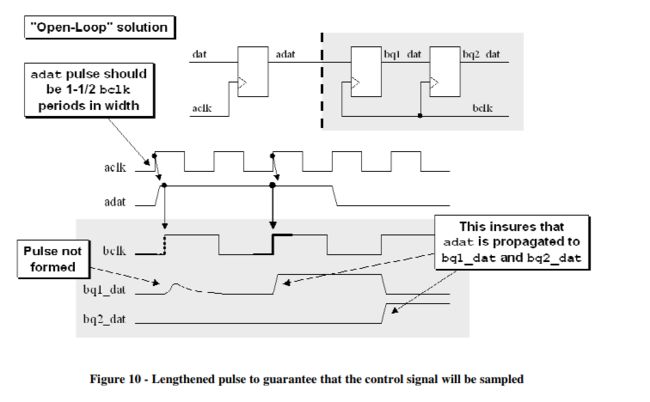

4.4 开环解决方案 - 使用同步器采样信号(将信号拓展到三边沿)

此问题的一个潜在解决方案是在超过一段时间内断言 CDC 信号采样时钟的周期时间如图 10 所示。如第 4.1.1 节所述,最小脉冲宽度为接收时钟频率周期的 1.5 倍。 假设是CDC 信号将被接收器时钟至少采样一次,也可能采样两次。当相对时钟频率固定并且适当时,可以使用开环采样分析了。

优点:开环解决方案是跨 CDC 边界传递信号的最快方式,不需要确认接收到的信号。

缺点:与开环解决方案相关的最大潜在问题是另一个工程师可能会将该解决方案误认为是通用解决方案或设计要求可能会发生变化,工程师可能无法重新分析原始的开环解决方案。 这通过向模型添加 SystemVerilog 断言来检测是否输入脉冲永远无法超过“三个边沿”设计要求。

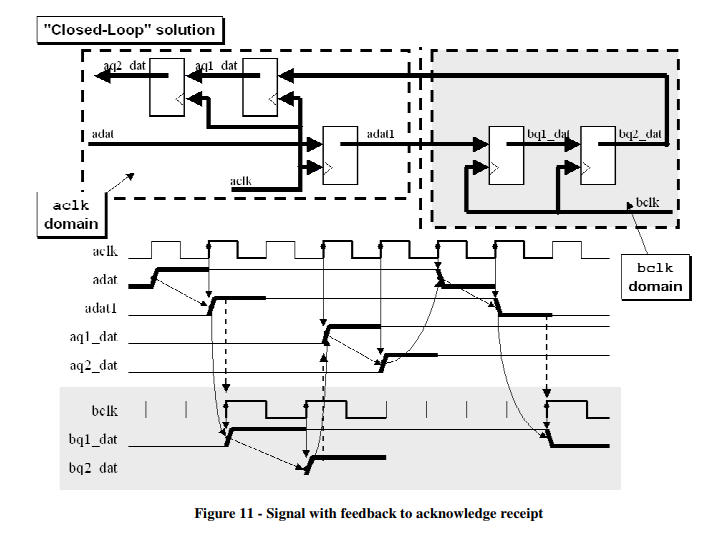

4.5闭环解决方案-同步信号采样

该问题的第二个潜在解决方案是发送使能控制信号,使其同步进入新的时钟域,然后将同步信号通过另一个时钟域传回同步器发送时钟域作为确认信号。

**优点:**同步反馈信号是一种非常安全的技术,可以确认第一个控制信号被识别并采样到新的时钟域中。

**缺点:**同步控制可能存在相当大的延迟在允许控制信号改变之前,在两个方向上发出信号。

5.0 Passing multiple signals between clock domains (在时钟域之间传递多个信号)

当在时钟域之间传递多个信号时,简单的同步器不能保证数据的安全传送

工程师在进行多时钟设计时常犯的一个错误是将同一事务中所需的多个 CDC 位从一个时钟域传递到另一个时钟域,而忽视了 CDC 位同步采样的重要性。

问题是同步到一个时钟的多个信号会经历小偶尔可以在一秒内的不同时钟上升沿上采样的数据变化偏差时钟域。 即使我们可以完美地控制和匹配多个走线长度信号、上升和下降时间的差异以及芯片上的工艺变化可能引入足够的偏差,导致在其他仔细匹配的迹线上采样失败。(多bit信号会出现不同bits skew不同的情况)

必须采用多位 CDC 策略以避免多位值的倾斜采样

5.1 Multi-bit CDC strategies

为了避免多位 CDC 倾斜采样场景,我将多位 CDC 策略分为三大类:

(1)多位信号合并。 如果可能,将多个 CDC 位合并为 1 位 CDC信号。

(2)多循环路径制定。 使用同步负载信号安全地通过多个 CDC位。

(3)使用格雷码传递多个CDC位。

本节其余部分详细介绍了每种策略

5.2 Multi-bit signal consolidation

如果可能,将多个 CDC 信号合并为 1 位 CDC 信号。 问自己问题,我真的需要多个位来控制跨 CDC 边界的逻辑吗?

简单地在所有 CDC 位上使用同步器并不总是足够好,如以下示例所示。如果控制信号的顺序或对齐很重要,则必须注意将信号正确传递到新的时钟域。 本节中显示的所有示例都过于虽然很简单,但它们非常模仿实际设计中经常出现的情况。

5.3 两个同时需要的控制信号。Two simultaneously required control signals.

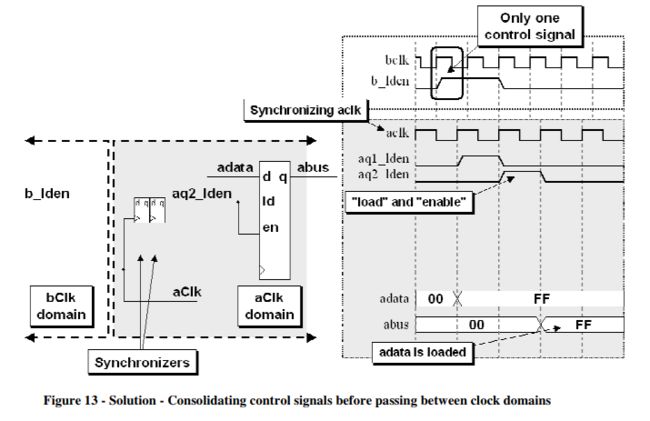

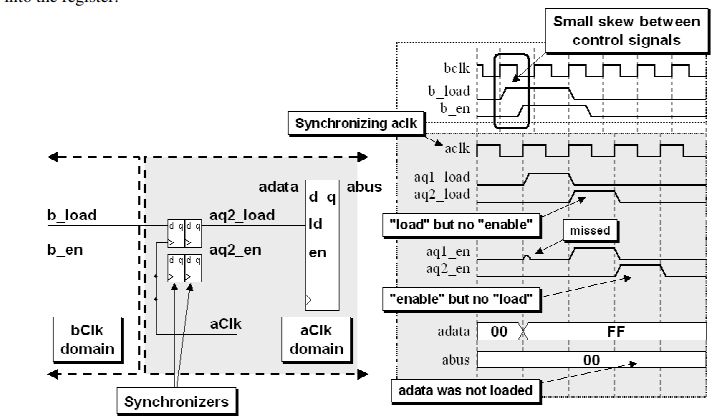

在图 12 所示的简单示例中,接收时钟域中的寄存器需要加载信号和使能信号,以便将数据值加载到寄存器中。 如果两个负载和使能信号在同一发送时钟沿上驱动,有可能出现小偏差控制信号之间可能会导致两个信号同步到不同的时钟接收时钟域内的周期。 在这种情况下,数据将不会被加载到寄存器中。

5.3 Solution-Consolidation

解决5.3节中的问题很简单,合并控制信号即可。 如图所示图 13,在接收时钟域中驱动负载和使能寄存器输入信号仅来自一个负载使能信号。 合并将消除两个控制信号的潜力到达的时间发生了变化。

5.4 Problem - Two phase-shifted sequencing control signals

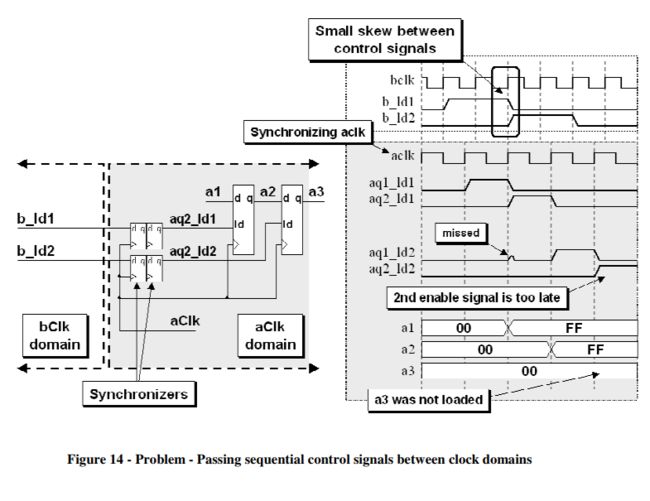

图 14 中的图表显示了顺序驱动的两个使能信号 aen1 和 aen2从发送时钟域进入接收时钟域以控制使能输入流水线数据寄存器。 问题在于,在第一个时钟域中,aen1控制信号可能会在 aen2 控制信号生成之前稍微终止,并且接收时钟可能出现在 aen1 和 aen2 控制信号脉冲之间的微小间隙中,导致在接收时钟域的使能控制信号链中形成单周期间隙。这将导致第二个寄存器丢失 a2 数据值。

问题描述:当相位相差180°的信号被采样时,可能存在skew,满足三边沿条件下。可能出现信号错位的情况,从而出现问题

Soulution consolidation and an extra flip-flop

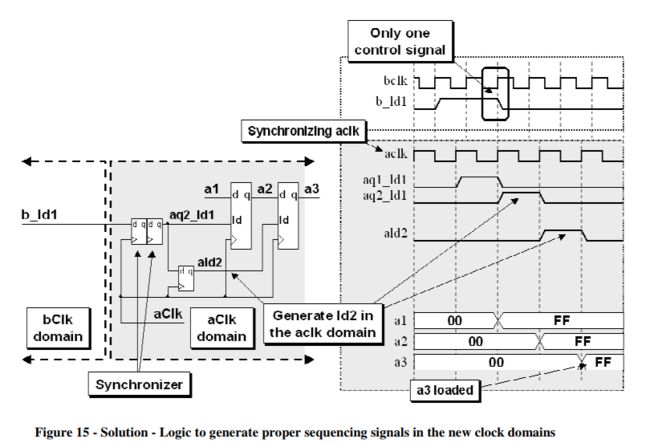

该问题的解决方案,如图 15 所示,是只发送一个控制信号到接收时钟域并生成第二相移流水线使能信号接收时钟域。(通过将两个信号合并,引入一个新的flip-flop实现相同的功能)

5.5 Problem - Multiple CDC signals

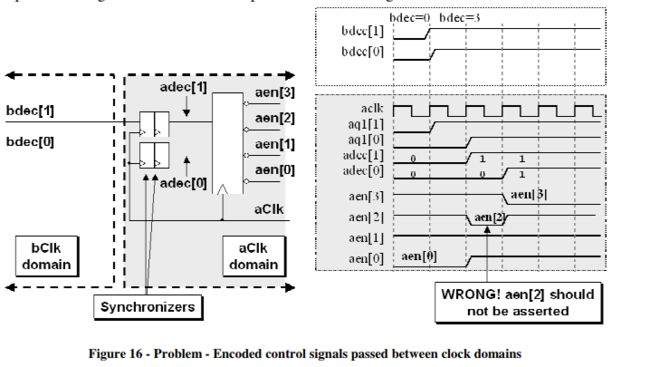

图 16 中的图表显示了在时钟域之间传递的两个编码控制信号。 如果两个编码信号在采样时略有偏差,则在接收时钟域中的一个时钟周期内可能会生成错误的解码输出。

因为bdec[1] 与 bdec[0] 信号会出现skew,所以当进行打拍后会错开一个时钟周期,那么编码会出现错误

Solutions for passing multiple CDC signals 解决方法

多循环路径 (MCP) 公式和 FIFO 技术可用于解决问题与传递多个 CDC 信号相关。 MCP 配方的描述和定义是第 5.6 节给出

至少有两种多循环路径(MCP)公式可以用来解决这个问题:

(1)闭环-带反馈的MCP公式。

(2)闭环-MCP制定,具有确认反馈。

MCP 制定实施技术将在下一节开始描述。至少还有两种 FIFO 策略可以作为该问题的闭环解决方案:

(1) 异步FIFO实现。

(2)** 2-deep FIFO 实现。埋坑**

FIFO 实现技术从第 5.8 节开始描述。

5.7.5 格雷码技术风格1

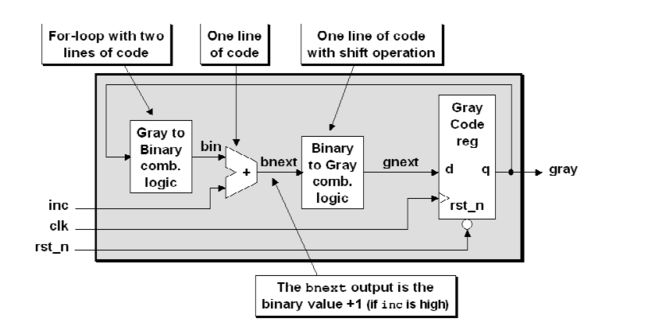

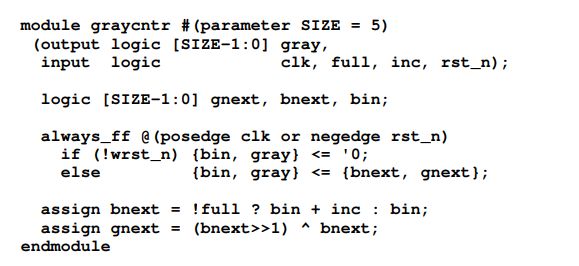

我们可以使用第 5.7.3 节和第 5.7.3 节中所示的转换来构建格雷码计数器5.7.4. 对于任何格雷码计数器,重要的是要记住格雷输出必须是注册以消除设计中的任何组合沉降。

格雷码计数器样式 #1 的 SystemVerilog 代码包含一个格雷码到二进制转换器、一个二进制到灰度转换器并在转换之间递增二进制值,如下所示图 27.

将多位的地址计数信号转化为是否需要自增一位

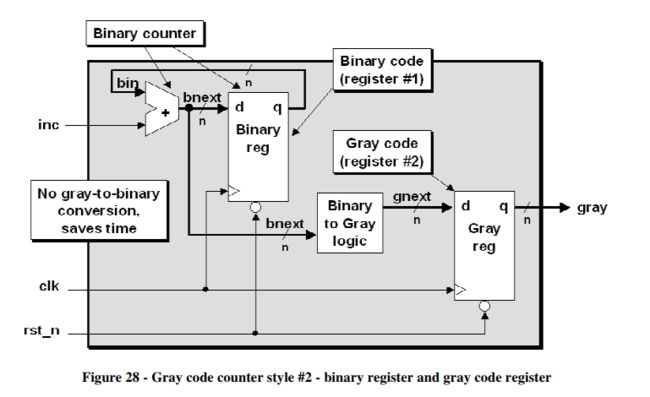

5.7.6 格雷码计数风格2

我们可以仅使用 5.7.4 节中所示的二进制到格雷码转换来构建第二种类型的格雷码计数器。 这个格雷码计数器实际上既是一个二进制计数寄存器,又是一个格雷码计数寄存器。

5.8 额外的多bitCDC技术

除了前面几节中描述的 MCP 制定技术之外,我还发现许多工程师使用标准 FIFO 在时钟域之间传递数据和控制信号。

至少有两种有趣的 FIFO 实现策略可用于解决多位 CDC 信号完整性问题:

(1) 异步FIFO实现。

(2) 2-deep FIFO 实现。