【Xilinx】Spartan 7上手指南(ARTY S7开发板)

Spartan 7上手指南

- 一、安装board文件

-

- 1. 下载并解压板卡压缩文件

- 2. 复制到Vivado安装目录

- 二、demo工程

-

- 1. 下载demo

- 2. 修改tcl

- 3. 恢复工程

- 4.生成bit

- 三、调试运行

-

- 1. 连接电脑

- 2. 设置串口

- 3. 烧写bit

-

- 1) 打开Open Hardware Manager

- 2) 点Open Target

- 3) 点Auto Connect

- 4) 右键点击xc7s50_0

- 5) 点Program Device

- 6) 点Program

- 4. 运行效果

今天拿到一块ARTY S7开发板,主芯片是xc7s50csga324。

大小非常的小巧,但是该有的资源一点也不少

开发环境:

官网上用的是2017,我没有这么老的版本,用了Vivado2019.2

安装路径是C:\Xilinx\Vivado\2019.2

有些版本上的细节调整,后面会讲到。

一、安装board文件

1. 下载并解压板卡压缩文件

默认情况下,Vivado选择board时是没有这个板子的型号的,需要从网上下载

打开链接

https://github.com/Digilent/vivado-boards

下载压缩包并解压

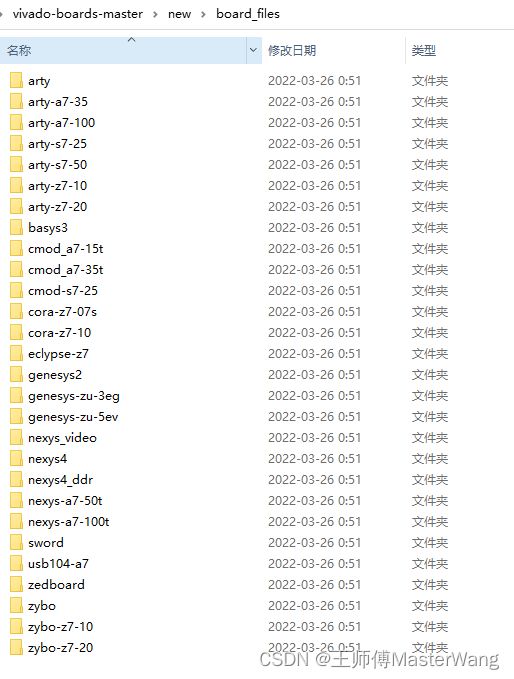

压缩包里new是2015.x及以上版本,old适用于2014.4及以下版本

我用的是2019.2,所以选用new文件夹的文件

2. 复制到Vivado安装目录

把这些文件夹复制到vivado安装目录下的data\boards\board_files目录,然后重启vivado

C:\Xilinx\Vivado\2019.2\data\boards\board_files

重新打开Vivado后新建工程,可以看到有了Arty S7-50这个开发板型号

二、demo工程

参考链接

https://digilent.com/reference/learn/programmable-logic/tutorials/github-demos/start

1. 下载demo

打开链接

https://digilent.com/reference/programmable-logic/arty-s7/start

点击这个链接打开新页面

可以看到提供了7s25和7s50的工程,我的开发板是50,所以选了S7-50的zip包

最后下载的文件如下图

![]()

我把它解压放到了

D:\debug\192\S7Arty\Arty-S7-50-GPIO

2. 修改tcl

这里有个小问题需要注意,网上下载的board是digilentinc.com:arty-s7-50:part0:1.1

工程里面用的是1.0,直接使用会提示board_part没定义

ERROR: [Board 49-71] The board_part definition was not found for digilentinc.com:arty-s7-50:part0:1.0. The project's board_part property was not set, but the project's part property was set to xc7s50csga324-1. Valid board_part values can be retrieved with the 'get_board_parts' Tcl command. Check if board.repoPaths parameter is set and the board_part is installed from the tcl app store.

所以需要打开proj/create_project.tcl

把这里1.0修改成1.1就可以解决这个问题

3. 恢复工程

一般情况网上提供的Vivado工程,并不是直接提供的Vivado工程压缩包,而是一个恢复重建的tcl文件

打开Vivado,不要创建工程也不要打开工程,以下步骤直接在最底下的Tcl Console进行操作

我的路径是D:\debug\192\S7Arty\Arty-S7-50-GPIO

注意Vivado里面需要把 \ 改成 /, Vivado里面 \ 是转义符

先进入proj目录

cd D:/debug/192/S7Arty/Arty-S7-50-GPIO/proj

然后执行

source create_project.tcl

等待一会,工程就会自动创建完成。

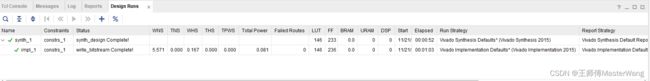

4.生成bit

点击Generate Bitstream,如果没有错误的话,等待几分钟就会成功生成bit

三、调试运行

1. 连接电脑

用micro usb连接电脑,效果如图

这个usb同时起到仿真器、串口、供电三种功能,不需要另外外接电源

2. 设置串口

打开串口,默认参数为9600, 8, n, 1

3. 烧写bit

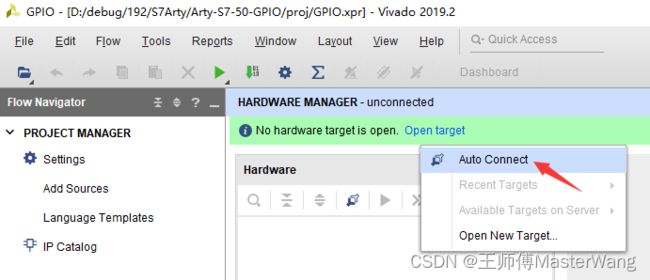

1) 打开Open Hardware Manager

2) 点Open Target

3) 点Auto Connect

4) 右键点击xc7s50_0

5) 点Program Device

6) 点Program

正常情况会自动填写bit文件路径,不用手动修改,如果要烧写别的程序,可以手动输入。

然后点Program开始烧写,烧写完会自动开始运行

4. 运行效果

烧写完成串口马上输出了RTY GPIO/UART DEMO!

并且可以看到板上的灯开始闪烁变色