IEEE1149.1 学习笔记 (二)

- 测试逻辑结构

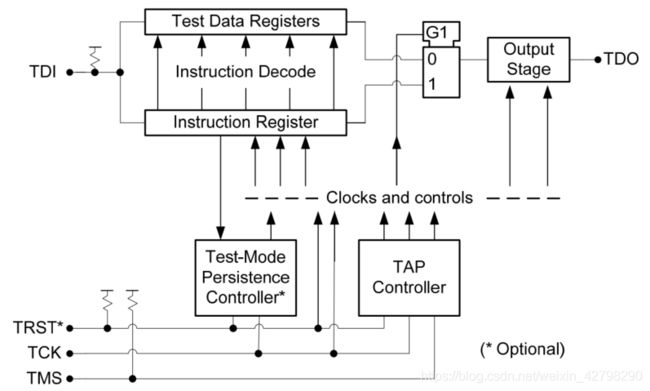

测试逻辑中必须包含的元素:

(1) TAP controller

(2) 指令寄存器

(3) 一组TDR

IR & TDR 应有单独的移位寄存器传输路径,并行连接关系,有公共的数据输入/输出端口连到TAP TDI/TDO

TAP Controller 通过TDI/TDO 控制IR/TDR 的切换与配置

测试逻辑中也可以包含test mode persistence controller (TMP)

此设计的重要特点:

(1) TAP controller 既可以接收TCK 信号及对TMS信号做出反应,也可以产生时钟和其它IR/TDR 等需要的控制信号

(2) TAP controller 控制操作(reset,shift,capture,update),指令提供操作对象

(3) 指令寄存器将指令移位到design中,选择对应操作的TDR

(4) IR需定义,且在TDI/TDO之间总存在一位TDR (bypass TDR)

(5)TDR 应包含一个bypass & boundary scan reg. 也可包含其他可选标准TDR: 如 device identification 。IR 选择TDR。

(6)可选TMP controller 接收TCK 及 IR 的解码,修改TAP controller 产生的一些控制信号。

测试逻辑的实现

TAP controller,和可选的TMP controller ,IR 及 控制指令的相关电路,TDR应为专有电路。若期望TDR 配置对片上系统逻辑不产生任何影响,则TDR相关电路应为专有电路。某些情况下,TDR可复用,比如device identification reg 和 boundary scan reg

- 测试逻辑控制器

测试逻辑状态机 , 有限状态机

强制的TAP controller : 同步有限状态机,对TCK / TMS 的激励做出响应,控制测试逻辑行为,同一测试链上components之间保持同步。

可选的TMP controller:同步有限状态机,对特定指令做出响应,强制component 保持当前测试状态

TAP controller 状态图

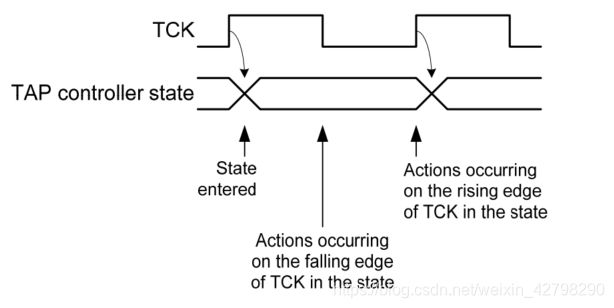

图2:TCK 上升沿根据TMS激励,TAP controller 状态机改变。

测试逻辑应以TCK上升沿或下降沿发生状态的改变。如图3

(1) Test-Logic_reset

若TMP controller 不存在或处于persistence-off 态,测试逻辑能处于已知态以便系统能正常工作。可以通过例化IR 寄存器去包含IDCODE 指令,或者当device identification register 不存在时,通过bypass 寄存器实现。若存在TMP controller 且其处于Persistence ON 状态,components 可能处于测试模式,进行进一步测试。

这个状态不会直接影响系统逻辑。在上电序列中,TAP保持在此状态,或者没有定义为干扰系统逻辑和I / O之间的信号流的指令处于活动状态,该组件将执行其设计功能。 但是,如果执行了一条或多条指令,这些指令会干扰进出系统逻辑的信号流(例如EXTEST),则系统逻辑可能处于不确定状态,重新连接引脚可能会导致行为无法预测。

无论系统处于状态机的哪种状态,只要持续的输入TCK和高电平的TMS信号,那么最多5个TMS=1,电路即可回到Test-Logic-Reset状态(或低电平的TRST 信号)

离开Test -Logic-Reset 状态后,状态机进入Run-Test/Idle 状态,这个状态不会有任何动作,因为当前指令已经选择device identification 或 bypass register。 测试逻辑在Select-DR-Scan 和 Select-IR-Scan 状态下也是处于inactive

(2) Run-Test/Idle

scan operation 的中间状态。一旦进入,只要TMS为低电平信号,状态机会一直保持此状态。当TMS信号变为高电平,在TCK 上升沿时刻,状态机进入Select-DR-Scan 态

在Run-Test/Idle 状态下,只有特定指令才会造成所选测试逻辑运动。例如,RUNBIST 指令 会使片上系统在此状态下进行自检。对于不在此状态下执行的指令,这个状态会造成一个延时,所有被当前指令选择的TDR 会保持之前的状态

当TAP controller 处于此状态时,指令不发生改变

(3) Select-DR-Scan

中间态,在TCK 下一个上升沿时退出此状态。在此状态,当前指令选择的TDR 保持他们之前的状态

Select-DR-Scan + TMS=0 + TCK 上升沿 --> Capture-DR

Select-DR-Scan + TMS=1 + TCK 上升沿 --> Select-IR-Scan

当TAP controller 处于此状态时,指令不发生改变

(4) Select-IR-Scan

中间态,在TCK 下一个上升沿时退出此状态。在此状态,当前指令选择的TDR 保持他们之前的状态

Select-IR-Scan + TMS=0 + TCK 上升沿 --> Capture-IR

Select-IR-Scan + TMS=1 + TCK 上升沿 --> Test-Logic_Reset

当TAP controller 处于此状态时,指令不发生改变

(5) Capture-DR

中间态,此状态下TCK上升沿触发数据加载到当前指令所选TDR的shift-capture path 上,使TAP 退出此状态。若当前指令所选TDR 没有并行输入端口,或者所选测试不需要capture,则寄存器保持之前状态不改变。

当TAP controller 处于此状态时,指令不发生改变

Capture-DR + TMS=0 + TCK 上升沿 --> Shift-DR

Capture-DR + TMS=1 + TCK 上升沿 --> Exit1-DR

(6) Shift-DR

在此状态下,TDI -TDR- TDO 形成shift 通路,TDI 灌入激励,TDO 移出 (TCK 上升沿) 。被当前指令选择 且不在serial path 中的TDR 保持当前状态

当TAP controller 处于此状态时,指令不发生改变

Shift-DR + TMS=0 + TCK 上升沿 --> Remain in Shift-DR

Shift-DR + TMS=1 + TCK 上升沿 --> Exit1-DR

(7)Exit1-DR

中间态。被当前指令选择的TDR保持之前的状态

当TAP controller 处于此状态时,指令不发生改变

Exit1-DR + TMS=0 + TCK 上升沿 --> Pause-DR

Exit1-DR + TMS=1 + TCK 上升沿 --> Update-DR

(8) Pause-DR

此状态会使TDI和TDO之间serial path 上的TDR 暂时停止shift 动作,被当前指令选择的TDR 维持之前的状态

Pause-DR + TMS=0 + TCK 上升沿 --> Remain in Pause-DR

Pause-DR + TMS=1 + TCK 上升沿 --> Exit2-DR

当TAP controller 处于此状态时,指令不发生改变

(9)Exit2-DR

中间态.被当前指令选择的TDR 维持之前的状态.

当TAP controller 处于此状态时,指令不发生改变

Exit2-DR +TMS=0 + TCK 上升沿 --> Shift_DR

Exit2-DR + TMS=1 + TCK 上升沿 --> Update-DR

(10)Update-DR

中间态

一些TDR会被提供锁存并行输出,以防止在特定指令下(Extest,Intest,RUNBIST)数据移位到相应的shift-capture path 上。在此状态下,TCK 的下降沿触发 数据从shift-capture path 锁存到这些TDR的并行输出上。所存的并行输出数据不会改变除非此状态下进行自检。

所有被当前指令选择的TDR的shift-capture path 保持之前状态不变

Update-DR +TMS=0 + TCK 上升沿 --> Run-Test/Idle

Update-DR+ TMS=1 + TCK 上升沿 --> Run-Test/Idle

(11)Capture-IR

中间态,当向量并行load 到 特定IR (TCK 上升沿),TAP controller 退出此状态

Capture-IR +TMS=0 + TCK 上升沿 --> Shift-IR

Capture-IR+ TMS=1 + TCK 上升沿 --> Exit1-IR

(12)Shift-IR

TDI–>IR 中的移位寄存器–> TDO

Shift-IR +TMS=0 + TCK 上升沿 --> Shift-IR

Shift-IR + TMS=1 + TCK 上升沿 --> Exit1-IR

(13)Exit1-IR

中间态

Exit1-DR +TMS=0 + TCK 上升沿 --> Pause-IR

Exit1-DR + TMS=1 + TCK 上升沿 --> Update-IR

(14)Pause-IR

可使IR的移位动作暂时停止

Pause-IR + TMS=0 + + TCK 上升沿 --> Pause-IR

Pause-IR + TMS=1 + + TCK 上升沿 --> Exit2-IR

(15)Exit2-IR

中间态

Exit2-IR+ TMS=0 + + TCK 上升沿 --> Shift-IR

Exit2-IR + TMS=1 + + TCK 上升沿 --> Update-IR

(16)Update-IR

中间态

IR 寄存器 shift-capture-path 上的值在TCK下降沿锁存到并行输出端口。一旦锁存新的值,它成为了当前的指令

Update-IR + TCK 上升沿 + TMS = 0/1 --> Run-Test/Idle

TAP controller 的操作

TAP controller 以一下激励时改变状态:

(1)TCK 上升沿

(2) TRST =0

(3)包含TAP电路的上电

TAP controller 产生控制IR/TDR的信号

TDO 在状态机中以TCK下降沿反应

TAP controller 的初始化

TAP controller 在上电时应处于Tets-Logic-Reset 状态

TAP controller 不应被系统任何端口初始化

TRST 与 TCK 是异步的

TAP controller 完成初始化的结果应等同于TRST=0