计算机的存储系统

1.现代计算机的结构

数据在计算机内部是如何存储的?现代计算机的结构中主机的内部有一个主存储器,也就是我们所说的内存,还有就是辅存,如手机中的机身存储 ,这些存储器的容量时不一样的,主存会更小,而辅存会更大,除了主存和辅存外,计算机内部还有没有可以存储数据的设备呢? 为什么主存和辅存之间的存储容量差距这么大?它们之间有没有速度差异呢?

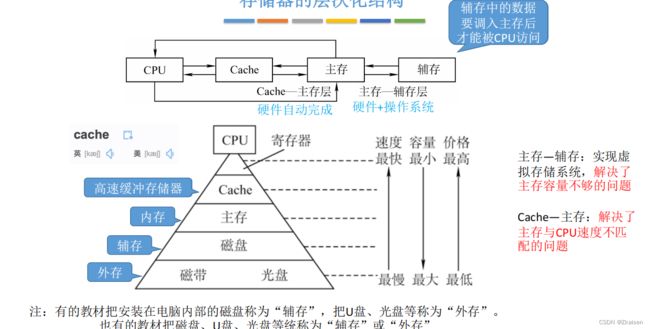

2.存储器的层次结构

存储器的层次结构: 在这个存储结构中,越靠近上层的速度越快,容量越小,造价也越高;越靠近下层速度越慢,容量越大,当然价格越低。

前边主存8GB,由于主存靠近上层,速度是比较快的;机身存储128GB也就是辅存,它的速度会更慢。我们平时下载的APP如微信、QQ等都是存储在辅存中的,它的读写速度是比较慢的,CPU不能直接与辅存进行数据交互,CPU的数据处理速度很快,如果让CPU和辅存直接进行数据交互,那么CPU的速度会被辅存所拖累,所以要先把辅存的内容调到主存中,才能被CPU访问。

CPU与主存:CPU可以直接从主存中读数据,也可以直接往主存中写数据。

主存与Cache:在主存之上还有一层高数缓冲存储器Cache,CPU可以从Cache中读数据,也可以往Cache中 写数据;Cache可以从主存中读数据Cache被更改的数据也可以写回主存。

增加高速缓冲存储器的作用:主存读写速度虽然已经 很快了,但是它的速度远远跟不上CPU,为了缓解主存和CPU的速度矛盾,计算机硬件把当前可能被频繁使用的数据从主存复制一份到 Cache当中,CPU可以直接读取Cache中的副本数据,由于Cache是更靠近上层的存储层,所以读写速度更快。设置Cache是为了缓解CPU和主存之间的速度矛盾

寄存器:在Cache之上还有寄存器,它是更靠近CPU的,比如ACC累加寄存器,MQ乘商寄存器等寄存器的读写速度要比Cache快得多,所以CPU在进行加减乘除等数值运算的时候会把操作数先保存在寄存器中,CPU内部的寄存器的数量是十分有限的。

辅存:计算机里的机械硬盘就是辅存

外存:如磁带、光盘、U盘等

主存和辅存:主存和辅存之间的数据交换是由硬件和操作系统来实现的,操作系统需要负责实现页面置换算法,根据页面置换算法确定哪些数据需要从主存置换到外存,主存和Cache之间的数据是由硬件自动完成的。

主存和辅存之间的数据交换就构成了虚拟存储系统,解决了主存容量不够的问题

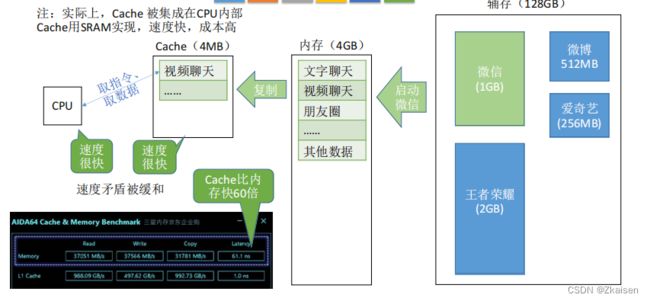

3.Cache的基本原理

不采用Cache的情况,假设你的手机机身存储128GB,安装了微信、微博、王者荣耀等程序,启动微信的过程就是将微信所需的代码块和数据从辅存调入主存的过程,假设你在和朋友视频,CPU只会用到”视频聊天“相关的指令代码,如果一条一条的从内存中读取指令的话CPU的速度会被访问内存所拖累,引入Cache就是为了解决CPU和主存之间的速度矛盾。

引入Cache后,我们就能先把与”视频聊天“相关的代码放入Cache中,CPU直接从Cache中读取视频相关的指令和数据,缓解了CPU和主存之间的速度矛盾。

Cache是被集成在CPU内部的,因为CPU芯片的造价高,芯片体积很小,集成度高,所以Cache的容量是很有限的,那么我们应该如何选取所需的代码来放入Cache呢?

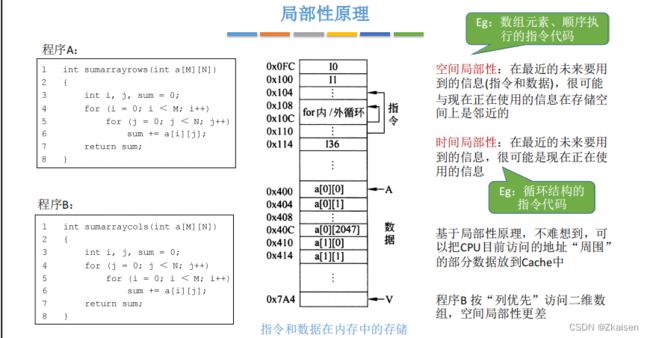

4. 程序局部性原理

我们有时候使用的不只是仅仅和视频相关的一段代码,还需要其他的功能代码段,但是Cache的容量是有限的,怎样从主存中选取所需的代码合适呢?

空间局部性:在最近使用的未来要用的信息(指令和数据)很可能与现在正在使用的信息在存储空间上是临近的。(在计算机内部我们的程序和数据都是顺序存储的,我们所访问的时候也都是顺序访问的)

在访问二维数组时,我们访问数组的第一个元素时,数组的其他元素也很可能使用到,在计算机中数组元素的存储是线性的,即存完第一个元素紧接着存放第二个元素,因此在存储空间上是临近的,这是数据空间局部性,当然指令也存在空间局部性,因为我们执行的代码在计算机里面被翻译成一条一条的汇编指令顺序存放的,当执行某条指令的时候,这条指令紧挨着的其他指令也有可能被访问到。

时间局部性:在最近的未来要用到的信息,很可能是现在正在使用的信息。

理解时间局部性,最典型的就是for循环内部的指令,比如程序A中的加法指令,当我们访问了这条加法指令的时候,由于循环的存在,使得我们在未来很短时间内很可能再次使用到加法这条指令,这就是时间局部性。数据也存在时间局部性,比如for循环中的sum,i,j等变量。

基于局部性原理,我们可以把CPU目前访问的地址周围的部分数据放到Cache中,比如CPU访问了数组的第一个元素,那么我们就可以把数组的其他元素也都放到Cache中,这样CPU在访问数组元素的时候就可以直接从Cache中访问,就可以大幅的提升CPU运行的速度。

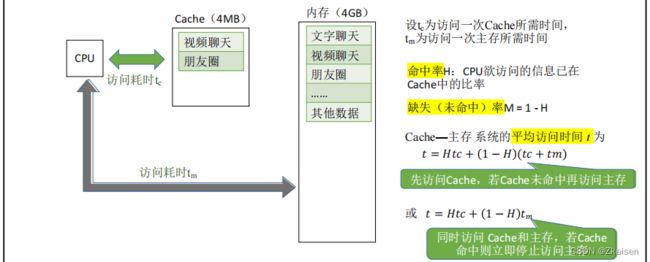

5.Cache性能分析

假设微信的程序在内存中占1GB,根据局部性原理,从当前执行的程序代码中复制了一段放到了 Cache中,设CPU访问一次Cache所需tc,CPU访问一次主存所需的时间为tm,如果CPU想要执行的视频聊天的功能,这部分代码可以直接从Cache中获取到,或者CPU想要读取朋友圈的数据,这些数据也可以在Cache中找到,对CPU想要的数据,如果可以直接在Cache中找到,这种现象称为Cache命中,与之对应的一个指标就是命中率,即CPU想要访问的信息已经在Cache中的比例是多少,与命中率对应的就是没有命中的概率也就是缺失率。

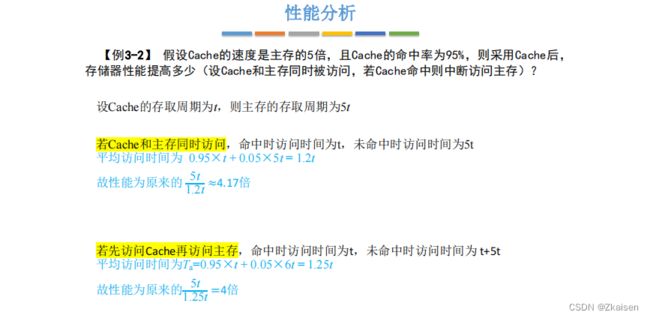

根据命中率以及访问Cache和主存的时间,我们就能计算出Cache-主存系统的平均访问时间。

引入Cache后系统性能的提升:

未引入Cache之前,CPU访问数据都要访问主存,需要存取周期为5t,引入Cache后(主存和Cache同时访问)存取周期为1.2t,性能提升了4.17倍。

主存和CPU的数据交换是以”块“为单位的