【vivado PG学习】1 PG168:7 Series FPGAs Transceivers官方配置方法学习笔记

目录

- 1 概览

-

- 1.4 不支持的功能

- 2 产品说明

- 3 用IP核进行设计

-

- 3.1 通用设计向导

- 3.2 时钟

- 3.3 复位

- 4 设计流程

-

- 4.1 生成IP核

- 4.2 约束IP核

- 5 例程

-

- 5.3 例程文件结构

介绍:

The 7 series FPGAs Transceivers Wizard LogiCORE™ IP 自动创建配置7系列fpga 收发器的HDL封装。向导可以配置一个或多个支持行业主流标准的高速串行收发器。或者从零开始支持各种自定义协议。

功能:

- 创建配置7系列fpga 收发器的HDL封装。

- 自动对模拟设置进行配置。

- 预定义了提供Aurora 8B/10B, Aurora 64B/66B, CEI-6G,DisplayPort, Interlaken, Open Base StationArchitecture Initiative (OBSAI), OC192,OC48, SRIO, 10GBASE-R, Common PacketRadio Interface (CPRI), Gigabit Ethernet,10 Gb Attachment Unit Interface (XAUI),RXAUI, and XLAUI, OTU3, 10GH SmallForm-factor Pluggable Plus (SFP+), OpticalTransport Network OTU3, V-by-One, SDI或者其他自定义的协议。

1 概览

关于向导:

可以创建收发器、设计实例、testbench以快速整合以及验证自定义功能的串行接口。

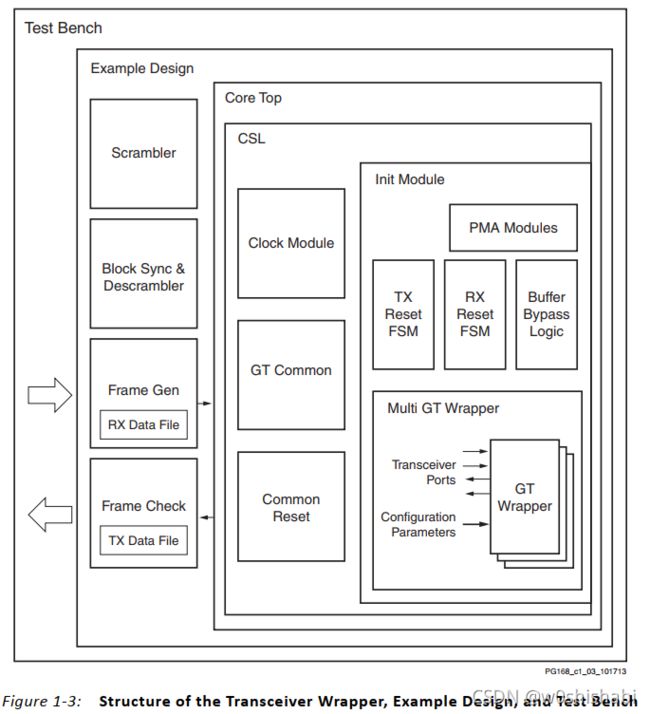

这个图有1个重要的点:

- 第二步,在选完协议后,下一步应确定收发器的位置。因为这个是跟引脚有映射关系的硬核,位置必须确定。

收发器的HDL封装、设计示例、testbench的结构:

1.4 不支持的功能

向导可以在TX和RX生成不对称数据位宽的设计(内部和外部不相等)的设计,但是不支持这样的功能或时序仿真。

向导不允许用户从两列中选择收发器(如果器件中有)。向导仅为GTZ收发器生成Verilog封装。

2 产品说明

7系列的收发器是低功耗的,GTP线速率高达6.6Gb/s,GTX 12.5Gb/s,GTH 13.1 Gb/s。

端口描述(不同协议端口数不一样):

| 端口 | 方向 | 时钟域 | 描述 |

|---|---|---|---|

| GTREFCLK_PAD_N_IN/GTREFCLK_PAD_P_IN | Input | - | fpga收发器块的差分时钟输入。某一个块中有好几个收发器 |

| SYSCLK_IN | Input | - | 设计示例的系统时钟。如果DRP(dynamic reconfiguration port )接口使能了,DRP_CLK_IN与SYSCLK_IN连接 |

| DRP_CLK_IN_P/DRP_CLK_IN_N | Input | - | 外部输入的DRP差分时钟对,给DRP接口 |

| TRACK_DATA_OUT | Output | rxusrclk | 表示在RX端接收到有效数据。这是一个电平信号。 |

| RXN_IN/RXP_IN | Input | RX serial clk | RXP和RXN是7系列FPGA收发器块中每个接收器的差分输入对。 |

| TXN_OUT/TXP_OUT | Output | TX serial clk | TXP和TXN是7系列FPGA收发器块中每个发射器的差分输出对。 |

3 用IP核进行设计

3.1 通用设计向导

串行收发器的位置:

根据所选串行收发器的总数,提供打算使用的每个串行收发器的具体位置。面板中显示的区域指示了串行收发器在器件中的位置。区域的划分是基于串行收发器相对于每个设备可用bufg的中位数的物理位置。

基于设计示例进行设计:

IP核的示例程序可以进行仿真和实现,自己的设计可以在此基础上进行,也可以作为排除自己的程序故障的参考。

保留寄存器:

用户程序和IP 核所有的输入和输出之间的寄存器可以简化时序以及提高系统性能。打拍很大程度的简化了时序分析以及让工具可以更好的布局布线。

识别关键时序路径:

示例的XDC文件说明了关键信号以及时序约束。

别瞎改IP核文件:

7 series FPGA transceiver core不允许用户修改,任何更改都可能造成系统时序以及协议问题。只能通过IDE的选项更改然后生成文件。

3.2 时钟

| 时钟 | 描述 |

|---|---|

| GTREFCLK_PAD_N_IN/GTREFCLK_PAD_P_IN | 收发器块的外部差分时钟 |

| DRP_CLK_IN_P/DRP_CLK_IN_N | 外部差分时钟,DRP接口时钟,即ip核设计中MMCM的输入时钟 |

| SYSCLK | 系统时钟用于驱动FPGA逻辑。当DRP接口使能时,DRP_CLK连接到syscclk。这个时钟需要在XDC中被约束。 |

| PLLLOCKDETCLK | 给反馈检测的稳定参考时钟,PLL的参考时钟,PLL的输入参考时钟或从PLL产生的任何输出时钟(例如TXOUTCLK)不能用来驱动这个时钟。此时钟仅在使用PLLFBCLKLOST和 |

| PLLREFCLKLOST端口的时候需要.在示例设计中,PLLLOCKDETCLK连接到DRPCLK或syscclk。PLLREFCLKLOST在TX/RX启动FSM模块中使用。 |

TX / RXUSRCLK和TX / RXUSRCLK2 的产生:

-

TXUSRCLK 和 TXUSRCLK2用TXOUTCLK产生,收发器的输出。

-

TXOUTCLK的源可以是参考时钟或PMA时钟。

-

RXUSRCLK and RXUSRCLK2可以使用TXOUTCLK 或 RXOUTCLK产生。

-

RXOUTCLK的源可以是参考时钟或者恢复时钟。

TX/RXOUTCLK通过一个混合模式时钟管理器(MMCM)或BUFG路由到FPGA逻辑。当TXUSRCLK和TXUSRCLK2不匹配、RXUSRCLK和RXUSRCLK2不匹配时,需要配置MMCM,在示例设计中则会根据情况自动配置MMCM。

3.3 复位

设计示例中的FSM复位的目的:

- 初始化FSM以满足要求。

- 用于解决诸如fpga配置和RX数据中断或更换(如电缆插头或拔出)等问题。

4 设计流程

4.1 生成IP核

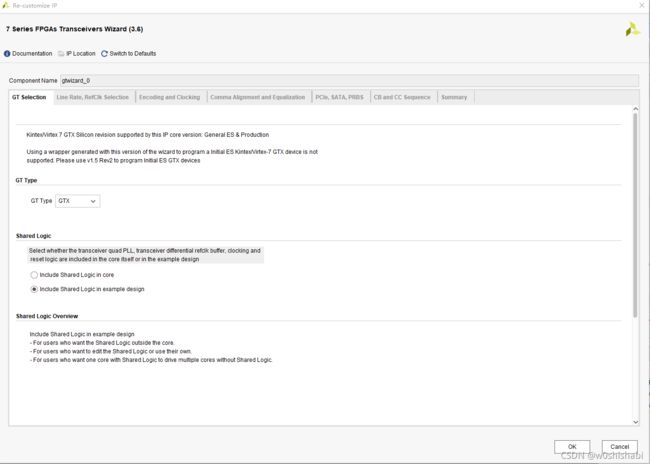

第1页:

Component Name:

GT Type:收发器类型,取决于器件是否支持。

Shared Logic:选择收发器块PLL、差分参考时钟缓冲器、时钟和复位逻辑是包含在IP 核中还是在示例程序中。

第2页:

Protocal: 从下拉列表选择协议。

选择收发器的位置和时钟,左下会显示所有器件支持的收发器。7系列收发器具体位置在《UG476:7 Series FPGAs GTX/GTH Transceivers》有写。

TX:

| 选项 | 描述 |

|---|---|

| Line Rate | 置所需的目标线速率,单位为Gb/s。可以与接收的线路速率不同。 |

| Reference Clock | 从下拉列表中选择可用的时钟频率 |

| TX off | 勾选的话关闭收发器的TX通路 |

RX:

| 选项 | 描述 |

|---|---|

| Line Rate | 置所需的目标线速率,单位为Gb/s。 |

| Reference Clock | 从下拉列表中选择可用的时钟频率 |

| RX off | 勾选的话关闭收发器的RX通路 |

Use Common DRP: 选择此选项将应用COMMON block的动态重新配置端口(DRP)信号。

Advanced Clocking Option :使用此复选框可将所有可能的参考时钟端口调出到生成的封装。用于动态时钟切换。

*Vivado Design Suite Debug Feature:使用此复选框可以打开IP中的ILA和VIO核,用于硬件调试和控制。

选择收发器及参考时钟:

TX/RX Clock Source:确定提供给每个选定收发器的参考时钟信号的源。两对差分时钟信号输入引脚对REFCLK0和REFCLK1分别给四个收发器提供时钟,一共有四组,标签从下到上为Q0~Q4(k7 325 900为例,分别Q0Q3对应115118组)。每个收发机都可以访问本地信号组的时钟和相邻1或2组的时钟,这取决于收发器的位置。【一般都是选择本组的时钟,不要离太远】

各时钟域收发器分组对应关系

| 选项 | 说明 |

|---|---|

| REFCLK0/1 Q0 | 本地参考时钟到收发器Y0-Y3 |

| REFCLK0/1 Q1 | 本地参考时钟到收发器Y4-Y7 |

| REFCLK0/1 Q2 | 本地参考时钟到收发器Y8-Y11 |

| REFCLK0/1 Q3 | 本地参考时钟到收发器Y12-Y15 |

| REFCLK0/1 Q4 | 本地参考时钟到收发器Y16-Y19 |

| REFCLK0/1 Q5 | 本地参考时钟到收发器Y20-Y23 |

| REFCLK0/1 Q6 | 本地参考时钟到收发器Y24-Y27 |

| REFCLK0/1 Q7 | 本地参考时钟到收发器Y28-Y31 |

| REFCLK0/1 Q8 | 本地参考时钟到收发器Y32-Y35 |

PLL selection:

| 选项 | 说明 |

|---|---|

| QPLL | GTX、GTH:使用Quad PLL 时,四个收发器都用这玩意就可以减少功耗,因为这个可以被四个收发器共享 |

| CPLL | GTX、GTH:根据选择的收发器的线速率使用Channel PLL |

| PLL0 | GTP: PLL0在Quad的四个收发器上共享 |

| PLL1 | GTP: PLL1在Quad的四个收发器上共享 |

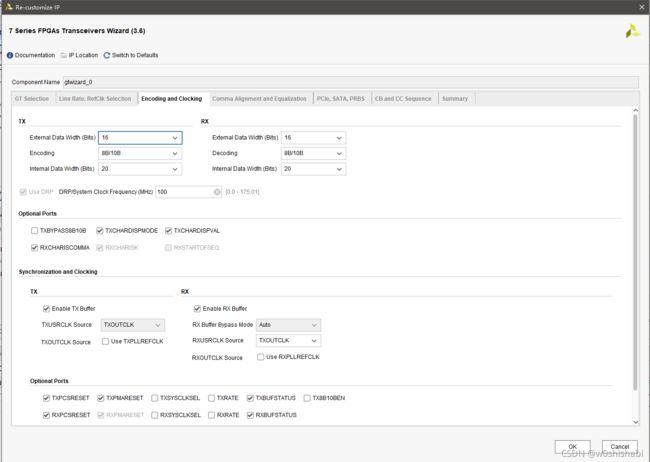

第3页:

TX/RX:

- External Data Width: 设定发射机应用接口的数据宽度

- Encoding: 编码方式

- Internal Data Width : 内部数据位宽,我们关注外部就行,内部位宽给我们计算相关时钟频率提供参考。

注意:RX设置应与TX设置相同

DRP/System Clock Frequency: 选择此选项使应用程序可以使用CHANNEL块的动态重新配置端口信号。

Optional Ports:

| 选项 | 说明 |

|---|---|

| TXBYPASS8B10B | 2bit位宽,8B/10B编码器每个byte的失能信号,高位对应高字节失能 |

| TXCHARDISPMODE | 2bit位宽,control disparity of outgoing 8B/10B data. 高位影响高字节 |

| TXCHARDISPVAL | 同上 |

| RXCHARISCOMMA | 2bit位宽,指示遇到有效的8B/10B comma字符,高位指示高byte数据路径 |

| RXCHARISK | 2bit位宽,指示遇到有效的8B/10B 字符,高位指示高byte路径 |

Synchronization and Clocking :

| 选项 | 说明 |

|---|---|

| Enable TX Buffer | 收发器中的TX缓冲区使能。这个缓冲区可以被绕过以获得低的、确定的延迟 |

| TX Buffer Bypass Mode | 此选项仅在TX缓冲区被绕过时有效。必须使用manual模式。 |

| Enable RX Buffer | 收发器中的RX缓冲区使能。这个缓冲区可以被绕过以获得低的、确定的延迟 |

| RX Buffer Bypass Mode | 这个选项只有在RX缓冲区被绕过时才可见。建议设置为auto模式。 |

TXUSRCLK / RXUSRCLK Source:

TX:TXOUTCLK: TXUSRCLK由TXOUTCLK驱动

RX:TXOUTCLK: RXUSRCLK由TXOUTCLK驱动。如果RX缓冲区被绕过,则此选项不可用。对于RX缓冲旁路模式,使用RXOUTCLK作为RXUSRCLK的源。

TXOUTCLK / RXOUTCLK Source:

TX:Use TXPLLREFCLK: 如果勾选,TXOUTCLK由输入参考时钟生成;否则向导将为TXOUTCLK选择适当的源。

RX:Use RXPLLREFCLK: 如果勾选,RXOUTCLK由输入参考时钟生成;否则向导将为RXOUTCLK选择适当的源。

Optional Ports:

| 选项 | 说明 |

|---|---|

| TXPCSRESET | 用于发送PCS逻辑的高电平复位信号 |

| TXBUFSTATUS | 2位信号监视TX弹性缓冲区的状态。当TX缓冲区被绕过时,此选项不可用。 |

| TXRATE | 传输速率改变 端口 |

| RXPCSRESET | 用于接收PCS逻辑的高电平复位信号 |

| RXBUFSTATUS | 指示RX弹性缓冲器的状态。当RX缓冲区被绕过时,选项不可用。 |

| RXBUFRESET | RX弹性缓冲逻辑的高电平复位信号。当RX缓冲区被绕过时,此选项不可用 |

| RXRATE | 接收速率改变 端口 |

| QPLLPD | 仅当选择GTX或GTH收发器时可见。QPLL的掉电端口 |

| CPLLPD | 仅当选择GTX或GTH收发器时可见。CPLL的掉电端口 |

| PLL0PD | 仅当选择GTP收发器时可见。QPLL的掉电端口 |

| PLL1PD | 仅当选择GTP收发器时可见。CPLL的掉电端口 |

| TXSYSCLKSEL | 选择驱动TX数据路径的参考时钟源。 |

| RXSYSCLKSEL | 选择驱动RX数据路径的参考时钟源。 |

| TXPMARESET | 用于发送PMA逻辑的高电平复位信号。 |

| RXPMARESET | 用于接收PMA逻辑的高电平复位信号。 |

| TX8B10BEN | X8B10BEN设置为高,以启用8B/10B编码器。 |

| RXCDRHOLD | 保持CDR控制 loop frozen。 |

| SIGVALIDCLK | 仅当选择GTH或GTP收发器时可见。OOB电路的时钟。 |

| CLKRSVD | 仅当选择GTX收发器时可见。OOB电路的时钟。 |

| TXPIPPMEN | 使能TX相位插补器PPM控制块。 |

| TXPIPPMOVRDEN | 使能直接控制TXPI。 |

| TXPIPPMPD | 关闭TX插补器PPM控制块。 |

| TXPIPPMSTEPSIZE | 指定要增加或减少PI代码的数量。 |

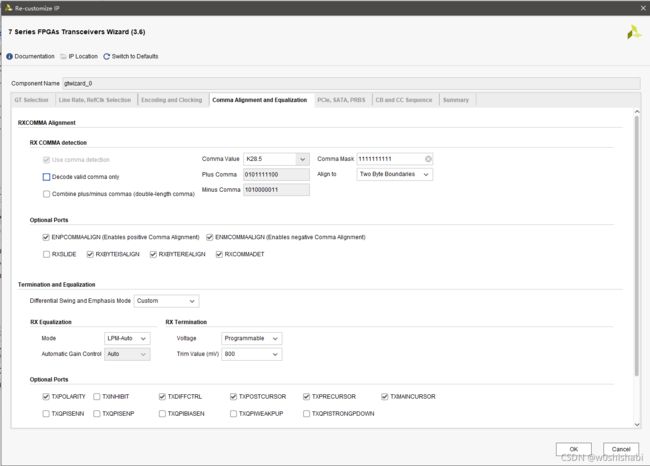

第4页:

设置comma字符和控制接收均衡和终端电压。

Comma Detection :

| 选项 | 说明 |

|---|---|

| Use Comma Detection | 启用接收comma检测。用于标识数据流中的comma字符和SONET帧字符。 |

| Decode Valid Comma Only | 当启用Use Comma Detection时,将检测限制为特定定义的comma字符 |

| Comma Value | 选择一个标准Comma模式或User Defined模式以输入自定义模式。 |

| Plus Comma | 表示要匹配的positive-disparity Comma字符的10位二进制模式。模式的最右位是连续到达的第一个位。 |

| Minus Comma | 表示要匹配的negative-disparity Comma字符的10位二进制模式。模式的最右位是连续到达的第一个位。 |

| Comma Mask | 10位二进制模式,表示Comma匹配模式的掩码。1表示Comma模式中匹配的对应位。0位表示不关心Comma模式中对应的位。 |

| Align to:Any Byte Boundary | 当检测到Comma时,使用Comma模式将数据流对齐到最近的字节边界 |

| Align to:Two Byte Boundary | 当检测到Comma时,使用Comma模式将数据流对齐到2字节边界 |

| Align to:Four Byte Boundary | 当检测到Comma时,使用Comma模式将数据流对齐到3字节边界 |

| Option Ports:ENPCOMMAALIGN | 高电平有效,当检测到Plus Comma模式时,使能字节边界对齐过程。 |

| Option Ports:ENMCOMMAALIGN | 高电平有效,当检测到Minus Comma模式时,使能字节边界对齐过程。 |

| Option Ports:RXSLIDE | 高电平有效,每个assertion按一位调整的字节对齐方式。优先于普通Comma对齐。 |

| Option Ports:RXBYTEISALIGNED | 高电平有效,指示并行数据流按字节边界对齐。 |

| Option Ports:RXBYTEREALIGN | 高电平有效,指示字节对齐已用最近的逗号检测更改。注意,在这种情况下可能会出现数据错误。 |

| Option Ports:RXCOMMADET | 高电平有效,表示Comma对齐逻辑在数据流中检测到Comma模式。 |

Differential Swing and Emphasis Mode:指定发射pre-cursor pre-emphasis模式设置。选择自定义模式,使能设置的差异摆动和 pre-emphasis级别。

RX Equalization:

| 选项 | 说明 |

|---|---|

| Equalization Mode | 设置接收端的均衡模式。 |

| Automatic Gain Control | 设置接收机的自动增益控制。可以设置为“AUto自动”或“Manual手动” |

| Use RX Equalizer CTLE3 Adaptation Logic (DFE mode only) | 仅适用于GTX收发器。如果勾选此项,则在示例设计中实例化CTLE3适配逻辑。 |

RX Termination: Termination Voltage:

- 选择GND接地内部终端网络。

- 选择Floating隔离网络。

- 选择AVTT将一个内部电压参考源应用到终端网络。

- 选择Programmable可编程选项,从下拉菜单中选择RX终止电压。

Optional Ports:

| 选项 | 说明 |

|---|---|

| TXPOLARITY | 高电平有效,转换发射机输出的极性。 |

| TXINHIBIT | 高电平有效,迫使发射机输出稳定。 |

| RXPOLARITY | 高电平有效,反转接收数据信号的极性。 |

| TXQPIBIASEN | 高电平有效,使QPI偏置。 |

| TXQPIWEAKUP | 高电平有效,QPI传输。 |

| RXDFEAGCOVRDEN | 高电平有效,DFE AGC over-ride |

| TXPOSTCURSOR | TXPOSTCURSOR 端口 |

| TXPRECURSOR | TXPOSTCURSOR 端口 |

| TXQPISENN | 发送QPI端口(负极性)。 |

| RXDFEMONITOROUT | 接收DFE监控端口。 |

| RXLPMHFOVRDEN | 接收低通覆盖使能端口。 |

| TXQPISENP | 发送QPI端口(正极性)。 |

| RXDFEMONITORSEL | 接收DFE监视器选择端口。 |

| RXLPMLFKLOVRDEN | 接收低通覆盖使能端口。 |

| TXQPISTRONGPDOWN | 发送QPI掉电端口。 |

| RXDFELPMRESET | 重置接收DFE/LPM块。 |

| TXDIFFCTRL | 发送驱动摆动控制。 |

| RXQPISENN | 在MGTRXN引脚上注册1或0的检测输出 |

| RXQPISENP | 在MGTRXP引脚上注册1或0的检测输出。 |

| RXQPIEN | 禁用QPI协议的RX终止。 |

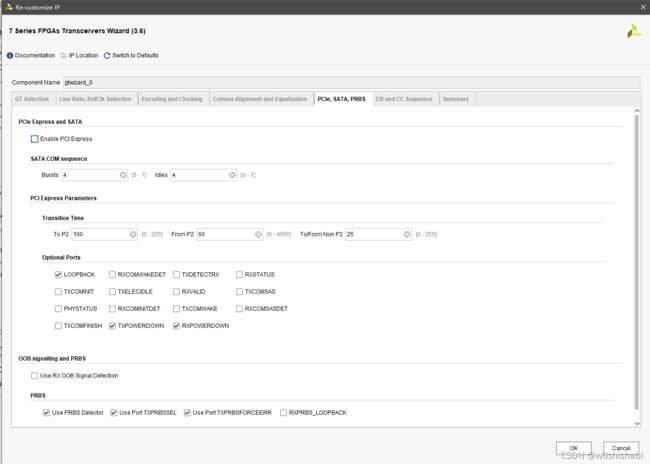

第5页:

Enable PCI Express: 选择该选项可开启PCI Express的某些特定操作,包括开启PCI Express省电模式和PCIe通道绑定选项。当PCI Express使用收发器时,此选项应该被勾选。

SATA COM Sequence:

- Bursts:0到7之间的整数值,表示声明COM匹配的突发序列数。该值默认为4,这是SATA规范中为COMINIT、COMRESET和COMWAKE指定的突发计数。

- Idles:0到7之间的整数值,表示声明a的空闲序列的数目COM匹配。每个空闲信号都是一个长度与COMINIT/匹配的OOB信号COMRESET或COMWAKE。

Transition Time:

- To P2::0到65,535之间的整数值。设置一个计数器,以确定PCI Express到P2电源状态的转换时间。

- From P2:0到65,535之间的整数值。设置一个计数器,以确定PCI Express从P2电源状态转换的时间。

- To/From non-P2:0到65,535之间的整数值。设置一个计数器,以确定PCI Express从P2以外的电源状态转换到或从电源状态转换的时间。

PCI Express Parameters:Optional Ports:

| 选项 | 说明 |

|---|---|

| LOOPBACK | 3bit位宽,使能各种数据环回模式进行测试。 |

OOB Signal Detection:

- Use RX OOB Signal Detection:启用内部OOB信号检测器。OOB信号检测用于PCIe和SATA。

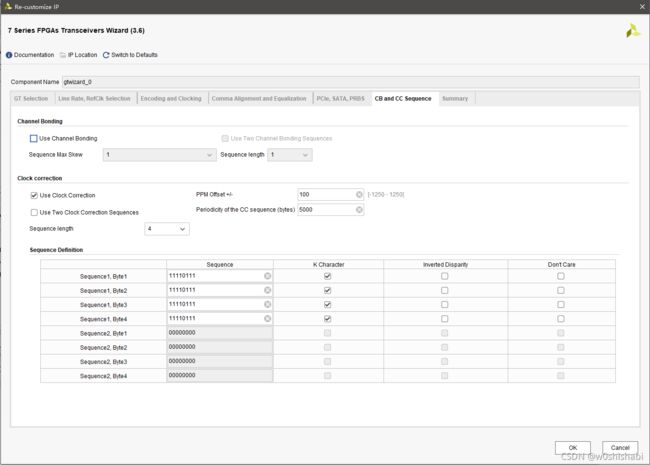

第6页:

Channel Bonding:

| 选项 | 说明 |

|---|---|

| Use Channel Bonding | 使能接收器通道使用唯一的字符序列绑定逻辑。当识别这些序列时,允许在接收缓冲区中添加或删除字符,以字节对齐多个数据收发器。 |

| Sequence Length | 在下拉列表中选择唯一通道绑定序列的字符数 |

| Sequence Max Skew | 从下拉列表中选择可通过通道绑定处理的最大字符倾斜。必须始终小于通道连接序列之间最小距离的一半 |

| Use Two Channel Bonding Sequences | 激活可选的第二通道绑定序列。任一序列的检测都会触发通道绑定。 |

Clock Correction:

| 选项 | 说明 |

|---|---|

| Use Clock Correction | 使能接收器使用独特的字符序列进行时钟校正逻辑,当识别这些序列时,允许在接收缓冲区中添加或删除字符,以防止由于发送/接收时钟频率的微小差异而导致的缓冲区下溢/溢出。 |

| Sequence Length | 从下拉列表中选择唯一时钟校正序列中的字符数(子序列)。 |

| PPM Offset | 发送时钟和接收时钟之间的PPM偏差。 |

| Periodicity of the CC Sequence | 表示在数据流中插入CC序列的时间间隔。 |

| Use Two Clock Correction Sequences | 激活可选的秒时钟校正序列。任一序列的检测触发时钟校正。 |

Sequences Didinition:

| 选项 | 说明 |

|---|---|

| Byte (Symbol) | 设置每个序列的字节 |

| K Character | 当选择8B/10B解码时,此选项可用。勾选后符号是一个8B/10B K字符 |

| Inverted Disparity | 一些8B/10B解码协议使用了故意颠倒disparity的符号。当序列中期望有这样的符号时,应该选中该选项。 |

| Don’t Care | 通过检查此选项,多字节序列可以具有通配符。序列中未使用的字节将自动设置此选项。 |

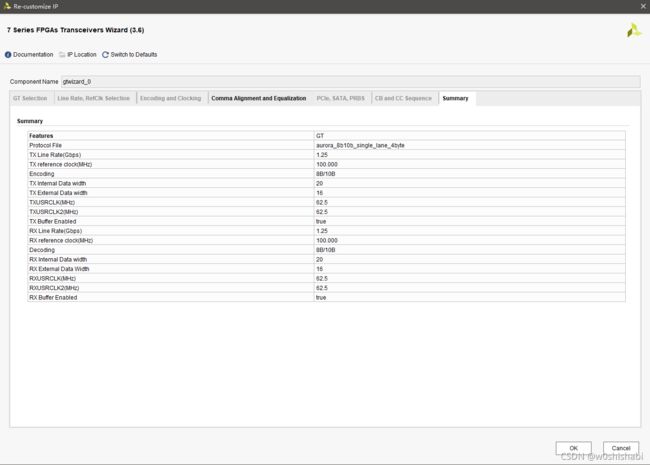

第7页:

4.2 约束IP核

IP核根据自定义的参数产生了对应的时序和位置约束。

时钟频率约束

create_clock

错误路径

系统时钟和用户时钟与其他时钟没有关联,这两时钟也没有确定的相位关系,这两个始终与需要设置位 false path。

set_false_path

收发器布局

根据自己选的的位置会生成对应的约束,如:

##---------- Set placement for gt0_gth_wrapper_i/GTHE2_CHANNEL ------

set_property LOC GTHE2_CHANNEL_X0Y0 [get_cells xaui_wrapper_support_i/xaui_wrapper_init_i/

IO约束

包括参考时钟这些都是固定的位置,所以上面的约束就已经对参考时钟、输入输出引脚之类的IO进行约束了。

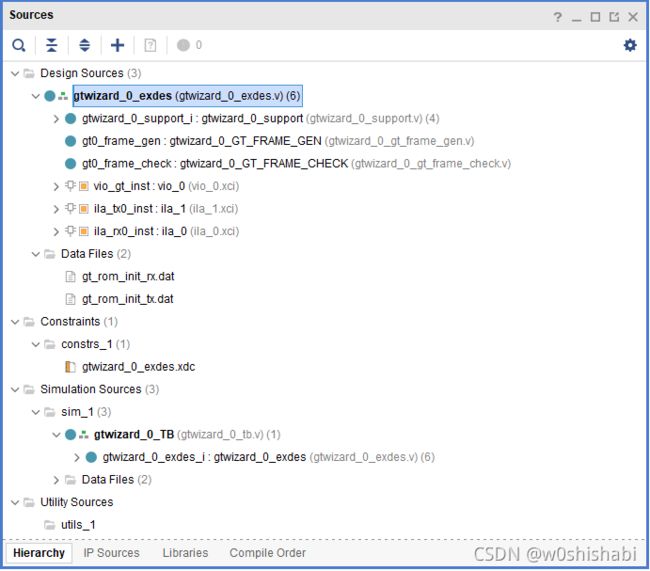

5 例程

5.3 例程文件结构

这里我的gtwizard_0

| 文件 | 说明 |

|---|---|

| _exdes.xdc | IP核自动生成的约束 |

| _tb.v[hd] | Test bench文件 |

| _gt_frame_check.v[hd] | 要在示例设计中实例化的帧检查逻辑。 |

| 要在示例设计中实例化的帧生成器逻辑。 | |

| 顶层设计的例子。包含收发器,重置逻辑,以及帧生成器和帧检查逻辑的实例化。还包含 Vivado Design Suite调试特性模块实例化。 | |

| gt_rom_init_tx.dat | gt_frame_gen模块的块RAM初始化模式。模式是用户可以修改的。 |

| gt_rom_init_rx.dat | gt_frame_check模块的块RAM初始化模式。模式是用户可以修改的。 |

| IP核支持层的7系列FPGA收发器设计 | |

| 收发器用户时钟模块,为收发器和用户逻辑生成时钟信号。 | |

| 这个文件实例化GTXE2_COMMON或GTXE2_COMMON原语,在各自的多个收发器核心之间共享。 | |

| 该文件生成复位电路,用于7系列fpga收发器向导核心的核心复位。 | |

| 给出了testbench进行功能仿真设计的实例。 | |

| 给出了testbench进行时序仿真设计的实例。 |

IP核文件结构_srcs\sources_1\ip\

| 文件 | 说明 |

|---|---|

| 收发器的主HDL封装。实例化单个收发器的封装用于目标设计 | |

| vho] | |

| 来自Vivado工具的日志文件,描述用于生成收发器封装的选项。Vivado工具为它在当前项目目录中创建的每个Wizard封装生成XCI文件。XCI文件还可以用作Vivado工具的输入。 | |

| 要在主收发器封装中实例化的单个收发器封装。使用所选协议的设置实例化所选收发器。 | |

| 仅限于GTZ收发器。要在主收发器封装中实例化的单个收发器封装。使用所选协议的设置实例化所选收发器。 | |

| 同上 | |

| gtwizard_v3_4_beachfront.v | 个文件应该用于将用户逻辑与GTZ收发器连接起来。 |

| tx_startup_fsm.v[hd] | 发射器复位模块。这个文件不是为GTZ收发器生成的。 |

| rx_startup_fsm.v[hd] | 接收器复位模块。这个文件不是为GTZ收发器生成的。 |