【DRAM存储器八】SDRAM介绍-part2

个人主页:highman110

作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

参考资料:《镁光SDRAM数据手册》、《PC SDRAM specification》

目录

SDRAM基本功能介绍

命令真值表

模式寄存器

上电和初始化

NOP和DSEL

Row activate

Read

Write

Precharge

DQM

刷新

Power down

Clock Suspend

SDRAM基本功能介绍

命令真值表

SDRAM支持如下基础命令,通过地址/控制信号的不同高低电平组合表示不同的命令。先对这些命令有个总体认识,后面再挑几个重点进行介绍。

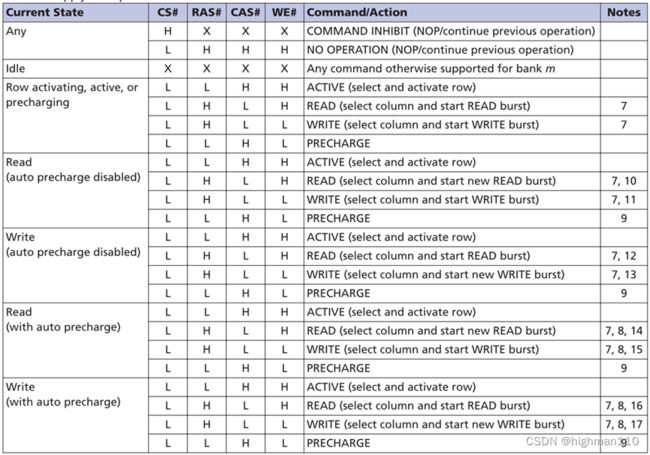

如下表为同一个bank内状态跳转的操作命令,current state是当前状态,command/action是下一步动作。比如当前是read,下面可以接read、write、Precharge、BURST TERMINATE命令。

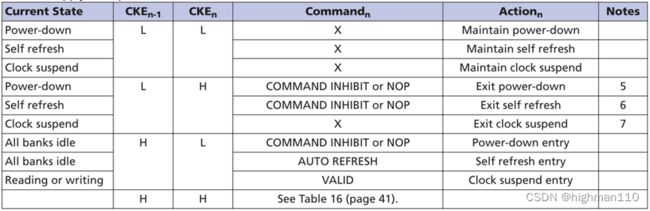

下表为不同bank间状态跳转的操作命令:

表中H表示高电平,L表示低电平,X表示不关注,V表示value值。

表中H表示高电平,L表示低电平,X表示不关注,V表示value值。

模式寄存器

SDRAM的模式寄存器只有一个,很简单,规范写的更简单,有的比特没有写清楚,下面是从镁光256Mb SDRAM datasheet中截的图:

Mode寄存器的值由地址线进行设置。各bit含义如下:

Bit[2:0]:BL,突发长度。支持1、2、4、8、full page 5种突发长度。

Bit[3]:burst传输方式,0表示顺序传输,1表示交错传输。

Bit[6:4]:CAS潜伏期,可设置为1、2、3,单位为时钟周期tck。

Bit[12:7]:操作模式,除了bit9之外,其他bit都是0,000000表示操作模式为突发读或突发写,000100表示操作模式为突发读或单一写。

上电和初始化

同样以镁光256Mb SDRAM为例进行说明,上电和初始化流程如下:

1.同时向VDD和VDDQ供电。

2.保持CKE为低电平。

3.提供稳定的CLK信号。

4.在发出NOP之外的任何命令之前,至少等待100μs。

5.从这100μs期间的某个点开始,使CKE变高。同时使用一个或多个NOP命令。

6.执行PRECHARGE ALL命令。

7.至少等待tRP(充电周期)时间;在此期间,必须给出NOP或DESELECT命令。所有存储体都将完成预充电,从而使设备处于所有存储体内的空闲状态。

8.发出AUTO REFRESH命令。

9.至少等待tRFC(自动刷新周期)时间,在此期间只允许NOP或COMMAND INHIBIT命令。

10.发出AUTO REFRESH命令。

11.至少等待tRFC时间,在此期间只允许NOP或COMMAND INHIBIT命令。(注意:这里应该是至少需要两个自动刷新命令,也可以比两个多,SDRAM规范文档里写的是8个,不太明白为什么这里是两个,可能器件的工艺有提升)

12.SDRAM现在已准备好进行模式寄存器编程。由于模式寄存器将在未知状态下通电,因此在应用任何操作命令之前,应对其进行设置。使用LMR命令(load mode register,规范里此命令symbol为MRS,mode register set),对模式寄存器进行编程。编程设置后该寄存器将保留设置值,直到再次编程或设备断电。初始化时不对模式寄存器进行编程将导致可能不需要的默认设置。整个初始化器件,输出DQ应为高阻状态。

13.至少等待tMRD时间完成模式寄存器设置,在此期间只允许NOP或DESELECT命令。

14.芯片初始化完毕,可以支持其他有效命令的输入。

初始化操作图如下:

NOP和DSEL

DSEL就是Deselected,器件没有被选中,即CS#为高,这时器件忽略所有控制信号的输入。NOP即NO operation,无操作,此时CS#为低,RAS#、CAS#、WE#为高,举例来说,行激活active之后,再到列选通,中间有一个tRCD(RAS# to CAS# delay)时间的延迟,这段时间不能操作DRAM,这段时间用NOP操作。

Row activate

初始化完成后,要想对某个存储单元进行寻址,就必须先找到并打开对应的bank和对应的行,bank地址和行地址是同时发出寻址的,所以这个过程叫行激活,也叫bank activate。如下图所示,CKE、CS#、RAS#、CAS#、WE#的高低电平组成行激活命令,DRAM在时钟CLK上升沿锁存行地址和bank地址。

行激活有两个间隔定义:同一个bank内的不同行激活的间隔为tRC,不同bank间的行激活间隔为tRRD,tRRD要比tRC小很多,因为在同一个bank内,必须要将当前行进行预充电后才能打开另一行,而不同bank间没有这个限制,通过多bank间的interleaving操作,可以显著提升吞吐量。

Read

下篇介绍

Write

下篇介绍

Precharge

下篇介绍

DQM

下篇介绍

刷新

下篇介绍

Power down

下篇介绍

Clock Suspend

下篇介绍