【接口技术】总线

【接口】

接口概念:若干个端口 + 控制逻辑电路

端口:接口电路中可读/写的寄存器,传送数据信息、控制信息和状态信息

输入数据 —— I/O设备的状态信息

输出数据 —— 控制信息

接口的三大端口:数据端口(存放数据信息)、控制端口(存放控制命令)、状态端口(存放状态信息)

输入指令(IN):读出端口信息

输出指令(OUT):信息写入端口

对状态端口只进行输入,对命令端口只进行输出

IN/OUT —— CPU和接口之间传输

MOV —— CPU内部,或CPU和内存之间传输

接口设计过程:

- 分析接口两侧情况

- 合理选择接口芯片

- 正确分析相关芯片的时序搭配

- 进行正确的信号转换(数模、串并)

- 接口驱动程序的分析与编写

【微型计算机总线】总线标准、总线指标、总线分类(XT、ISA、PCI、PCI-E)

总线:

一组传输公共信号线的集合,传输地址、数据和控制信号,由一组导线和相关的控制(协议)驱动电路组成

主板上的印制电路线将各插槽的相应点连接起来,即为总线

总线标准:芯片之间、扩展卡之间和系统之间,通过总线进行连接和传输时,应该遵守的协议与规范

接口标准:外设接口的规范,包括接口信号线定义、信号传输速率、信号传输方向和拓扑结构、电气特性和机械特性等

总线与接口的区别:

- 总线标准为公用性;接口标准大多为专用性

- 总线以总线扩展槽形式供用;接口以接口插座(插头)形式供用

- 总线并行;接口串、并均有

- 总线信号线多且齐全,有分离的控制总线、数据线和地址线;接口信号线少且不齐全,共用控制线、数据线和地址线

总线串行化趋势,使总线和接口难以区分

总线特性:

- 物理特性:物理连接方式

- 功能特性:每一根线的功能

- 电气特性:每一根线上信号的传递方向和有效电平范围,IN和OUT

- 时间特性:每一根线何时有效

总线主要性能参数:

- 总线频率:工作频率(MHz)是总线频率的主要参数

- 总线宽度:数据总线的位宽

- 总线数据传输率:总线频率 * (总线宽度 / 8位)

总线分类:

| 划分标准 |

划分结果 |

| 总线结构 |

单总线;双总线;三总线 |

| 功能和信号传输类型 |

数据传送线;仲裁总线;中断和同步线;公用线 |

| 总线层次 |

CPU总线(内部总线);局部总线;系统总线(I/O总线);通信总线(外部总线) |

数据传送线:地址总线(单向) + 控制总线 + 数据总线(双向)

总线标准:

制定组织:IEEE、IEC、ITU、ANSI

总线的负载能力:当总线接上负载后必须不影响总线输入/输出的逻辑电平

总线输出驱动能力,总线输入影响插件板

增加总线负载能力的方法:在总线和负载之间加缓冲器或驱动器(驱动 + 隔离)

【XT总线】

将 CPU的引脚经过8282锁存器、8286发送接收器、8288总线控制器、8259中断控制器、8237DMA控制器以及其他逻辑电路的重新驱动和组合控制

总线信号线安排:共62条

双向数据线8条:D7——D0

单向地址线20条:A19——A0

·执行一条I/O指令的过程?

指令周期:由1个或若干个总线周期组成

总线周期:CPU通过总线与外部进行传输所需的时间

时钟周期:CPU的时间基准

·IN AL, DX

·与XT总线连接,需要哪些信号线?

- 地址信号线A15——A0

- 数据信号线D7——D0

- 控制信号线 -IOR、-IOW、AEN

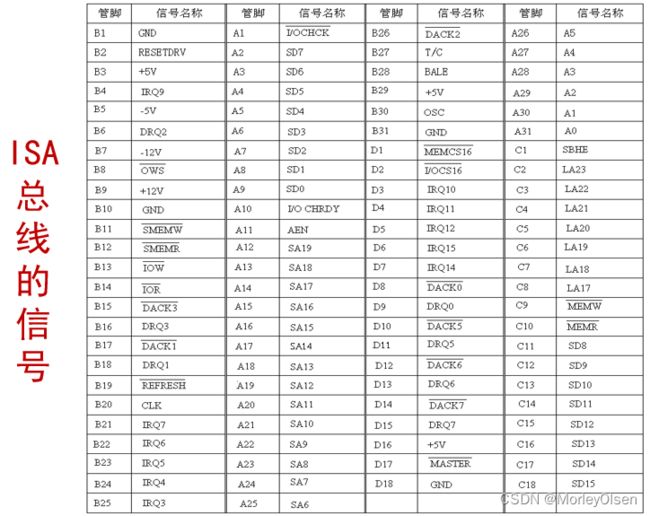

【ISA 总线】

工业标准体系结构,Industry Standard Architecture

ISA插槽:基本的62线8位插槽 + 扩展的36线插槽

数据线 D0——D15

低位地址线 A0——A19

高位地址线 LA17——LA23

地址锁存允许信号(输出) ALE

中断请求信号(输入) IRQ2——IRQ7、IRQ10——IRQ14

地址使能信号(输出) AEN :高电平表示DMA周期,CPU控制总线时保持低电平

【PCI总线】

外围部件互连总线,Peripheral Component Interconnect

PCI特点:

- 突发传输模式

- 独立于CPU工作(通过主桥路和处理器相连)

- 自动配置功能(256字节的配置空间支持,即插即用)

突发传输:两个设备之间不间断的连续数据传送。可由某个地址起读、写大量数据,地址自动加1

主桥路:北桥Host/PCI、南桥PCI/ISA、PCI/PCI桥

PCI插槽和扩展卡:

工作电源电压:5V 或 3.3V

连接器:32位 或 64位

5V的连接器用于3.3V时,需要旋转180度

PCI总线接口信号:

地址期:FRAME# 有效的第一个时钟周期

数据期:IRDY#、TRDY# 同时有效的时钟周期

PCI地址空间:

三种独立的地址空间:内存地址空间、I/O地址空间、配置地址空间

地址译码方式:正向/反向

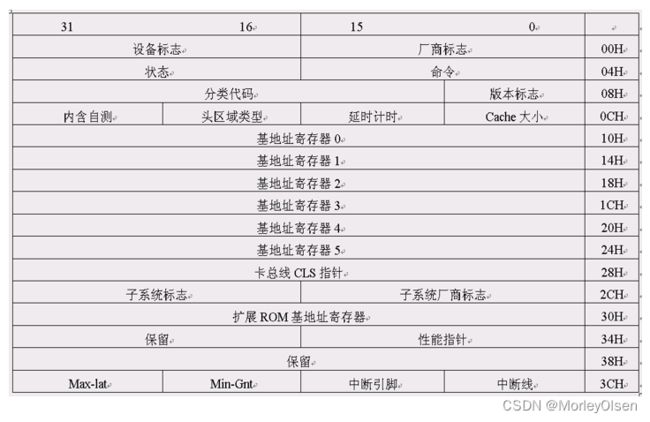

PCI配置空间:

·一个物理PCI设备可能包含多个功能块

·一个设备的所有功能(总线标准规定最多8个功能)共用一个IDSEL信号

·每个功能均有一个配置空间

配置空间大小256B(64个双字),头区域64B(如下图)

·基址寄存器,地址空间分配:

I/O空间分配(最大2^8=256字节,最小2^2=4字节)

存储空间分配(最大2^31=2GB,最小2^4=16字节)

基地址寄存器占用24B的头标区空间,最多容纳6个4B的基地址寄存器,所以PCI设备最多申请6段32位地址区域空间

配置空间访问的实现方法:

配置机构:PCI协议规定,将处理器发出的I/O访问转换为配置访问的转换机构

配置机构实现方法:用两个特定的32位I/O端口对应两个配置寄存器

·配置地址端口寄存器(I/O地址为0CF8H~0CFBH)

·配置数据端口寄存器(I/O地址为0CFCH~0CFFH)

(开头是字母,则加一个0进行区别)

配置地址信息格式:第31位“使能位”用来决定是否允许访问配置空间,第0、1位上的“0”用来要求只能按双字(4字节)来读写配置空间寄存器

配置操作实现步骤:

- 将访问的地址(如图)写入配置地址端口寄存器

- 执行一次对配置数据端口寄存器的I/O访问

| 读操作 |

写操作 |

| MOV DX, OCF8H |

MOV DX, OCF8H |

| MOV EAX, 配置地址 |

MOV EAX, 配置地址 |

| OUT DX, EAX |

OUT DX, EAX |

| MOV DX, OCFCH |

MOV DX, OCFCH |

| IN EAX, DX |

MOV EAX, 空间分配 |

| OUT DX, EAX |

配置空间访问的类型(PCI-PCI桥):

·0类配置请求:AD[1:0]=00,访问当前PCI总线(本地)上的目标寄存器

·1类配置请求:AD[1:0]=01,访问下一级PCI总线上的目标设备

目标PCI桥处理:

·总线号为本PCI桥下:将AD[1∶0]改为00,将AD[31∶0]传给桥下总线进行0类配置访问

·总线号属于本PCI桥下总线的下级总线范围:将AD[31∶0]传给桥下总线进行1类配置访问

【PCI-Express】

PCI-E与PCI的不同:物理连接不同,通信模型及程序方法采用分层协议

PCI-E基于双向的1位串行差分对的点对点物理传输机制

由1、2、4、8、16、32个差分对构成的PCI-E分别为PCI-E ×1、×2、×4、×8、×16、×32标准

【USB总线】

Universal Serial Bus

特点:速度快、连接简单快捷、无需外接电源、支持多连接、兼容性良好、功耗低

USB系统的连接模式:树型结构,最多可连127个设备

USB系统的硬件:

- 主控制器/根集线器(Host Ctrl/Root Hub):前者连接到PCI总线,占用一定I/O地址空间,受CPU控制;后者连接到主控制器,只占1个USB逻辑地址,受主控制器控制

- USB集线器(USB Hub):由控制器、中继器组成,最多支持4个USB端口;每个USB Hub占用1个USB逻辑地址

- USB设备:功能设备类型分为高速、全速、低速;每个USB设备占用1个USB逻辑地址

其他概念:

- USB总线:由VCC、GND、D+、D-组成,共4根线,D+和D-通过差分半双工使用

- USB事务:USB总线上最基本的一次数据交换操作

- USB逻辑地址:不通过连线实现,USB系统自动配置所分配

- USB端口:连接USB总结的连接器

- USB端点:集线器或设备的内部寄存器,编号0—15

USB系统软件:

- USB设备驱动程序:将某用户操作请求转换成几个IRP(I/O请求包),并送给USB驱动程序

- USB驱动程序:将IRP转换成几个USB事务,并送给USB主控制器驱动程序

- USB主控制器驱动程序:将USB事务调度到一系列事务列表中,USB主控制器定时读取一个列表信息并执行

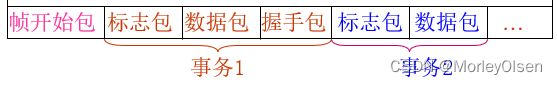

USB交换的包格式:

·USB事务的执行通过包交换(一次传输)完成

·一个USB事务由1~3个USB包组成,包的数量由传输类型决定

通信帧(定长):由帧开始包和若干事务的包组成