AXI VIP的简单使用

文章目录

- 基础

-

- 用途

- 架构

- 官方TestBench范例

-

- testbench的注意事项

- 小例

-

- 例子的用途

- 步骤

-

- 生成AXI VIP

- 添加测试文件

基础

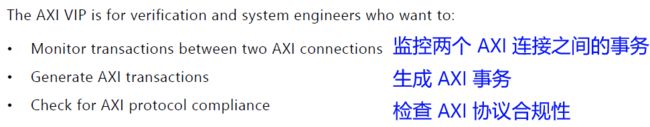

用途

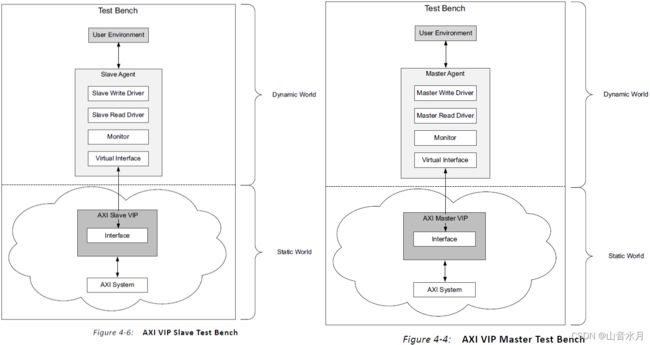

架构

The AXI VIP uses similar naming and structures as the Universal Verification Methodology

(UVM) for core design. It is coded in SystemVerilog. The AXI VIP is comprised of two parts.

One is instanced like other traditional IP (modules in the static/physical world) and the

second part is used in the dynamic world in your verification environment. The AXI VIP is an

IP which has a static world connected to the dynamic world with a virtual interface. The

virtual interface is the only mechanism that can bridge the dynamic world of objects with

the static world of modules and interfaces.

- AXI VIP 使用与UVM 类似的命名和结构,采用 SystemVerilog实现

- AXI VIP 可以像其他传统 IP一样被例化

- AXI VIP 的虚拟接口是一种将对象的dynamic world 与模块和接口的static world连接起来的机制

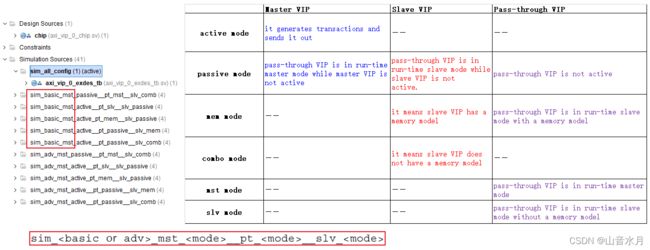

官方TestBench范例

- sim_all_config是最完备最复杂的,它展示了如何在复杂方法中使用 AXI VIP 的不同示例

- basic simulation set中展示了在tb文件中使用AXI VIP的代码片段

- dvanced simulation set中使用了更多的API

在sim_all_config的例子中,使用了3种发起写操作的方法,读操作也类似,

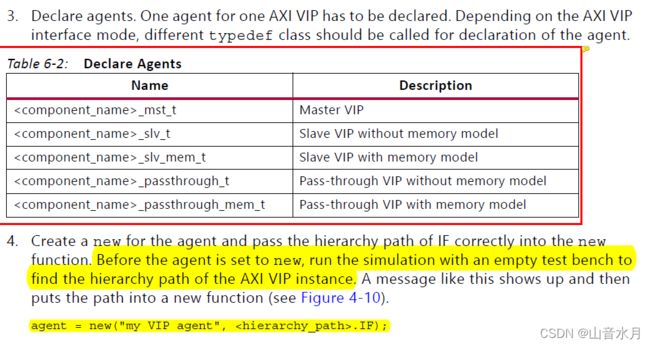

testbench的注意事项

- tb需要是systemverilog格式的文件

- 需要导入axi_vip_pkg and

_pkg - 需要声明并创建agent

- 需要正确设置AXI_VIP的IF路径

小例

例子的用途

将AXI_VIP作为master,对axi_gpio进行控制,观测gpio能否正常输入输出,并观察axi_lite时序

步骤

生成AXI VIP

添加测试文件

`timescale 1ns / 1ps

import axi_vip_pkg::*;

import axi_vip_design_axi_vip_0_0_pkg::*;

module tb_axi_vip();

/*************************************************************************************************

* 信号声明

*************************************************************************************************/

logic aclk;

logic aresetn;

logic [31:0] gpio_i;

logic [31:0] gpio_o;

//used in API and parital randomization for transaction generation and data read back from driver

axi_transaction wr_transaction; // Write transaction

axi_transaction rd_transaction; // Read transaction

xil_axi_uint mtestID; // ID value for WRITE/READ_BURST transaction

xil_axi_ulong mtestADDR; // ADDR value for WRITE/READ_BURST transaction

xil_axi_len_t mtestBurstLength; // Burst Length value for WRITE/READ_BURST transaction

xil_axi_size_t mtestDataSize; // SIZE value for WRITE/READ_BURST transaction

xil_axi_burst_t mtestBurstType; // Burst Type value for WRITE/READ_BURST transaction

xil_axi_lock_t mtestLOCK; // LOCK value for WRITE/READ_BURST transaction

xil_axi_cache_t mtestCacheType = 3; // Cache Type value for WRITE/READ_BURST transaction

xil_axi_prot_t mtestProtectionType = 3'b000; // Protection Type value for WRITE/READ_BURST transaction

xil_axi_region_t mtestRegion = 4'b000; // Region value for WRITE/READ_BURST transaction

xil_axi_qos_t mtestQOS = 4'b000; // QOS value for WRITE/READ_BURST transaction

xil_axi_data_beat dbeat; // Data beat value for WRITE/READ_BURST transaction

xil_axi_user_beat usrbeat; // User beat value for WRITE/READ_BURST transaction

xil_axi_data_beat [255:0] mtestWUSER; // Wuser value for WRITE/READ_BURST transaction

xil_axi_data_beat mtestAWUSER = 'h0; // Awuser value for WRITE/READ_BURST transaction

xil_axi_data_beat mtestARUSER = 0; // Aruser value for WRITE/READ_BURST transaction

xil_axi_data_beat [255:0] mtestRUSER; // Ruser value for WRITE/READ_BURST transaction

xil_axi_uint mtestBUSER = 0; // Buser value for WRITE/READ_BURST transaction

xil_axi_resp_t mtestBresp; // Bresp value for WRITE/READ_BURST transaction

xil_axi_resp_t[255:0] mtestRresp; // Rresp value for WRITE/READ_BURST transaction

// No burst for AXI4LITE and maximum data bits is 64

// Write Data Value for WRITE_BURST transaction

// Read Data Value for READ_BURST transaction

bit [63:0] mtestWData; // Write Data

bit[8*4096-1:0] Wdatablock; // Write data block

xil_axi_data_beat Wdatabeat[]; // Write data beats

bit [63:0] mtestRData; // Read Data

bit[8*4096-1:0] Rdatablock; // Read data block

xil_axi_data_beat Rdatabeat[]; // Read data beats

/*************************************************************************************************

* UUT

*************************************************************************************************/

axi_vip_design UUT (

.aclk ( aclk ),

.aresetn ( aresetn ),

.gpio_i ( gpio_i ),

.gpio_o ( gpio_o )

);

localparam PERIOD = 10.0;

initial begin

aclk = 0;

#(PERIOD/2);

forever #(PERIOD/2) aclk = ~aclk;

end

initial begin

gpio_i = 32'hABCD1234;

aresetn = 0;

#100;

aresetn = 1;

end

/*************************************************************************************************

* _mst_t for master agent

*************************************************************************************************/

axi_vip_design_axi_vip_0_0_mst_t mst_agent;

initial begin

/***********************************************************************************************

* Before agent is newed, user has to run simulation with an empty testbench to find the hierarchy

* path of the AXI VIP's instance.

***********************************************************************************************/

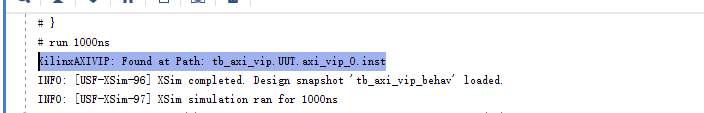

mst_agent = new("master vip agent",UUT.axi_vip_0.inst.IF); //可以先注释掉这句,打开simulator,查看路径

mst_agent.set_agent_tag("Master VIP"); //set tag for agents for easy debug

mst_agent.start_master(); // agent start to run

mtestID = 0;

mtestBurstLength = 0;

mtestDataSize = xil_axi_size_t'(xil_clog2(32/8));

mtestBurstType = XIL_AXI_BURST_TYPE_INCR;

mtestLOCK = XIL_AXI_ALOCK_NOLOCK;

mtestCacheType = 3;

mtestProtectionType = 0;

mtestRegion = 0;

mtestQOS = 0;

for(int i = 0; i < 256;i++) begin

mtestWUSER = 'h0;

end

#200;

@(posedge aclk);

mtestADDR = 0;

mtestWData = {32'h0,32'h1234};

mst_agent.AXI4LITE_WRITE_BURST(

mtestADDR,

mtestProtectionType,

mtestWData,

mtestBresp

);

mtestADDR = 0;

mst_agent.AXI4LITE_READ_BURST(

mtestADDR,

mtestProtectionType,

mtestRData,

mtestRresp

);

end

endmodule