Verilog HDL程序笔记3

Verilog HDL程序笔记3

Verilog HDL程序笔记1:写出属于你的第一个Verilog HDL模块

Verilog HDL程序笔记2:Testbench模块的使用

文章目录

- Verilog HDL程序笔记3

- 前言

- 一、电路逻辑描述法

- 二、结构化描述法

- 三、复杂电路小练习

- 总结

前言

前两章我们学会了搭建模块和测试模块。这一章我们来学习一下Verilog描述电路的另外一些方法。并且还会讲述一个更加复杂的电路的仿真例子。

一、电路逻辑描述法

这个方法是我自己命名的。本质上来说,这种方法就像我们真的在制作一个电路一样。哪根线接哪个引脚,十分地清晰明了。

下面我就举个例子让大家感受一下。

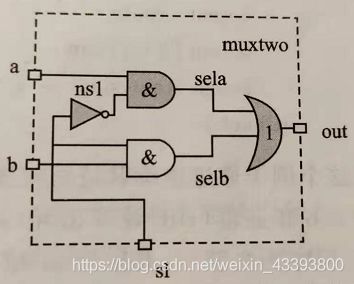

这是一个二选一数据选择器,也是我们第一章实现了的模块的内置电路。

有了数电基础后,我们可以很轻松地就看懂这个电路的逻辑了。

我们现在试一下用Verilog来写一遍他的逻辑。

module muxtwo(a,b,sl,out);//写出模块名和接口名

input a,b,sl;

output out;

wire nsl,sela,selb;//这里可以理解为连接电路的几根跳线

//wire型变量要用assign赋值

assign nsl=~sl;//非门直接取反

assign sela=a&nsl;//与门直接将两根线相与

assign=selb=b&sl;

assign out=sela|selb;//或门

endmodule

看,是不是非常简单明了。我们所设的wire型变量就好像真的是导线一样。我们要做的就是描述这根导线。

二、结构化描述法

第二种方法也很简单明了。

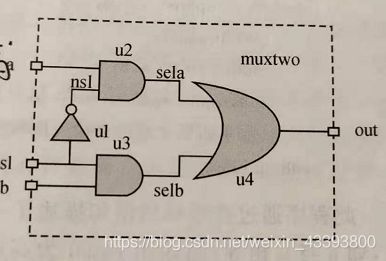

上图!

乍一看这张图和第一张图很像,但是不同的是,我们要将注意力放在门电路上,而不是导线上了。

module muxtwo(a,b,al,out);

input a,b,sl;

output out;

not u1(nsl,sl);//非门直接给了输出和输入两个参数

and #1 u2(sela,a,nsl);//与门

and #1 u3(selb,b,sl);

or #1 u4(out,sela,selb);//非门

endmodule

可以看到这种方法似乎更加直观。只需要将我们逻辑门电路填上输入输出就好了。

三、复杂电路小练习

上图是一个叫做"dog"的模块。已知mymux是一个二选一选择器。mytri是一个三态门。现在需要我们写一个dog模块以及dog的仿真模块。(dog的仿真模块信号要写全32种)

提示:三态门有2个输入1个输出。两个输入分别是enable和a。当enable=1时out才会输出a。

首先写出三态门的模块

module bufif1(out,in,enable);

output out;

input in,enable;

assign out=enable?in:'bz;

endmodule

module muxtwo(out,a,b,sl);

input a,b,sl;

output out;

reg out;

always @(sl or a or b)

if(!sl) out = a;

else out = b;

endmodule

module dog(ain,bin,enable1,enable2,select,outw);

input ain,bin,enable1,enable2,select;

output outw;

wire out1,out2;

bufif1 mybuf1(out1,ain,enable1);

bufif1 mybuf2(out2,bin,enable2);

muxtwo mymux(.out(outw),.a(out1),.b(out2),.sl(select));

endmodule

不难看出,我们在dog模块中调用了2次bufif1模块,1次muxtwo模块。而我们接下来要写的dogTestbench将要调用dog模块。

module t1;

reg ain,bin,select;

reg enable1,enable2;

wire outw;

initial

begin

select=0;

enable1=0;

enable2=0;

ain=0;

bin=0;

#100

select=0;

enable1=0;

enable2=0;

ain=0;

bin=1;

#100

select=0;

enable1=0;

enable2=0;

ain=1;

bin=0;

#100

select=0;

enable1=0;

enable2=0;

ain=1;

bin=1;

#100

select=0;

enable1=0;

enable2=1;

ain=0;

bin=0;

#100

select=0;

enable1=0;

enable2=1;

ain=0;

bin=1;

#100

select=0;

enable1=0;

enable2=1;

ain=1;

bin=0;

#100

select=0;

enable1=0;

enable2=1;

ain=1;

bin=1;

#100

select=0;

enable1=1;

enable2=0;

ain=0;

bin=0;

#100

select=0;

enable1=1;

enable2=0;

ain=0;

bin=1;

#100

select=0;

enable1=1;

enable2=0;

ain=1;

bin=0;

#100

select=0;

enable1=1;

enable2=0;

ain=1;

bin=1;

#100

select=0;

enable1=1;

enable2=1;

ain=0;

bin=0;

#100

select=0;

enable1=1;

enable2=1;

ain=0;

bin=1;

#100

select=0;

enable1=1;

enable2=1;

ain=1;

bin=0;

#100

select=0;

enable1=1;

enable2=1;

ain=1;

bin=1;

/16次

#100

select=1;

enable1=0;

enable2=0;

ain=0;

bin=0;

#100

select=1;

enable1=0;

enable2=0;

ain=0;

bin=1;

#100

select=1;

enable1=0;

enable2=0;

ain=1;

bin=0;

#100

select=1;

enable1=0;

enable2=0;

ain=1;

bin=1;

#100

select=1;

enable1=0;

enable2=1;

ain=0;

bin=0;

#100

select=1;

enable1=0;

enable2=1;

ain=0;

bin=1;

#100

select=1;

enable1=0;

enable2=1;

ain=1;

bin=0;

#100

select=1;

enable1=0;

enable2=1;

ain=1;

bin=1;

#100

select=1;

enable1=1;

enable2=0;

ain=0;

bin=0;

#100

select=1;

enable1=1;

enable2=0;

ain=0;

bin=1;

#100

select=1;

enable1=1;

enable2=0;

ain=1;

bin=0;

#100

select=1;

enable1=1;

enable2=0;

ain=1;

bin=1;

#100

select=1;

enable1=1;

enable2=1;

ain=0;

bin=0;

#100

select=1;

enable1=1;

enable2=1;

ain=0;

bin=1;

#100

select=1;

enable1=1;

enable2=1;

ain=1;

bin=0;

#100

select=1;

enable1=1;

enable2=1;

ain=1;

bin=1;

end

dog dog1(.outw(outw),.ain(ain),.bin(bin),.enable1(enable1),.enable2(enable2),.select(select));

endmodule

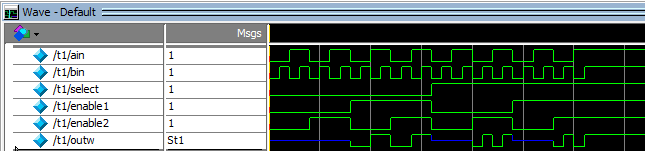

最后我们进行仿真

仿真的波形中outw只会有绿色和蓝色。如果出现了红色(不定值X)则代表你的程序写错了。

总结

今天我们学习了另外两种写法,以及做了一个小练习。希望大家已经理解了模块化的概念,因为接下来的实验我们都要围绕模块化呢!