运放的整理

目录

运放推荐书籍

电源抑制比单位1uV/V与dB的转换

为什么增益带宽积是常数

增益带宽积怎么用?

开环增益 差分增益 共模增益

运放与比较器的区别

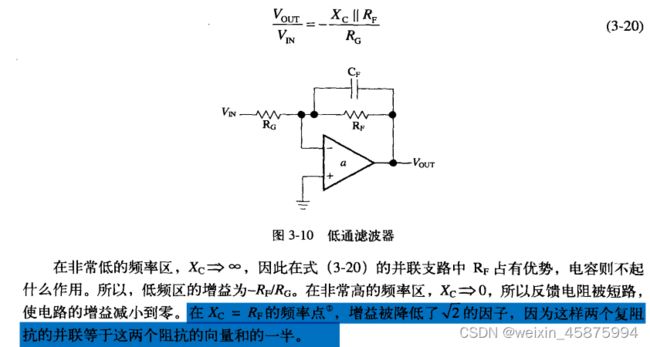

高通 低通

理想运放和理想运放条件

运算放大器指标

运放十坑

7.运放十坑之被遗忘的反馈电阻 (?)

8.运放十坑之失效的AD620

9.运放十坑之ADC的采样时间被运放拖累

10.运放十坑之被遗忘的功耗

运放在使用过程中需要注意的六大规则

1、注意输入电压是否超限

2、不要在运放输出直接并接电容

3、不要在放大电路反馈回路并接电容

4、注意运放的输出摆幅

5、注意反馈回路的Layout

6、要重视电源滤波

运放指标使用时的注意事项

运放参数带来的影响

如何降低运放电路中的电源噪声?

关于单/双电源运放应用

单电源----输入端偏置

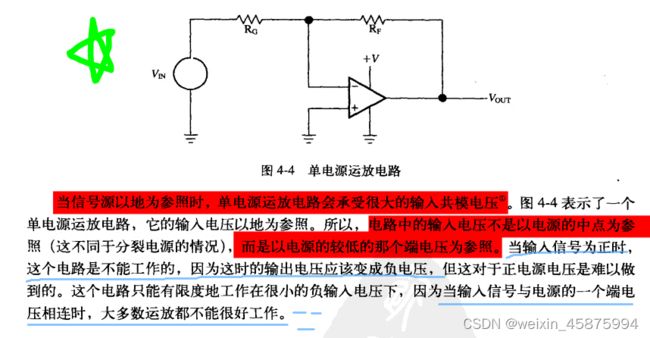

信号源以/不以地为参考时单双电源的运放

双电源运放具体的接法分几种情况

运算放大器中的虚短和虚断含意

使用运放构成电压跟随器的稳定性问题

微弱信号放大技巧

尺寸最小的比较器 运放

辨别运放和电压比较器

运放闭环开环

运放输出阻抗

振荡运放

运放自激振荡

1.运放振荡两个条件

2. 运放震荡判断方法

3. 消除自激的方法

相位补偿【滞后/ 超前补偿(环路内/外)】

注:此文为转载内容的归纳整理,尊重原创作者!

这本书太好看了!!必看!!!!拨开云雾见青天!!而且还会爱上运放的所有相关计算!!

第25章必看好吗?绝了!都是泪的教训啊!!!(增益范围&共模输入电压&未用运放的连接)

![]()

这篇更围绕ADC附属电路,与本文侧重点的内容不同:放大器应用.pdf运放参数选型电子版资源资料-嵌入式文档类资源-CSDN下载

--------------------

-------------------------------

----------------------------

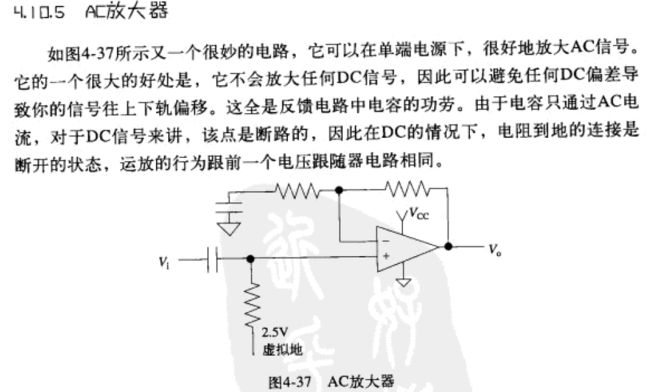

电源抑制比单位1uV/V与dB的转换

转换过程如下图:

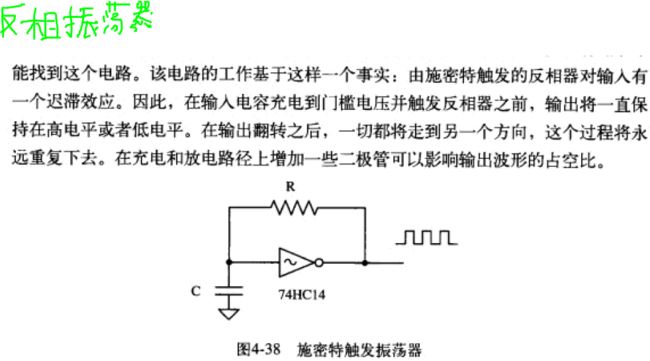

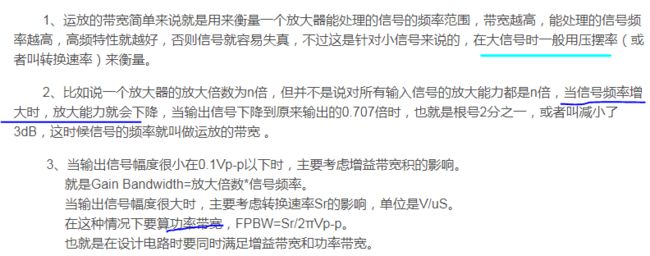

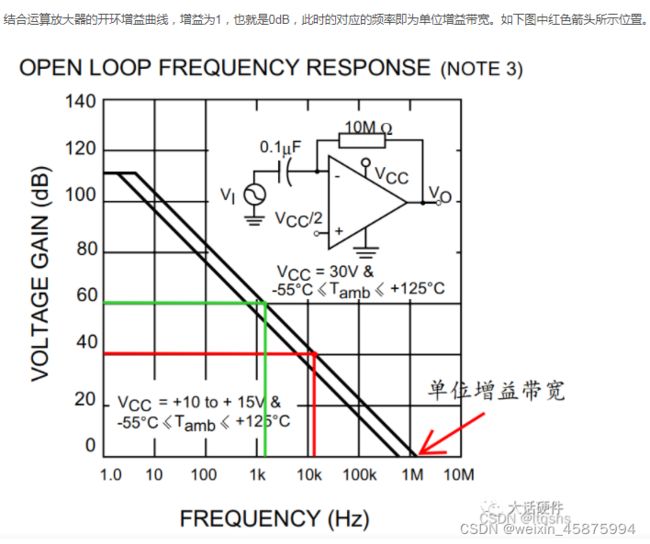

GBP增益带宽积

出处:

http://t.csdn.cn/Rm8nW

注:对于电压反馈运放,增益带宽积为常数。对于电流反馈运放,增益带宽积并无多大意义,因为在电流反馈运放中增益和带宽之间不存在线性关系。

实际一般需要根据开环增益曲线A(由供应商的数据手册提供)和1/F增益曲线(即噪声增益曲线,取决于反馈环路的设计)的交点判断,该交点决定了所能放大信号带宽,即闭环带宽fx。

http://t.csdn.cn/upPcK

————————————————

http://t.csdn.cn/LyGvO

并不是所有的运算放大器的GBW都能从开环增益曲线上这样直接计算。比如OPA820。。从手册中可以看出,增益带宽积是定值有限制条件,G>20,就是放大倍数要大于20倍GBW才是定值。

测试运放的单位增益带宽是将运放的闭环增益设定为1,将一个频率可变恒幅正弦小信号输入到运放的输入端,随着输入信号频率不断变大,输出信号增益将不断减小。当从运放的输出端测得闭环电压增益下降3db(或是相当于运放输入信号的0.707)时,所对应的信号频率乘以闭环放大倍数1所得的带宽,即为单位增益带宽。

为什么增益带宽积是常数呢?

(上面链接里有大佬证明这个结论的过程。)

单纯从开环曲线的角度理解就是,频率每增加10倍,增益降低10倍,因此总的增益和频率的乘积不变。一个变大10倍,一个降低10倍。有这样的结论的理论基础是运算放大器开环增益曲线在主极点后,增益以-20dB/dec下降。

增益带宽积怎么用?

如果电路设计是开环的,直接从开环增益曲线上找到增益对应的频率就可以解决问题,但是实际电路中运放都是处于闭环状态,那增益带宽积怎么和我们的设计联系起来呢?

假设我们要使用LM358设计一个放大倍数为10倍,增益为20dB的同相放大器。

详细见:http://t.csdn.cn/MqgGT

开环增益 差分增益 共模增益

什么是共模增益和差模增?_360问答

运算放大器在没有加(负)反馈时的增益(放大倍数取以十为底的对数再乘20,单位分贝),称为开环增益。运放加负反馈后,组成稳定的放大器。在放大器差动输入的两端加上极性相反大小相同的电压信号,放大器的增益称为差模增益。在放大器差动输入的两端加上极性相同大小相同的电压信号,放大器的增益称为共模增益。希望的是共模增益要小一些,因为共模信号往往是干扰信号。所以就有共模抑制比的问题。 运放是一种器件的统称。差模放大器是用运放加上负反馈后组成的放大电路,两者有联系,但不是一回事。

开环增益 线性:

运放跟随驱动问题 - 电路设计论坛 - 电子技术论坛 - 广受欢迎的专业电子论坛!

运放的SR(压摆率)和GBP(增益带宽积):

http://t.csdn.cn/maa82

用OP07做电压跟随器——增益带宽积怎么不可靠:

http://t.csdn.cn/nOTed

--------------------------------------------------------------

运放与比较器的区别

电压比较器 集成运放 区别?_360问答

1.最主要的区别是输出结构。比较器往往是集电极开路输出,这样可以多个比较器的输出并联,构成与门,这叫“线与”。而运放通常是推挽输出,输出端不能并联。

2.比较器的输出要加上拉电阻,运放的输出不需要加。

3.比较器工作在开环或者正反馈状态,一般不会自激。运放工作一般工作在负反馈状态,而开环或正反馈的时候需要加补偿电路,否则容易自激。

4.精密运放的开环增益很高,120dB左右。普通运放和比较器则不是很高,60dB左右。

5.运放工作一般工作在线性状态,内部结构决定了它非线性失真比较小。比较器工作在开关状态,如果用做线性放大的话,不能保证失真度。

----------------------------------------------------------

高通 低通

cr: ![]()

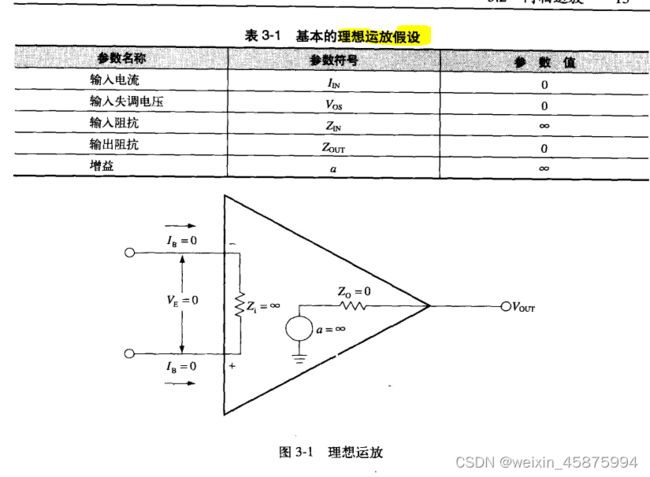

理想运放和理想运放条件

在分析和综合运放应用电路时,大多数情况下,可以将集成运放看成一个理想运算放大器。

理想运放各项技术指标具体如下:

1.开环差模电压放大倍数 Aod = ∞;

2.输入电阻 Rid = ∞;输出电阻 Rod =0

3.输入偏置电流 IB1=IB2=0 ;

4.失调电压 UIO、失调电流 IIO 、失调电压温漂、失调电流温漂均为零;

5.共模抑制比 CMRR = ∞;;

6.-3dB 带宽 fH = ∞ ;

7.无内部干扰和噪声。

实际运放的参数达到如下水平即可以按理想运放对待:

电压放大倍数达到 104~105 倍;输入电阻达到 105Ω;输出电阻小于几百欧姆;

外电路中的电流远大于偏置电流;失调电压、失调电流及其温漂很小,造电路的漂移在允许范围之内,电路的稳定性符合要求即可;输入最小信号时,有一定信噪比,共模抑制比大于等于 60dB;带宽符合电路带宽要求即可。

常用运放选型表完整来自:运放参数及选型表_Ammon_Zhang的博客-CSDN博客

运算放大器指标

————————————————

1.输入失调电压(VIO):输入失调电压,简称VIO,其定义是为使运算放大器输出端为0V(或接近0V)所需加于两输入端间之补偿电压。理想之运算放大器其VIO为0V,一般为毫伏级,此参数越小越好。反应了运放制造中电路的对称情况。

2.输入偏置电流(IIB):偏置电流 (bias current) 就是第一级放大器输入晶体管的基极直流电流的平均值。此参数越小越好。

3.输入失调电流(IIO):输入失调电流(input offset current)两输入端输入偏置电流之差的绝对值。该值也是越小越好。

4.差模输入电阻(RIN):输入电阻(input resistance )两输入端间差动输入电阻。该值是越大越好。

5.差模电压增益(AVD):也称为差动电压增益,是指输出电压的变化量与输入电压变化量的比值,即电压放大倍数。理想放大器的AV无限大,实际运放一般大于80dB。

6.共模电压增益(AVC):两输入端输入差模电压,输出电压的变化量与输入电压变化量之比。

7.最大输出电压(VOM):对于实际运算放大器,若振幅变大,则输出信号接近正、负电源电压进入饱和状态,出现失真。在出现失真之前的最大电压称为最大输出电压。

8.共模输入电压范围(VICM):这表示运算放大器两输入端与地之间能加的共模电压的范围。

9.共模抑制比(KCMR):差模电压增益AVD与共模电压增益AVC之比称为共模抑制比。可以表示为KCMR=20lg(AVD/AVC)dB。此值越大越好,但是会随着信号的频率升高而下降,一般都大于80dB。

10.电源电压抑制比(KSVR):运放的失调电压随电源的变化率称为电源电压抑制比。即输出信号受电源电压的影响程度。若电源变化△VS时失调电压变化量为△VIo,则KSVR定义为:KSVR=20lg(△VS/△VIo)dB。此值越大越好,较小时输出中出现电源噪声。

11.消耗电流(ICC):这是运算放大器电源端流通用的电流,随外加电路与电源电压的不同而变化。消耗电流越小越好,较大时放大器发热增加引起输出直流漂移增大。

12.转换速率(SR):若输入信号变化块,则输出跟不上输入的变化速度。SR是表示这种跟踪性能的参数。该值越大越好,但是该值高的运算放大器其他性能较差。

13.增益带宽乘积(GB):表示电压增益—频率特性的参数,单位为MHZ。(单位增益带宽)。

11.消耗电流(ICC):这是运算放大器电源端流通用的电流,随外加电路与电源电压的不同而变化。消耗电流越小越好,较大时放大器发热增加引起输出直流漂移增大。

12.转换速率(SR):若输入信号变化块,则输出跟不上输入的变化速度。SR是表示这种跟踪性能的参数。该值越大越好,但是该值高的运算放大器其他性能较差。

13.增益带宽乘积(GB):表示电压增益—频率特性的参数,单位为MHZ。(单位增益带宽)。

http://t.csdn.cn/X6G7l![]() http://t.csdn.cn/X6G7l————————————————

http://t.csdn.cn/X6G7l————————————————

输入失调电压 UIO

一个理想的集成运放,当输入电压为零时,输出电压也应为零(不加调零装置)。但实际上集成运放的差分输入级很难做到完全对称,通常在输入电压为零时,存在一定的输出电压。输入失调电压是指为了使输出电压为零而在输入端加的补偿电压。实际上是指输入电压为零时,将输出电压除以电压放大倍数,折算到输入端的数值称为输入失调电压,即 UIO 的大小反应了运放的对称程度和电位配合情况。UIO 越小越好,其量级在 2mV~20mV 之间,超低失调和低漂移运放的 UIO 一般在 1μV~20μV 之间 输入失调电流 IIO

当输出电压为零时,差分输入级的差分对管基极的静态电流之差称为输入失调电流 IIO

由于信号源内阻的存在,IIO 的变化会引起输入电压的变化,使运放输出电压不为零。IIO 愈小,输入级差分对管的对称程度越好,一般约为 1nA~0.1μA。 输入偏置电流 IIB

集成运放输出电压为零时,运放两个输入端静态偏置电流的平均值定义为输入偏置电流,

从使用角度来看,偏置电流小好,由于信号源内阻变化引起的输出电压变化也愈小,故输入偏置电流是重要的技术指标。一般 IIB 约为 1nA~0.1μA。

输入失调电压温漂△UIO/△T

输入失调电压温漂是指在规定工作温度范围内,输入失调电压随温度的变化量与温度变化量的比值。它是衡量电路温漂的重要指标,不能用外接调零装置的办法来补偿。输入失调电压温漂越小越好。一般的运放的输入失调电压温漂在±1mV/℃~±20mV/℃之间。

输入失调电流温漂 △IIO/△T

在规定工作温度范围内,输入失调电流随温度的变化量与温度变化量之比值称为输入失调电流温漂。输入失调电流温漂是放大电路电流漂移的量度,不能用外接调零装置来补偿。高质量的运放每度几个 pA。

最大差模输入电压 Uidmax

最大差模输入电压 Uidmax 是指运放两输入端能承受的最大差模输入电压。超过此电压,运放输入级对管将进入非线性区,而使运放的性能显著恶化,甚至造成损坏。根据工艺不同,Uidmax 约为±5V~±30V。

最大共模输入电压 Uicmax

最大共模输入电压 Uicmax 是指在保证运放正常工作条件下,运放所能承受的最大共模输入电压。共模电压超过此值时,输入差分对管的工作点进入非线性区,放大器失去共模抑制能力,共模抑制比显著下降。

最大共模输入电压 Uicmax 定义为,标称电源电压下将运放接成电压跟随器时,使输出电压产生 1%跟随误差的共模输入电压值;或定义为 下降 6dB 时所加的共模输入电压值。

开环差模电压放大倍数 Aud 是指集成运放工作在线性区、接入规定的负载,输出电压的变化量与运放输入端口处的输入电压的变化量之比。运放的 Aud 在 60~120dB 之间。不同功能的运放,Aud 相差悬殊。

差模输入电阻 Rid 是指输入差模信号时运放的输入电阻。Rid 越大,对信号源的影响越小,运放的输入电阻 Rid 一般都在几百千欧以上。

运放共模抑制比 KCMR 的定义与差分放大电路中的定义相同,是差模电压放大倍数与共模电压放大倍数之比,常用分贝数来表示。不同功能的运放,KCMR 也不相同,有的在 60~70dB 之间,有的高达 180dB。KCMR 越大,对共模干扰抑制能力越强。

开环带宽 BW

开环带宽又称-3dB 带宽,是指运算放大器的差模电压放大倍数 Aud 在高频段下降 3dB 所对应的频率 fH。

单位增益带宽 BWG 是指信号频率增加,使 Aud 下降到 1 时所对应的频率 fT,即 Aud 为 0dB 时的信号频率 fT。它是集成运放的重要参数。741 型运放的 fT=7Hz,是比较低的。

开环带宽:

开环带宽定义为,将一个恒幅正弦小信号输入到运放的输入端,从运放的输出端测得开环电压增益从运放的直流增益下降 3db(或是相当于运放的直流增益的 0.707)所对应的信号频率。这用于很小信号处理。

单位增益带宽 GB:

单位增益带宽定义为,运放的闭环增益为 1 倍条件下,将一个恒幅正弦小信号输入到运放的输入端,从运放的输出端测得闭环电 压增益下降 3db(或是相当于运放输入信号的 0.707)所对应的信号频率。单位增益带宽是一个很重要的指标,对于正弦小信号放大时,单位增益带宽等于输 入信号频率与该频率下的最大增益的乘积,换句话说,就是当知道要处理的信号频率和信号需要的增以后,可以计算出单位增益带宽,用以选择合适的运放。这用于 小信号处理中运放选型。

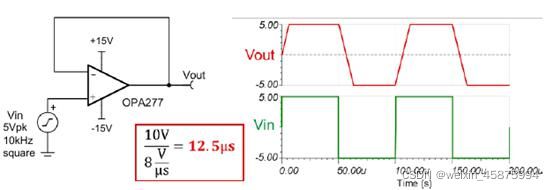

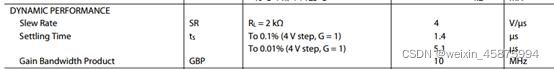

转换速率(也称为压摆率)SR:

是指放大电路在电压放大倍数等于 1 的条件下,输入大信号(例如阶跃信号)时,放大电路输出电压对时间的最大变化速率。它反映了运放对于快速变化的输入信号的响应能力。

运放转换速率定义为,运放接成闭环条件下,将一个大信号(含阶跃信号)输入到运放的输入端,从运放的输出 端测得运放的输出上升速率。由于在转换期间,运放的输入级处于开关状态,所以运放的反馈回路不起作用,也就是转换速率与闭环增益无关。转换速率对于大信号 处理是一个很重要的指标,对于一般运放转换速率 SR<=10V/μs,高速运放的转换速率 SR>10V/μs。目前的高速运放最高转换速率 SR 达到 6000V/μs。这用于大信号处理中运放选型。

转换速率 SR 是在大信号和高频信号工作时的一项重要指标,目前一般通用型运放压摆率在 1~10V/μs 左右。

全功率带宽 BW:

全功率带宽定义为,在额定的负载时,运放的闭环增益为 1 倍条件下,将一个恒幅正弦大信号输入到运放的输入端,使运放输出 幅度达到最大(允许一定失真)的信号频率。这个频率受到运放转换速率的限制。近似地,全功率带宽=转换速率 /2πVop(Vop 是运放的峰值输出幅度)。 全功率带宽是一个很重要的指标,用于大信号处理中运放选型。

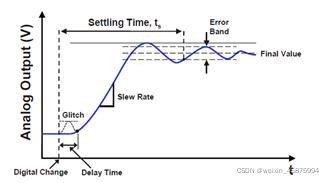

建立时间:

建立时间定义为,在额定的负载时,运放的闭环增益为 1 倍条件下,将一个阶跃大信号输入到运放的输入端,使运放输出由 0 增加到某 一给定值的所需要的时间。由于是阶跃大信号输入,输出信号达到给定值后会出现一定抖动,这个抖动时间称为稳定时间。稳定时间+上升时间=建立时间。对于不 同的输出精度,稳定时间有较大差别,精度越高,稳定时间越长。建立时间是一个很重要的指标,用于大信号处理中运放选型。

等效输入噪声电压:

等效输入噪声电压定义为,屏蔽良好、无信号输入的的运放,在其输出端产生的任何交流无规则的干扰电压。这个噪声电压折算到运放输入端时,就称为运放输入噪声电压(有时也用噪声电流表示)。对于宽带噪声,普通运放的输入噪声电压有效值约 10~20μV。

差模输入阻抗(也称为输入阻抗):

差模输入阻抗定义为,运放工作在线性区时,两输入端的电压变化量与对应的输入端电流变化量的比值。差模输 入阻抗包括输入电阻和输入电容,在低频时仅指输入电阻。一般产品也仅仅给出输入电阻。采用双极型晶体管做输入级的运放的输入电阻不大于 10 兆欧;场效应管 做输入级的运放的输入电阻一般大于 109 欧。

共模输入阻抗:

共模输入阻抗定义为,运放工作在输入信号时(即运放两输入端输入同一个信号),共模输入电压的变化量与对应的输入电流变化量之比。在低频情况下,它表现为共模电阻。通常,运放的共模输入阻抗比差模输入阻抗高很多,典型值在 108 欧以上。

输出阻抗:

输出阻抗定义为,运放工作在线性区时,在运放的输出端加信号电压,这个电压变化量与对应的电流变化量的比值。在低频时仅指运放的输出电阻。这个参数在开环测试。

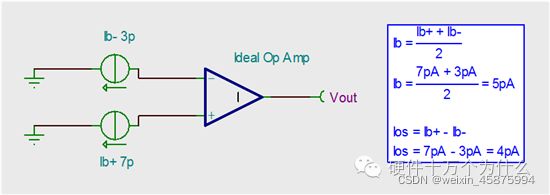

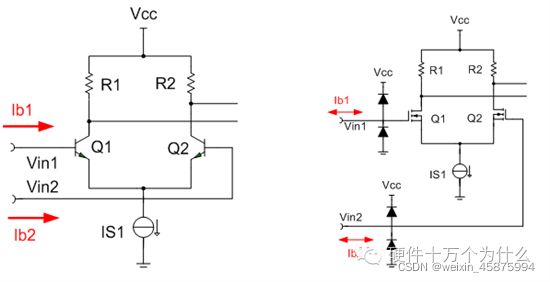

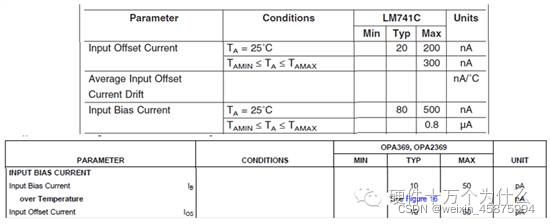

输入偏置电流和输入失调电流图解

只摘取了部分,完整版见出处:

z00143104的专栏_硬件十万个为什么_CSDN博客-华为研发模式系列,硬件开发领域博主

理想运放是没有输入偏置电流Ib和输入失调电流Ios .的。但每一颗实际运放都会有输入偏置电流Ib和输入失调电流Ios .

输入偏置电流Ib是由于运放两个输入极都有漏电流(我们暂且称之为漏电流)的存在。我们可以理解为,理想运放的各个输入端都串联进了一个电流源,这两个电流源的电流值一般为不相同。也就是说,实际的运入,会有电流流入或流出运放的输入端的(与理想运放的虚断不太一样)。那么输入偏置电流就定义这两个电流的平均值,这个很好理解。输入失调电流呢,就定义为两个电流的差。

说完定义,下面我们要深究一下这个电流的来源。那我们就要看一下运入的输入级了,运放的输入级一般采用差分输入(电压反馈运放)。采用的管子,要么是三级管bipolar,要么是场效应管FET。如下图所示,对于bipolar,要使其工作在线性区,就要给基极提供偏置电压,或者说要有比较大的基极电流,也就是常说的,三极管是电流控制器件。那么其偏置 电流就来源于输入级的三极管的基极电流,由于工艺上很难做到两个管子的完全匹配,所以这两个管子Q1和Q2的基极电流总是有这么点差别,也就是输入的失调电流。Bipolar输入的运放这两个值还是很可观的,也就是说是比较大的,进行电路设计时,不得不考虑的。而对于FET输入的运放,由于其是电压控制电流器件,可以说它的栅极电流是很小很小的,一般会在fA级,但不幸的是,它的每个输入引脚都有一对ESD保护二极管。这两个二极管都是有漏电流的,这个漏电流一般会比FET的栅极电流大的多,这也成为了FET输入运放的偏置电流的来源。当然,这两对ESD保护二极管也不可能完全一致,因此也就有了不同的漏电流,漏电流之差也就构成了输入失调电流的主要成份。

(自己加一点注释:三极管内各电流之间有确定的分配关系,即IC=βIB和IE=IC+IB。就是说,IC的大小主要由IB决定的,IB的大小变化决定了IC按比例增减,所以三极管是电流控制器件。我们利用三极管的电流控制作用来实现对信号幅值的放大和能量的转换,必须使其工作在输出特性的放大区,即发射结正向偏置,集电结反向偏置。)

下面列表中上表是bipolar的LM741的输入偏置电流和输入失调电流,这个电流流到外面电阻,即使是K欧级的,也会产生几十uV的失调电压,再经放大,很容易就会使输出的电压误差到mV级。下表则是CMOSFET的OPA369的输入偏置电流和输入失调电流,这两个值要小的多了,比较好的COMS运放输入偏置电流和输入失调电流的典型值可以做到小于1pA的目标。

这里还要强调的是,ESD的反向漏电流是与其反相电压有关的。因此当Vin=(Vcc-Vss)/2 时,加在两个ESD保护二极管的电压相当,他们的反向电流可以认为是近似相等的,此时理想情况是无电流流入或流出的,实际情况是电流达到最小值。因此这时有最小的偏置电流,当运放输入端电压Vin不等于(Vcc-Vss)/2,势必造成一个二极管的反向电压高,另一个低,此时两个二极管的反向漏电流就不等了,这个差电流就会构成了输入偏置电流的主要成份。这个现场称为领节效应。因此要使FET输入偏置电流最小,就要把共模电压设置在(Vcc-Vss)/2处。

上面分析了定义和来源。下面就要说说这两个参数对电路的影响了,输入偏置电流会流过外面的电阻网络,从而转化成运放的失调电压,再经运放话后就到了运入的输出端,造成了运放的输入误差。这也就说明了,在反向放大电路中,为什么要在运放的同相输入端连一个电阻再接地的原因。并且这个电阻要等于反向输入端的电阻和反馈电阻并联后的值。这就是为了使两个输入端偏置电流流过电阻时,形成的电压值相等,从而使它们引入的失调电压为0。这样说,太抽象了,还是看下面一组图容易理解一些。

再有一点,对于微小电流检测的电路,一般为跨阻放大电路,如光电二极管的探测电路,一般有用光信号都比较微弱转化的光电源信号更微弱,常常为nA级甚于pA级。这个电路的本意是想让光电流向反馈电阻流动从而在放大电路输出端产生出电压。如果选用的运放的输入偏置电流过大,刚这个微弱的光电流会有一部分流入到运放的输入端,而达不到预设的I/V线性转化。

许多运放的输入失调电流会随着温度的变化而变化,如果设计的系统是在很宽的温度范围内工作,这一因素不得不考虑。

运放十坑

(以下内容是摘取的部分,完整见出处)

轨到轨运放不是完全的可以使输出到达电源值,要使用的时候,还需要看负载和温度(影响导通电阻阻值)的关系来决定输出能达到多大电压。

2.运放十坑之不可忽略的输入偏置电流

运放正向输入端和反向输入端由于TVS漏电流和管子输入偏置电流,导致了两个输入端存在输入偏置电流(而且由于没有任何一个器件和另外一个器件一模一样,这两者输入偏置电流还不尽相同);这两个偏置电流会与外部电阻一起形成偏置电压后,输出到后端,形成误差。如果你不巧选择了一个基于BJT设计的运放,它具有较大的输入偏置电流,就会造成很大的后级误差。下面假设,两个输入端的输入偏置电流相同。

正反相输入偏置电流不尽相同,补偿只能减小失调电压,而正反相输入偏置电流差也称为失调电流。在进行高精度或小信号采样时,可以选用低失调电流运放,因为加入补偿电阻,也代入了一个新的噪声源,要慎重加入。

偏置电流是运放的主要误差之一,在之后的坑中,还会介绍一些影响后级的误差源。

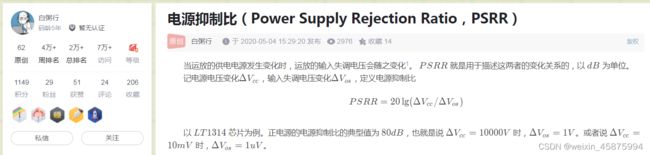

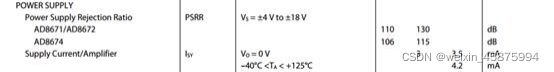

3.运放十坑之快速下降的PSRR

这个指标是指电源电压的直流变化,而不包括电源电压交流的变化(如纹波),在交流情况下,这个指标会发生非常大的恶化。Spec.里面提到的只是直流变化,交流变化在后面图示里面,一般情况下,非资深工程师对待图示都是滑滑地翻过去。

如果运放电路使用了开关电源,又没有把去耦、滤波做得很好的话,后级输入精度会受到极大的影响。

对于500kHz开关频率的纹波,PSRR+恶化到只有50dB,假设纹波大小为100mV,那么对于后级的影响恶化会达到0.3mV。对于很多小信号采集的应用来说,这个误差是不可接受的。因此,有些应用场景甚至会在运放电源入口做一个低通滤波(请注意电阻功耗和电阻热噪声)。

PSRR+ PSRR-介绍:一般地,PSRR 有 3个具体参数:+PSRR,-PSRR,+/-PSRR。表示从某个电源端或两个电源端分别或同时异向低频变化,在运放差分输入端引入的传输或影响量值。

4.运放十坑之乱加的补偿电容

以前有个“老工程师”对我说,反馈电路加个电容,电路就不会震荡。一看到“震荡”这么高大上的词语,我当场就懵逼了,以后所有的电路都并一个小电容,这样才professional。

直到一天,我要放大一个100kHz(运气很好,频率还没有太高,不然电压反馈运放都没法玩)的信号,也是按照经验并上一个电容,然后。。。信号再也没有正常。。。因为,并上了这个电容反馈阻抗对于100kHz的信号变成了只有不到200Ω,导致放大系数变化。

然,这还不是关键,问题在于:真的需要一个补偿电容吗?

首先,运放内部存在一个极点(把它想成就是RC低通造成的),它会造成相位的改变,最大到-90°:

如果再增加一个极点呢,它又会再次对相位进行改变,最大还可以增加到90°:

这样相位就到了-180°,这有什么问题呢?那就是“震荡”。

当某些频率点上的环路增益Aβ等于1,而相位为-180°的时候,这时,Vout/Vin会变成无穷大,电路就不稳定了。因此,当外部增加一个零点时,运放就会在某些频率点进入震荡。

这时,我们并上一个电容,相当于人为引入一个零点,把拉下去的相位,拉上来,但是,这个分布电容一般很小,使得它环路增益Aβ等于1的位置非常远,在这么远的频点上,运放早就不能正常工作了。而看手册这个运放自身在100k的时候,相位余量相当的高,超过了90°,完全不需要增加额外的补偿电容。

因此,对于具体情况,要具体分析,不能被“老工程师”带着跑了。

5.运放十坑之被冤枉的共模输入范围

以前遇到过一个问题,前级运放放大后,再由运放跟随进ADC,进ADC的信号是0.3V-1.5V。感觉是个很简单的电路,但是后面实测这颗工作电压为单电源5V的运放,有部分板卡在输出1.5V左右的时候,它的输出值并没有完全跟随到输入值,而低于比1.5V的信号,跟随都没问题,但是一旦接近就不对。当然,这个问题就上了硬件组的会议,最后讨论的结果是:“这个运放有问题,我们要找厂商嚎盘,但是我们是xx企业,别个又不得理我们,这样吧,我们换一个其它公司的运放”。不幸的是,我们冤枉了一颗运放,并且没有找到问题原因,幸运的是,在没有完全弄清原理的前提下,我们碰巧选到了一颗可以正常工作的运放。

运放共模输入范围是运放输入电压的一个区间,它表征的是运放能够线性工作的区间,即输入电压共模值在这个区间内,当输入电压发生变化时,输出电压能够线性的发生变化。

对于跟随电路,由于存在负反馈,基本上可认为正相输入端电压和负相输入端电压是同一个值,而这颗运放在5V供电时,它的共模输入范围是-0.1V至1.5V。因此,当输入电压在1.5V左右的时候,运放就存在不能正常线性跟随的情况。

为什么不能跟随呢?来看一个三极管放大电路,它也是运放的组成部分之一,来进行举例说明。

当输入的Vb发生变化时,Ie就会随着Vb发生相应的变化,从而引起Vc的变化,这就是跟随。若Vb继续增大到,使得Vc=Vcc-Ie x Rc计算值为负数的时候,而实际上Ie x Rc并不能超过Vcc,这时放大电路达到饱和甚至电流反相,导致输出电压固定或削峰或反向等。

6.运放十坑之不可忽略的压摆率

做1pps驱动电路,要求上升沿≤5ns,FPGA输出的信号用运放跟随增强驱动后,发现上升沿达不到要求。为什么呢?因为没有考虑到一个重要的指标,压摆率。压摆率是指:输入为阶跃信号时,闭环放大器的输出电压时间变化率的平均值。即输入一个理想的阶跃信号,输出会是一个带斜率信号,这个信号的爬升速率就是压摆率。

看一下这个运放的压摆率:

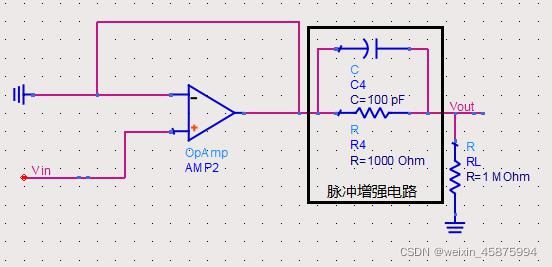

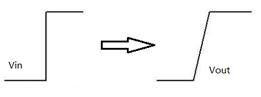

根本达不到要求啊,5ns只能爬升20mV,所以,上升沿根本达不到设计需求。怎么办呢?后期飞线增加了一个脉冲增强电路。

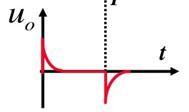

脉冲增强电路C4和R4,相当于一个微分电路C4和RL(当C x RL远小于压摆率时间)加一个直流电阻R4,使得负载RL上的信号边沿变得更加陡峭。分析一下:

a.电容C4与RL形成分压电路,根据下图的计算公式,C4上电压的变化率等于RL上的电压值。

b.那么假设电容电压变化率在0-τ范围内是几乎不变化的,那么负载RL上面的电压也是几乎不变的,一旦电容开始充电(电压发生变化),负载RL的电压就上升到顶点。记为波形1,如下图。

c.然后在电容充电结束后开始下落,为了解决没有变化率就没有电压的问题,增加一个直流电阻R4维持波形,它是一个直通波形,也就是原始波形,记为波形2。

d.两个波形合在一起后,由于波形1,波形2的上升沿得到极大增强,从而使得合成波形上升沿得以改善。

7.运放十坑之被遗忘的反馈电阻 (?)

为了扩大外部驱动能力,一般会在最后一级增加一个跟随电路,选择电流反馈运放-CFA增加运放的输出带宽。好简单哦,可惜你就是调不出来。还是先看图吧。好简单哦,可惜你就是调不出来。还是先看图吧。

什么电源轨、共模输入范围、增益积带宽、带载能力、压摆率。。。我全都考虑了啊,还是不对呢?

因为,CFA和VFA(电压反馈运放)不一样,读书时学的运放,基本上老师都是拿VFA进行举例和讲解。下图是CFA运放的模型:

它与VFA区别是,输入端不再是两个都虚断,反相输入电阻ZB是个非常小的值,但又绝对不能认为是零;它的开环增益Gout不再是非常大,而是约等于1;它的跨阻Z可以认为是无穷大。

当没有反馈电阻ZF的时候,A约等于1,ZF趋近于0,Aβ趋近于无穷,增益趋近于0,和想要的跟随电路完全不一样,也就是网上常说的“CFA不加反馈电阻就没信号”。(没找到这句话,忘记是在哪里看到的了,只能看下CFA手册上对反馈电阻的介绍)

因此,要增加一个反馈电阻,电路就会正常工作了。

PS:上面推导计算有技巧,只能从Aβ进行计算推导,因为CFA的计算前提是反相输入电阻ZB是个非常小的值;它的跨阻Z可以认为是无穷大,所以,要在求极限是找到一个单一变量,如果按照最终表达进行求极限,一个函数,三个变量(ZF趋近于0,ZB趋近于0,Z趋近于无穷),没法玩,如下图。

8.运放十坑之失效的AD620

采集4-20mA电流,得到1V-5V电压差,放大2倍后进入后级ADC。为了防止电阻功耗过高,R128,R129,R130三个电阻采用了并联取值的方式,最终取到了250Ω这个值。

分析一下,正相输入端2V-10V,符合器件输入范围(VCC-1.4V),反相输入端1V-5V,我加了负电,那更是符合了;然后看放大倍数2倍,Vmax=10V,也符合器件输出范围(VCC-1.4V);电源、放大倍数、去耦等等都没有问题。这是一个显得没有任何错误的原理图,但是实际上,它会在高输入电压值时发生错误。

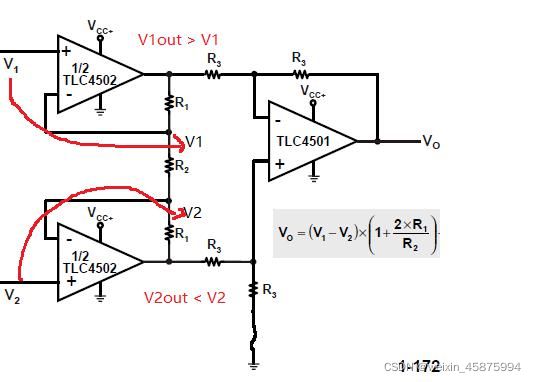

看下仪放的内部原理,就明白了(这里选一个手上有的资料,非AD620的内部原理,其实仪放原理都差不多)

正相输入电压和反相输入电压体现在仪放内部的R2处,而真正进行输出的电压,是由V1out和v2out体现的,换一句话说,最终增加的电压值平分为两份,一份由V1out提供,它会比V1高,另外一份由V2out提供,它会比V2低。

再看原理图,在20mA的时候,Vin+达到了10V,Vin-是5V,放大2倍,在仪放内部需要将Vin+放大到12.5V。这已经超过了仪放供电电压,因此,是绝对不可能正常工作的。

9.运放十坑之ADC的采样时间被运放拖累

ADC采集信号,信号稳定的时候,很准确;信号变化的时候,数据不稳定。当然了,ADC有采样时间,软件工程师也知道,他采了10次,只取后5次,但是数据还是有不稳定的状态。让硬件来看电路,硬件工程师说,电路当然没有问题了,全是从别人那里扣来的,怎么在我这就有问题了?

先看ADC的指标Tcycmin=500ns和Tacqmin=80ns,这是颗SAR型ADC,速度能上Mbps,还算挺快的。所以,它连续采样10次,所用时间也才10μs左右。

而运放从信号输入到输出,并不是一个无延时的过程,而是一个有延时还带震荡的过程,同时,这个过程的时间还会因为后级线路的PCB设计而增大。如下图:

看一下运放的指标,当4V时,达到0.01%,时间为5.1μs,此时带来的波动误差是0.4mV,而在4V范围内,一个16位ADC的1LSB为0.06mV。误差可以吃掉6,7个码字,如果再加上分布电容和走线电阻,这个时间会进一步增加,使得后级稳定时间增长,从而导致误差变得更加的大。

后来,软件工程师调低了采样率,增加了采集时间,问题得以解决。

10.运放十坑之被遗忘的功耗

做过一款板卡,功耗要求很严格,因此,设计完成后,就画了电源树,计算了每个器件的功耗,没有超,然后投版,调试,一上电,功耗超标。

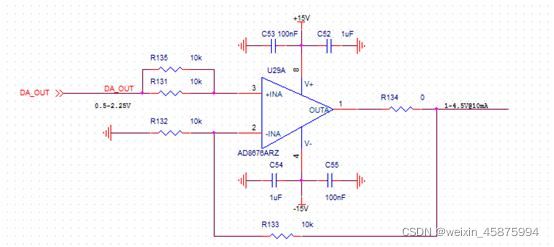

后面一检查,发现是运放功耗计算的时候出现了问题,下图这样的运放电路用了5个。

由于是直流驱动,在计算的时候,只考虑了运放本身的静态功耗,PD=15V x 4.2mA =63mW,按照最大静态功耗来考虑,功耗余量还绰绰有余。

实际上,忽略了一个重要的功率消耗点:运放供电电压15V到输出电压(1V-4.5V)之间的电压差,全部在运放里面消耗了,按照最大压差计算,一个电路就消耗140mW。这种耗散功率,以前从来没有考虑过,所以,全部都选择性的忽略了,当遇到功耗要求紧张的需求时,问题就暴露出来了。

后面改版的时候,选择了低电压给运放供电,减少了耗散功耗,满足了指标要求。

运放在使用过程中需要注意的六大规则

运算放大器使用规则(转)![]() https://www.cnblogs.com/AijunHe/p/6947607.html

https://www.cnblogs.com/AijunHe/p/6947607.html

1、注意输入电压是否超限

比如ADI的OP07数据表中的输入电气特性的一部分,可以看到在电源电压±15V的条件下,输入电压的范围是±13.5V,如果输入电压超出范围,那么运放就会工作不正常,出现一些意料不到的情况。

而有一些运放标注的不是输入电压范围,而是共模输入电压范围,比如TI的TLC2272数据表在单电源+5V的条件下,共模输入范围是0-3.5V.其实由于运放正常工作时,同相端和反相端输入电压基本是一致的(虚短虚断),所以“输入电压范围”与“共模输入电压范围”都是一样的意思。

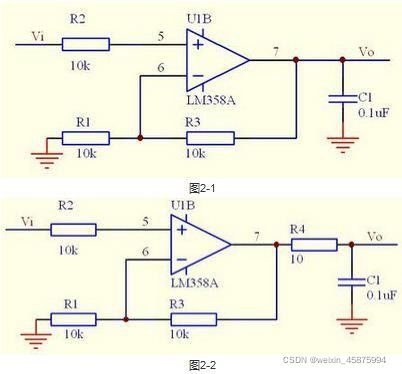

2、不要在运放输出直接并接电容

在直流信号放大电路中,有时候为了降低噪声,直接在运放输出并接去耦电容(如图2-1)。虽然放大的是直流信号,但是这样做是很不安全的。当有一个阶跃信号输入或者上电瞬间,运放输出电流会比较大,而且电容会改变环路的相位特性,导致电路自激振荡,这是我们不愿意看到的。

正确的去耦电容应该要组成RC电路,就是在运放的输出端先串入一个电阻,然后再并接去耦电容(如图2-2)。这样做可以大大削减运放输出瞬间电流,也不会影响环路的相位特性,可以避免振荡。

3、不要在放大电路反馈回路并接电容

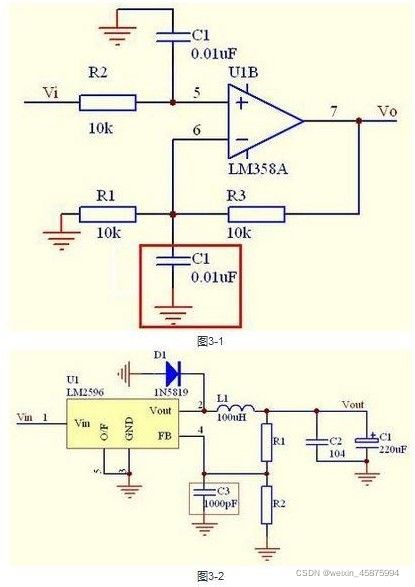

如图3-1所示,同样是一个用于直流信号放大的电路,为了去耦,不小心把电容并接到了反馈回路,反馈信号的相位发生了改变,很容易就会发生振荡。所以,在放大电路中,反馈回路不能加入任何影响信号相位的电路。由此延伸至稳压电源电路,如图3-2,并接在反馈脚的C3是错误的。为了降低纹波,可以把C3与R1并联,适当增大纹波的负反馈作用,抑制输出纹波。

4、注意运放的输出摆幅

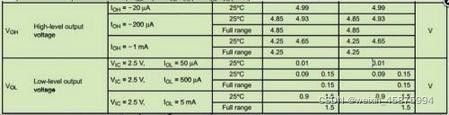

任何运放都不可能是理想运放,输出电压都不可能达到电源电压,一般基于MOS的运放都是轨对轨运放,在空载情况下输出可以达到电源电压,但是输出都会带一定的负载,负载越大,输出降落越多。基于三极管的运放输出幅度的相对值更小,有的运放输出幅度比电源电压要小2~6V,比如NE5532.图4-1就是TI的TLC2272在+5V供电的输出特性,它属于轨对轨运放,如果用该器件作为ADC采样的前级放大(如图4-2),单电源+5V供电,那么当输入接近0V的时候,输入和输出变得非线性的了。解决的方法是引入负电源,比如在4脚加入-1V的负电源,这样在整个输入范围内,输出与输入都是线性的了。

图4-1

5、注意反馈回路的Layout

反馈回路的元器件必须要靠近运放,而且PCB走线要尽量短,同时要尽量避开数字信号、晶振等干扰源。反馈回路的布局布线不合理,则会容易引入噪声,严重会导致自激振荡。

6、要重视电源滤波

运放的电源滤波不容忽视,电源的好坏直接影响输出。特别是对于高速运放,电源纹波对运放输出干扰很大,弄不好就会变成自激振荡。所以最好的运放滤波是在运放的电源脚旁边加一个0.1uF的去耦电容和一个几十uF的钽电容,或者再串接一个小电感或者磁珠,效果会更好。

————————————————

运放指标使用时的注意事项

1.在任何情况下,都要避免让运放工作在单位增益带宽附近(开环增益曲线和闭环增益曲线的相交点附近),在这些频率点处,运放的各项指标都会急剧恶化。留有100倍以上的裕量将使得放大器拥有更理想的增益精度。

2.平衡电阻的使用问题,在ti的最新工艺的一些器件中,如opa277,由于芯片内部已经有了Ib的补偿电路,这时这样的补偿方法就没有意义了,反而会引入额外的失调和噪声增益。

3.对于ti的被称为Zero-Drift技术的一些运放,比如opa335等,其Vos Drift仅仅为0.02uV/C,使用时就基本不用考虑温度对失调电压的影响了。

4.运放输入端的共模电压太高或者太低,运放的输入端就会关闭或者停止工作。比如opa690在5伏单电源工作的情况下

5.电流反馈型的运放没有增益带宽积的概念。

6.压摆率(Slew Rate),SR = 2π * f max* Vpp,由于压摆率的限制,会导致大信号条件下带宽不足的现象。因此,当我们把运放使用在大信号条件下,必须考虑运放的压摆率指标。

7.用运放做ADC的前级缓冲时,如果运放的建立时间(或上升时间,也是显示运放高速特性的重要参数,指当运放输入一个小信号的阶跃信号时,输出达到指定误差范围内为止的时间。通常误差都指定为到0.1%或0.01%)超过了ADC的采样时间,显然ADC采到的很难是我们所期望得到的值。可见,ADC的速度越高,对运放的建立时间也就越高。另一个例子是当运放不稳定时,输入阶跃或方波时在输出的上升沿会观察到大量的振铃和过冲,这会大大增加运放的建立时间,甚至导致运放不能正常工作。

8.CMRR(共模抑制比)当与频率对应的时候,随频率的增大而减小。

9.随着频率增大,PSRR的性能会急剧下降。所以在高精度的模拟电路中一般不会采用开关电源供电,因为他们虽然效率很高,但是会产生KHz量级的电源纹波噪声,对我们的高精度运放无疑是一个隐患,因此我们常用线性稳压器给高精度电路供电。

10.现代运放的电流噪声非常小,通常忽略不计

原文链接:TI运放使用指南一_yuechifanfan的博客-CSDN博客

运放参数带来的影响

CBM27AS8增益带宽更大,表示转换速率更快;

CBM27AS8的共模抑制比更大些,表示在电路中的抗干扰能力更强些;

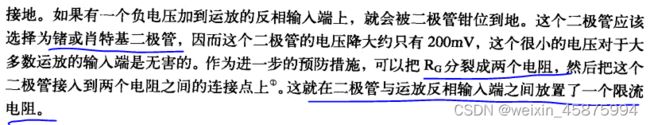

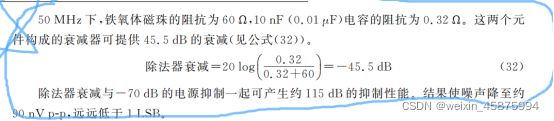

如何降低运放电路中的电源噪声?

(以下仅摘取部分,完整见出处:

如何降低运放电路中的电源噪声? - ADI 技术 - 电子技术论坛 - 广受欢迎的专业电子论坛!

将噪声定义为任何在运放输出端的无用信号。噪声可以是随机信号或重复信号,内部或外部产生,电压或电流形式,窄带或宽带,高频或低频。

噪声通常包括器件的固有噪声和外部噪声,固有噪声包括:热噪声、散弹噪声和低频噪声(1/f噪声)等,在这里我们不予讨论。外部的噪声通常指电源噪声、空间耦合干扰等,通常通过合理的设计可以避免或减小影响。降低外部噪声的影响对发挥低噪声运放的性能至关重要。

电源纹波

在全波整流的线性稳压供电的电路中,100Hz纹波是主要的电源噪声,对于运放电路,100Hz噪声电平通常要求控制在10nV-100nV(Rti)内,这取决于三个因素:运放在100Hz时的电源抑制比(PSRR),稳压器的纹波抑制比及稳压器的输入滤波电容的大小。

对电源纹波电压较大和要求运放输出精度较高的场合,选用对电源纹波抑制能力强且频率响应快的运放。

电源去耦

典型的串联稳压器供电的电源中包含有幅度为150UV,频率范围为100Hz-100KHz的噪声,开关型电源更严重,运放的PSRR在高频时以20dB/Decade的速度降低,通过在电源脚加RC或LC去耦网络,能滤除大部分噪声,应该注意负载电流的变化会导致对电源脚上电压的调制。

电源调整率

任何电源电压的变化都会引起运放输入偏置电流的变化,电源电压的变化是一个潜在的低频噪声源。在低噪声运放的应用中,降低电源的纹波和提高电源的调整率都很重要,电源调整率不足通常会引起讨厌的低频噪声。

开关电源

开关电源是一个很严重的噪声源,噪声频谱既包含开关频率及其谐波成分,还包含开关回路谐振引起的阻尼振荡的高频成分,从几十KHz一直延续到几十MHz,而普通的运放在几百Hz以上时PSRR开始急剧下降,到几百KHz时几乎为零,此时,出现在输出端的电源噪声将很严重

影响途径和对策

除了注意对运放PSRR或CMRR参数的选择和加强运放供电去耦(如采用RC去耦)外,在开关电源供电设计中,还应注意如下一些方面:

电源中的噪声可能通过基准源或PCB的漏电直接耦合到放大器的输入端。要注意对电压基准源输出的滤波,对于PCB漏电,可在信号输入引线与电源走线间加地线防护。

噪声可能通过PCB走线之间的分布电容直接耦合到放大器输入端,造成干扰。在PCB布线时,要注意电源线与弱信号线不要贴近平行走线,线净距大于线宽的3倍(3W原则),并在电源线或数字信号线与模拟小信号线之间加地线隔离。

接地处理不当,噪声通过公共阻抗影响敏感电路部分。为了防止公共阻抗将电源噪声引入信号回路,要注意如下几点:接地上避免带噪声的大电流流过前级小信号地;单点接地,电源、模拟、数字电路分开接地;布板使用地平面层,最小化地线阻抗;开关电源输出从最后一个滤波电容的地端引出电源地,避免从滤波电感前的电容的地端引出。

开关管漏极开关电压驱动的位移电流,通过初次级分布电容,次级电路,次级对大地与杂散电容,大地与初级地之间的杂散电容形成环路,次级模拟电路中流过的共模电流流过不平衡的阻抗转换成差模,对放大电路造成干扰(如图6)。共模方式引入的干扰一般为开关噪声中的高频分量(数MHz以上)。措施主要有如下三点:提供一条从开关电源次级地返回初级地的低阻抗噪声旁路通道,通常使用1000p~2200p的安规电容;使用共模扼流圈加强开关电源的输出的共模滤波;使用隔离技术,最小化回路中的共模电流。

通过空间磁场耦合到具有一定环路面积的信号回路或地线环中,造成对信号的影响。另外来自开关电源或市电网络的高频干扰可能通过空间杂散电容直接耦合到信号回路。设计中的考虑包括:合理的布局、调整电感线圈或变压器放置方向、优化布线,减小关键信号的回路面积,避免形成地环路可以减小干扰;双面或单面板布线,注意信号线和地线,电源线与地线一定要贴近平行走线;使用1000p电容射频多点接地,可以兼顾EMC和低频信噪比的需求;对敏感电路加屏蔽,注意屏蔽层连接到被保护信号的参考地;走线设计上注意电源线不要和信号线捆扎在一起。

小结

在运放电路设计中降低电源噪声的主要措施包括:

通过去耦、滤波等措施降低电源输出的纹波和噪声成分。

改善设计,提高电源电压调整率。

合理电路结构、考究的PCB布线、合理的走线工艺。

选择在敏感噪声频段的PSRR或CMRR较高的器件。

运放应用电路图及计算过程

第六章第一节集成运放应用电路组成原理(课件) - 豆丁网

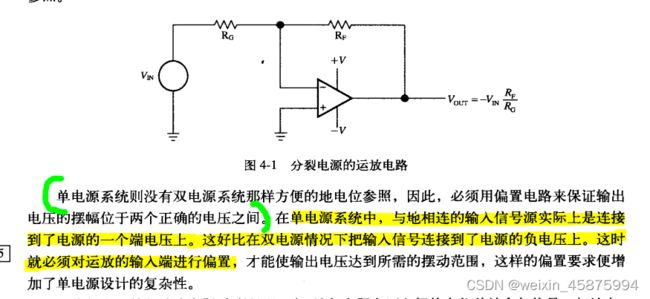

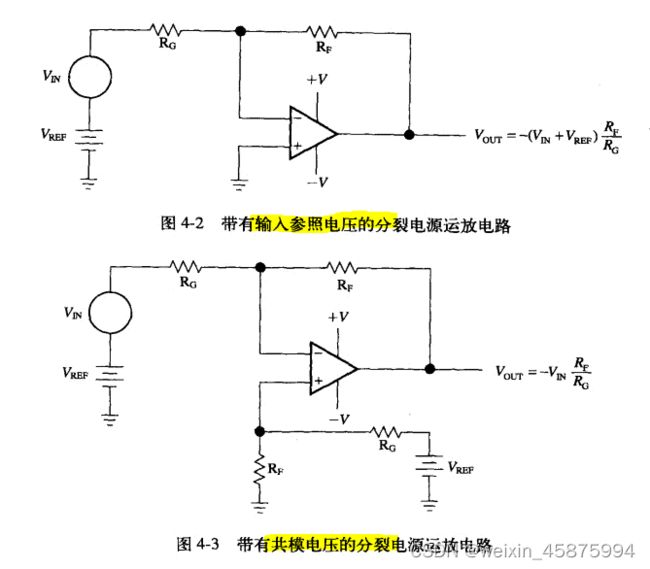

我们经常看到很多非常经典的运算放大器应用图集,但是这些应用都建立在双电源的基础上,很多时候,电路的设计者必须用单电源供电,但是他们不知道该如何将双电源的电路转换成单电源电路。

在设计单电源电路时需要比双电源电路更加小心。

关于单/双电源运放应用

双电源或称分裂电源

单电源----输入端偏置

cr:运算放大器权威指南第三版 P37

信号源以/不以地为参考时单双电源的运放

cr:运算放大器权威指南第三版 P37

单电源供电时,输入负电压,输出只能饱和在电源较低的端电压上

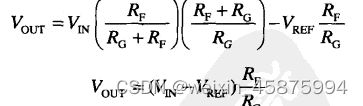

范例一

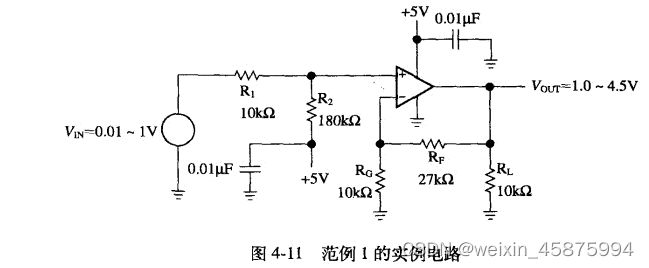

范例三

???????

原文链接:硬件十万个为什么——运放篇(十一)关于单电源运放应用_z00143104的专栏-CSDN博客![]() https://blog.csdn.net/z00143104/article/details/48133171

https://blog.csdn.net/z00143104/article/details/48133171

问:如果输入信号以系统地为参考,必须加电容耦合吗?我实际测试,无论是正,反相输入,运算都不工作。

答:电容耦合是隔离直流分量的,不工作可能是没有静态工作点造成的。交流信号放大电路或音频放大电路中,也可采用电源偏置电路,将静态直流输出电压降为电源电压的一半,基于单电源工作,但输入和输出信号都需要加交流耦合电容。

一般运放以双电源工作时是以((V+)+(V-))/2=0V作为参考电压的,运放工作在中间的线性区。运放若以单电源供电,仍应当将电压参考点设置在((V+)- 0V)/2=(V+)/2处。若是反相放大器,应当将同相输入端的参考电压设为V+/2,反相输入端的输入信号也应当以V+/2作为参考点。当输入信号接近0V或V+时,会使运放工作在非线性区,放大器输出会出现饱和失真或截止失真。

————————————————

另一篇:

在实际应用中,这两种运放都能采用单电源、双电源的供电模式。具体使用方式如下:

1:在放大直流信号时,如果采用双电源运放,则最好选择正负双电源供电,否则输入信号幅度较小时,可能无法正常工作;如果采用单电源运放,则单电源供电或双电源供电都可以正常工作;

2:

3:在放大交流信号时,无论是单电源运放还是双电源运放,简单的采用单电源供电都无法正常工作,对于单电源运放,表现为无法对信号的负半周放大,而双电源运放无法正常工作。要采用单电源,就需要所谓的“偏置”。而偏置的结果是把供电所采用的单电源相对的变成“双电源”。

双电源是由一个正电源和一个相等的负电源组成,一般是正负15伏,正负12伏,正负 5伏,输入和输出电压都是参考地给出的,一般教课书中的涉及到的运放都采用的是这种双电源的供电方法,但是在一些实际生产设计中没有或者只能采用单电源的供电的方法时,就有必要采取相应的解决方法。 单电源供电时,正电源接Vcc,电源地接公共地,并需要将正电压Vcc的一半电压Vcc/2作为虚地接到运放的同相输入端,一般也会在中间加个电阻 VCCVCC/2在此基础上,我们再按照要求设计出相应的运放电路,接通电源后,单电源供电就会正常工作 Vcc/2 可以通过电阻分压的形式从正电压Vcc出得到,但是这个可能会降低运放的低频特性。

大部分运算放大器要求双电源(正负电源)供电,只有少部分运算放大器可以在单电源供电状态下工作,如LM358(双运放)、LM324(四运放)、CA3140(单运放)等。需要说明的是,单电源供电的运算放大器不仅可以在单电源条件下工作,也可在双电源供电状态下工作。例如,LM324可以在、+5~+12V单电源供电状态下工作,也可以在+5~±12V双电源供电状态下工作。

双电源运放具体的接法分几种情况

电路按照单电源供电设计时,地线按照要求接电源正或负极,运放电源端分别接电源正和负极,信号输入和输出对地进行;

电路按照双电源供电设计使用,运放地端接电源地,运放电源端分别接电源正和负极,信号输入和输出对地进行;

信号输入和输出存在悬浮,需要对回路另外设计。双电源运在双电源供电情况使用时,双电源要有正常的地线,电源正电压和负电压尽量一致,滤波良好。

学霸带你飞 | 这些运放基本电路全解析,了解一下-模拟/电源-与非网

1.1 电源供电和单电源供电

所有的运算放大器都有两个电源引脚,一般在资料中,它们的标识是 VCC+和 VCC-,但是有些时候它们的标识是 VCC+和 GND。这是因为有些数据手册的作者企图将这种标识的差异作为单电源运放和双电源运放的区别。但是,这并不是说他们就一定要那样使用――他们可能可以工作在其他的电压下。在运放不是按默认电压供电的时候,需要参考运放的数据手册,特别是绝对最大供电电压和电压摆动说明。

绝大多数的模拟电路设计者都知道怎么在双电源电压的条件下使用运算放大器,比如图一左边的那个电路,一个双电源是由一个正电源和一个相等电压的负电源组成。一般是正负 15V,正负 12V 和正负 5V 也是经常使用的。输入电压和输出电压都是参考地给出的,还包括正负电压的摆动幅度极限 Vom 以及最大输出摆幅。

单电源供电的电路(图一中右)运放的电源脚连接到正电源和地。正电源引脚接到 VCC+,地或者 VCC-引脚连接到 GND。将正电压分成一半后的电压作为虚地接到运放的输入引脚上,这时运放的输出电压也是该虚地电压,运放的输出电压以虚地为中心,摆幅在 Vom 之内。

有一些新的运放有两个不同的最高输出电压和最低输出电压。这种运放的数据手册中会特别分别指明 Voh 和 Vol 。需要特别注意的是有不少的设计者会很随意的用虚地来参考输入电压和输出电压,但在大部分应用中,输入和输出是参考电源地的,所以设计者必须在输入和输出的地方加入隔直电容,用来隔离虚地和地之间的直流电压。(参见 1.3 节)

通常单电源供电的电压一般是 5V,这时运放的输出电压摆幅会更低。另外现在运放的供电电压也可以是 3V 也或者会更低。出于这个原因在单电源供电的电路中使用的运放基本上都是 Rail-To-Rail 的运放,这样就消除了丢失的动态范围。

需要特别指出的是输入和输出不一定都能够承受 Rail-To-Rail 的电压。虽然器件被指明是轨至轨(Rail-To-Rail)的,如果运放的输出或者输入不支持轨至轨,接近输入或者接近输出电压极限的电压可能会使运放的功能退化,所以需要仔细的参考数据手册是否输入和输出是否都是轨至轨。这样才能保证系统的功能不会退化,这是设计者的义务。

1. 2 虚地

单电源工作的运放需要外部提供一个虚地,通常情况下,这个电压是 VCC/2,图二的电路可以用来产生 VCC/2 的电压,但是他会降低系统的低频特性。

R1 和 R2 是等值的,通过电源允许的消耗和允许的噪声来选择,电容 C1 是一个低通滤波器,用来减少从电源上传来的噪声。在有些应用中可以忽略缓冲运放。

在下文中,有一些电路的虚地必须要由两个电阻产生,但是其实这并不是完美的方法。在这些例子中,电阻值都大于 100K,当这种情况发生时,电路图中均有注明。

1. 3 交流耦合 ?????????

虚地是大于电源地的直流电平,这是一个小的、局部的地电平,这样就产生了一个电势问题:输入和输出电压一般都是参考电源地的,如果直接将信号源的输出接到运放的输入端,这将会产生不可接受的直流偏移。如果发生这样的事情,运放将不能正确的响应输入电压,因为这将使信号超出运放允许的输入或者输出范围。

解决这个问题的方法将信号源和运放之间用交流耦合。使用这种方法,输入和输出器件就都可以参考系统地,并且运放电路可以参考虚地。当不止一个运放被使用时,如果碰到以下条件级间的耦合电容就不是一定要使用:第一级运放的参考地是虚地第二级运放的参考第也是虚地这两级运放的每一级都没有增益。任何直流偏置在任何一级中都将被乘以增益,并且可能使得电路超出它的正常工作电压范围。

如果有任何疑问,装配一台有耦合电容的原型,然后每次取走其中的一个,观察电工作是否正常。除非输入和输出都是参考虚地的,否则这里就必须要有耦合电容来隔离信号源和运放输入以及运放输出和负载。一个好的解决办法是断开输入和输出,然后在所有运放的两个输入脚和运放的输出脚上检查直流电压。所有的电压都必须非常接近虚地的电压,如果不是,前级的输出就就必须要用电容做隔离。(或者电路有问题)

1. 4 组合运放电路

在一些应用中,组合运放可以用来节省成本和板上的空间,但是不可避免的引起相互之间的耦合,可以影响到滤波、直流偏置、噪声和其他电路特性。设计者通常从独立的功能原型开始设计,比如放大、直流偏置、滤波等等。在对每个单元模块进行校验后将他们联合起来。除非特别说明,否则本文中的所有滤波器单元的增益都是 1。

1. 5 选择电阻和电容的值

每一个刚开始做模拟设计的人都想知道如何选择元件的参数。电阻是应该用 1 欧的还是应该用 1 兆欧的?一般的来说普通的应用中阻值在 K 欧级到 100K 欧级是比较合适的。高速的应用中阻值在 100 欧级到 1K 欧级,但他们会增大电源的消耗。便携设计中阻值在 1 兆级到 10 兆欧级,但是他们将增大系统的噪声。用来选择调整电路参数的电阻电容值的基本方程在每张图中都已经给出。如果做滤波器,电阻的精度要选择 1% E -96 系列(参看附录 A)。一但电阻值的数量级确定了,选择标准的 E-12 系列电容。

用 E-24 系列电容用来做参数的调整,但是应该尽量不用。用来做电路参数调整的电容不应该用 5%的,应该用 1%。

2.1 放大

放大电路有两个基本类型:同相放大器和反相放大器。他们的交流耦合版本如图三所示。对于交流电路,反向的意思是相角被移动 180 度。这种电路采用了耦合电容 ――Cin 。Cin 被用来阻止电路产生直流放大,这样电路就只会对交流产生放大作用。如果在直流电路中,Cin 被省略,那么就必须对直流放大进行计算。

在高频电路中,不要违反运放的带宽限制,这是非常重要的。实际应用中,一级放大电路的增益通常是 100 倍(40dB),再高的放大倍数将引起电路的振荡,除非在布板的时候就非常注意。如果要得到一个放大倍数比较的大放大器,用两个等增益的运放或者多个等增益运放比用一个运放的效果要好的多。

2.2 衰减

传统的用运算放大器组成的反相衰减器如图四所示。

图六中同相的衰减器可以用作电压衰减和同相缓冲器使用。

2.3 加法器

图七是一个反相加法器,他是一个基本的音频混合器。但是该电路的很少用于真正的音频混合器。因为这会逼近运放的工作极限,实际上我们推荐用提高电源电压的办法来提高动态范围。

同相加法器是可以实现的,但是是不被推荐的。因为信号源的阻抗将会影响电路的增益。

2.4 减法器

就像加法器一样,图八是一个减法器。一个通常的应用就是用于去除立体声磁带中的原唱而留下伴音(在录制时两通道中的原唱电平是一样的,但是伴音是略有不同的)。

2.5 模拟电感

图九的电路是一个对电容进行反向操作的电路,它用来模拟电感。电感会抵制电流的变化,所以当一个直流电平加到电感上时电流的上升是一个缓慢的过程,并且电感中电阻上的压降就显得尤为重要。

电感会更加容易的让低频通过它,它的特性正好和电容相反,一个理想的电感是没有电阻的,它可以让直流电没有任何限制的通过,对频率是无穷大的信号有无穷大的阻抗。

如果直流电压突然通过电阻 R1 加到运放的反相输入端上的时候,运放的输出将不会有任何的变化,因为这个电压同过电容 C1 也同样加到了正相输出端上,运放的输出端表现出了很高的阻抗,就像一个真正的电感一样。

随着电容 C1 不断的通过电阻 R2 进行充电,R2 上电压不断下降,运放通过电阻 R1 汲取电流。随着电容不断的充电,最后运放的两个输入脚和输出脚上的电压最终趋向于虚地(Vcc/2)。

当电容 C1 完全被充满时,电阻 R1 限制了流过的电流,这就表现出一个串连在电感中电阻。这个串连的电阻就限制了电感的 Q 值。真正电感的直流电阻一般会比模拟的电感小的多。这有一些模拟电感的限制:

电感的一段连接在虚地上;

模拟电感的 Q 值无法做的很高,取决于串连的电阻 R1;

模拟电感并不像真正的电感一样可以储存能量,真正的电感由于磁场的作用可以引起很高的反相尖峰电压,但是模拟电感的电压受限于运放输出电压的摆幅,所以响应的脉冲受限于电压的摆幅。

2.6 仪用放大器

仪用放大器用于需要对小电平信号直流信号进行放大的场合,他是由减法器拓扑而来的。仪用放大器利用了同相输入端高阻抗的优势。基本的仪用放大器如图十所示。

这个电路是基本的仪用放大电路,其他的仪用放大器也如图中所示,这里的输入端也使用了单电源供电。这个电路实际上是一个单电源的应变仪。这个电路的缺点是需要完全相等的电阻,否则这个电路的共模抑制比将会很低。

这个电路的增益非常好计算。但是这个电路也有一个缺点:那就是电路中的两个电阻必须一起更换,而且他们必须是等值的。另外还有一个缺点,第一级的运放没有产生任何有用的增益。

这节非常深入地介绍了用运放组成的有源滤波器。在很多情况中,为了阻挡由于虚地引起的直流电平,在运放的输入端串入了电容。这个电容实际上是一个高通滤波器,在某种意义上说,像这样的单电源运放电路都有这样的电容。设计者必须确定这个电容的容量必须要比电路中的其他电容器的容量大 100 倍以上。这样才可以保证电路的幅频特性不会受到这个输入电容的影响。如果这个滤波器同时还有放大作用,这个电容的容量最好是电路中其他电容容量的 1000 倍以上。如果输入的信号早就包含了 VCC/2 的直流偏置,这个电容就可以省略。

这些电路的输出都包含了 VCC/2 的直流偏置,如果电路是最后一级,那么就必须串入输出电容。

这里有一个有关滤波器设计的协定,这里的滤波器均采用单电源供电的运放组成。滤波器的实现很简单,但是以下几点设计者必须注意:

1. 滤波器的拐点(中心)频率

2. 滤波器电路的增益

3. 带通滤波器和带阻滤波器的的 Q 值

4. 低通和高通滤波器的类型(Butterworth 、Chebyshev、Bessell)

不幸的是要得到一个完全理想的滤波器是无法用一个运放组成的。即使可能,由于各个元件之间的负杂互感而导致设计者要用非常复杂的计算才能完成滤波器的设计。通常对波形的控制要求越复杂就意味者需要更多的运放,这将根据设计者可以接受的最大畸变来决定。或者可以通过几次实验而最终确定下来。如果设计者希望用最少的元件来实现滤波器,那么就别无选择,只能使用传统的滤波器,通过计算就可以得到了。

3.1 一阶滤波器

一阶滤波器是最简单的电路,他们有 20dB 每倍频的幅频特性

3.1.1 低通滤波器

3.1.2 高通滤波器

3.1.3 文氏滤波器

文氏滤波器对所有的频率都有相同的增益,但是它可以改变信号的相角,同时也用来做相角修正电路。

3.2 二阶滤波器

二阶滤波电路一般用他们的发明者命名。他们中的少数几个至今还在使用。有一些二阶滤波器的拓扑结构可以组成低通、高通、带通、带阻滤波器,有些则不行。

二阶滤波器有 40dB 每倍频的幅频特性。

3.2.1 Sallen-Key 滤波器

Sallen-Key 滤波器是一种流行的、广泛应用的二阶滤波器。他的成本很低,仅需要一个运放和四个无源器件组成。但是换成 Butterworth 或 Chebyshev 滤波器就不可能这么容易的调整了。 这个电路是一个单位增益的电路,改变 Sallen-Key 滤波器的增益同时就改变了滤波器的幅频特性和类型。实际上 Sallen-Key 滤波器就是增益为 1 的 Butterworth 滤波器。

3.2.2 多反馈滤波器

多反馈滤波器是一种通用,低成本以及容易实现的滤波器。不幸的是,设计时的计算有些复杂,在这里不作深入的介绍。

3.2.3 双 T 滤波器

双 T 滤波器既可以用一个运放也可仪用两个运放实现。他是建立在三个电阻和三个电容组成的无源网络上的。这六个元件的匹配是临界的,但幸运的是这仍是一个常容易的过程,这个网络可以用同一值的电阻和同一值的电容组成。用图中的公式就可以同时的将 R3 和 C3 计算出来。应该尽量选用同一批的元件,他们有非常相近的特性。

3.2.3.1 单运放实现

如果用参数非常接近的元件组成带通滤波器,就很容易发生振荡。接到虚地的电阻最好在 E-96 1%系列中选择,这样就可以破坏振荡条件。

3.2.3.2 双运放实现

运算放大器(Operational Amplifier,简称 OP、OPA、OPAMP)是一种直流耦合﹐差模(差动模式)输入、通常为单端输出(Differential-in, single-ended output)的高增益(gain)电压放大器,因为刚开始主要用于加法,乘法等运算电路中,因而得名。一个理想的运算放大器必须具备下列特性:无限大的输入阻抗、等于零的输出阻抗、无限大的开回路增益、无限大的共模排斥比的部分、无限大的频宽。最基本的运算放大器如图 1-1。一个运算放大器模组一般包括一个正输入端(OP_P)、一个负输入端(OP_N)和一个输出端(OP_O)。

通常使用运算放大器时,会将其输出端与其反相输入端(inverting input node)连接,形成一负反馈(negative feedback)组态。原因是运算放大器的电压增益非常大,范围从数百至数万倍不等,使用负反馈方可保证电路的稳定运作。但是这并不代表运算放大器不能连接成正回馈(positive feedback),相反地,在很多需要产生震荡讯号的系统中,正回馈组态的运算放大器是很常见的组成元件。

闭环负反馈

将运算放大器的反向输入端与输出端连接起来,放大器电路就处在负反馈组态的状况,此时通常可以将电路简单地称为闭环放大器。闭环放大器依据输入讯号进入放大器的端点,又可分为反相(inverting)放大器与非反相(non-inverting)放大器两种。

闭环正回馈

将运算放大器的正向输入端与输出端连接起来,放大器电路就处在正回馈的状况,由于正回馈组态工作于一极不稳定的状态,多应用于需要产生震荡讯号的应用中。

运算放大器中的虚短和虚断含意

理想运放工作在线性区时可以得出二条重要的结论:

虚短

因为理想运放的电压放大倍数很大,而运放工作在线性区,是一个线性放大电路,输出电压不超出线性范围(即有限值),所以,运算放大器同相输入端与反相输入端的电位十分接近相等。在运放供电电压为±15V 时,输出的最大值一般在 10~13V。所以运放两输入端的电压差,在 1mV 以下,近似两输入端短路。这一特性称为虚短,显然这不是真正的短路,只是分析电路时在允许误差范围之内的合理近似。

虚断

由于运放的输入电阻一般都在几百千欧以上,流入运放同相输入端和反相输入端中的电流十分微小,比外电路中的电流小几个数量级,流入运放的电流往往可以忽略,这相当运放的输入端开路,这一特性称为虚断。显然,运放的输入端不能真正开路。

运用“虚短”、“虚断”这两个概念,在分析运放线性应用电路时,可以简化应用电路的分析过程。运算放大器构成的运算电路均要求输入与输出之间满足一定的函数关系,因此均可应用这两条结论。如果运放不在线性区工作,也就没有“虚短”、“虚断”的特性。如果测量运放两输入端的电位,达到几毫伏以上,往往该运放不在线性区工作,或者已经损坏。

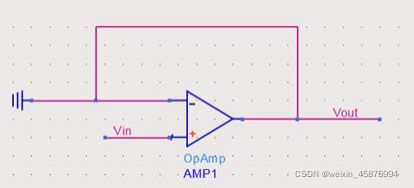

使用运放构成电压跟随器的稳定性问题

出处: 使用运放构成电压跟随器的稳定性问题

| 本文介绍了使用运放构成电压跟随器的稳定性问题及解决方法。 用运放构成电压跟随器的电路,传统教科书仅是简单的把输出和反相输入端连接起来完事儿(如图一),而实际电路要复杂的多,稳定性问题不可忽视!本文是在一家日本IC厂家网站上找到的,希望对实际应用有一点帮助。 (电压跟随器,顾名思义,就是输出电压与输入电压是相同的,就是说,电压跟随器的电压放大倍数恒小于且接近1。) 电压跟随器的显著特点就是,输入阻抗高,而输出阻抗低,一般来说,输入阻抗要达到几兆欧姆是很容易做到的。输出阻抗低,通常可以到几欧姆,甚至更低。 在电路中,电压跟随器一般做缓冲级及隔离级。因为,电压放大器的输出阻抗一般比较高,通常在几千欧到几十千欧,如果后级的输入阻抗比较小,那么信号就会有相当的部分损耗在前级的输出电阻中。在这个时候,就需要电压跟随器来从中进行缓冲。起到承上启下的作用。应用电压跟随器的另外一个好处就是,提高了输入阻抗,这样,输入电容的容量可以大幅度减小,为应用高品质的电容提供了前提保证。电压跟随器的另外一个作用就是隔离,在HI-FI电路中,关于负反馈的争议已经很久了,其实,如果真的没有负反馈的作用,相信绝大多数的放大电路是不能很好的工作的。但是由于引入了大环路负反馈电路,扬声器的反电动势就会通过反馈电路,与输入信号叠加。造成音质模糊,清晰度下降,所以,有一部分功放的末级采用了无大环路负反馈的电路,试图通过断开负反馈回路来消除大环路负反馈的带来的弊端。但是,由于放大器的末级的工作电流变化很大,其失真度很难保证。) Q. 用电压跟随器使运算放大器保持稳定,须注意哪些问题? A:对于采用负反馈的放大电路,如何减少振荡以保持稳定,目前尚无定论。电压跟随器也不例外。 运算放大器理想的运行状态是输出电压和输入电压为同相,即,当负输入端的印加电压引起输出增大时,运算放大器能够相应地使增加的电压降低。不过,运算放大器的输入端和输出端的相位总有差异。当输出和输出之间的相位相差180°时,负输入与正输入正好相同,原本应该减少的输出却得到了增强。(成为正反溃的状态。)如果在特定频段陷入这一状态,并且仍然保持原有振幅,那么该输出频率和振荡状态将一直持续下去。 2. 输入输出端出现相位差的主要原因 其原因大致可分为两种: 1.由于运算放大器固有的特性 2.由于运算放大器以外的反馈环路的特性 2.1. 运算放大器的特性 Fig2a 及Fig2b分别代表性地反映了运算放大器的电压增益—频率特性和相位—频率特性。数据手册中也有这两张曲线图。 如图所示,运算放大器的电压增益和相位随频率变化。运算放大器的增益与反馈后的增益(使用电压跟随器时为0dB)之差,即为反馈环路绕行一周的增益(反馈增益)。如果反馈增益不足1倍(0dB),那么,即使相位变化180o,回到正反馈状态,负增益也将在电路中逐渐衰减,理论上不会引起震荡。 反而言之,当相位变化180o后,如频率对应的环路增益为1倍,则将维持原有振幅;如频率对应的环路增益为大于1倍时,振幅将逐渐发散。在多数情况下,在振幅发散过程中,受最大输出电压等非线性要素的影响,振幅受到限制,将维持震荡状态。 为此,当环路增益为0dB时的频率所对应的相位与180o之间的差是判断负反馈环路稳定性的重要因素,该参数称为相位裕度。 如没有特别说明,单个放大器作为电压跟随器时,要保持足够相位裕度的。 注:数据手册注明「建议使用6dB以上的增益」的放大器,不可用作电压跟随器。 2.2. 运算放大器周边电路对反馈环路的影响 在实际应用中,构成电压跟随器并非象Fig1.那样简单地将输入端和输出端直接连接在一起。至少输出端是与某个负载连接在一起的。因此,必须考虑到该负载对放大器的影响。 例如,如Fig3.所示,输出端和接地之间接电容时,这一容量与运算放大器的输出电阻构成的常数造成相位滞后。 (Fig2b.所示之状态可能变化为Fig2c所示之状态)这时,环路增益在输出电阻和C的作用下降低。同时,相位和增益之间不再有比例关系,相位滞后成为决定性因素,使反馈环路失去稳定,最糟糕时可能导致震荡。单纯地在输出端和接地之间连接电容,构成电压跟随器时,每种运算放大器之间的稳定性存在差异。 Fig4.为输入端需要保护电阻的运算放大器可能发生的问题。 为解决Fig3.出现的问题,可采用Fig5.(a)、(b)所示之方法。(a)图中插入R,消除因CL而产生的反馈环路相位滞后。(在高频区,R作为运算放大器的负荷取代了CL而显现出来。) (b)则用C1来消除CL造成的相位滞后。 为解决Fig4.的问题,则可在输入保护电阻上并联一个尺寸适当的电容。一般被叫做“输入电容取消值”的近似值约为10pF~100pF。 |

FET运放

ADC驱动器手册里截选

微弱信号放大技巧

原文链接:硬件十万个为什么——运放篇(四)微弱信号放大技巧_z00143104的专栏-CSDN博客_微弱信号放大

如何实现微弱信号放大?

传感器+运算放大器+ADC+处理器是运算放大器的典型应用电路,在这种应用中,一个典型的问题是传感器提供的电流非常低,在这种情况下,如何完成信号放大?

大多数检测固定频率信号(调制信号),可以通过信号的相干性进行检测。但是大多数场景传感器的信号是非调制信号,无法通过相干性进行算法检测。

通过电路设计如何提高信号的信噪比

另有工程师朋友建议,在运放、电容、电阻的选择和布板时,要特别注意选择高阻抗、低噪声运算和低噪声电阻。设计注意事项如下:

要点一、防止干扰:

要点二、提高器件本底噪声:

要点三、电路设计:

开环增益 线性

运放跟随驱动问题 - 电路设计论坛 - 电子技术论坛 - 广受欢迎的专业电子论坛!

tlv2211的闭环输出阻抗有点大,开环增益(在负载阻抗为10k的时候)有点小,所以导致这个运放在小负载的时候,不是工作在线性的,你可以理解为开环输出阻抗“分压”。我大致计算了下,是没问题的,你可以根据闭环输出阻抗200 ohm(见datasheet),大致算出运放的开环输出阻抗2.6K,然后根据运放列电流测流向列方程如下:设此时运放正相端电压为U,则(3-U)/Rid+Aou*Ro=U/RL, 把数值代入即可,其中Ro为开环输出阻抗。所以你得增加负载,使得此运放的开环增益变大,此时运放才线性。

尺寸最小的比较器 运放

如何用最小的器件缩小PCB板空间-电子发烧友网

辨别运放和电压比较器

很简单,看看有没有反馈线。

他们用的是一个器件,比如LM393。只是外围电路不同,是电路工作状态不同。

运放工作在深度负反馈状态,从输出会引一根线到输入端。所以有个反馈电阻。

比较器就没有。直接从两个输入端输入信号。

运放闭环开环

运放开环和闭环输出阻抗解析 - 电力电子技术 - 电子技术论坛 - 广受欢迎的专业电子论坛!

两者相同的就是:两者都是放大器的输出电阻。

不同的在于:前者是带有反馈(一般是负反馈)后的输出电阻,后者是没有带反馈的放大器的输出电阻。两者很有可能不一样,比如如果放大器引入了电压负反馈后,闭环输出电阻要小于开环输出电阻,如果是引入了电流负反馈,则相反。

运放输出阻抗

1、当信号送入一个放大器时,就会有一个电压加在输入级上,如果你的输入级阻抗很小则势必会有较大电流通过,而前级电路又提供不了如此大的电流,你说说会出现什么情况呢?输入电压就降低了呀,那么送进放大器的电压就比源电压要小很多了,不能有效放大;

2.当信号从放大器输出的时候,在输出端会有一个负载(广义的啊,别狭义的理解),这时他需要一定的电流提供能力,你的输出阻抗如果高,输出电流流经输出电阻,再经过负载,势必有一部分能量是消耗在了输出电阻上了;

因此,理想状态的电压/电压运算放大器都是:Ri=无穷大、Ro=0、开环增益=无穷大。

那么需要注意的事情:很多传感器是容性的,其信号也是以交流信号为主。那么这些传感器的信号放大,需要正向放大。因为反向放大的输入阻抗无法保证。

传感器的直流阻抗也在M级,那么需要需要运放的输入阻抗在10M级别。

另外需要关注放大电路的容性阻抗。考虑在信号全频段的阻抗分布。

————————————————

原文链接:硬件十万个为什么——运放篇(十)输入阻抗_z00143104的专栏-CSDN博客_运算放大器的输入阻抗

振荡运放

Bruce Trump系列:“驯服”振荡运算放大器

运放自激震荡的大杂烩总结

1.运放振荡两个条件

(1)环路增益大于1(|AF|>1)

(2)反馈前后信号的相位差在360度以上,附加相位180以上(由于负反馈接反向端)。

A(开环增益) = Xo/Xi F(反馈系数)=Xf/Xo

2. 运放震荡判断方法:

常用的是相位裕度,即20lg|AF|=0时,相位偏移是否超过180

什么是穿越频率? fc

G(S)*H(S)对应的增益为1(即幅值不变)的频率即为穿越频率。换算为dB单位:20log1=0dB

3. 消除自激的方法:

由自激震荡条件可知,消除震荡可从两个方面着手:

(一)减少环路增益(但该方法增加了运放增益误差)

对运放来说,就是减少反馈系数F,换句话说,F越大,产生自激震荡的可能性越大。对于电阻反馈网络,F的最大值是1,F=1的典型电路就是电压跟随电路。这就是电压跟随运放易震荡原因(这也是我们常常会看到运放手册标有单位增益稳定说明的原因,但电压跟随的增益误差较小)。

这也是对于电压反馈来说,容性负载驱动能力随闭环增益成比例增加。所以,如果闭环增益为1时,VFA可稳定驱动100pF容性负载,那么闭环增益为10时,便能驱动1000pF容性负载

但由于设计原因,闭环增益的大小通常不是能够随便改变的,故该方法适用性不强。

(二 )增大相位裕度

要求在穿越频率点上,开环传递函数G(S)*H(S)的相移应该与180°保持足够的裕量。这个裕量选取多少比较合适呢?目前在工程应用上通常选取45°,即要求传递函数G(S)*H(S)的相移应该小于135°

相位补偿【滞后/ 超前补偿(环路内/外)】

按补偿原理分滞后补偿、超前补偿及滞后一超前补偿

滞后补偿:凡是使相移滞后的补偿即被称为滞后补偿。滞后补偿使主极点频率降低,即放大器频带变窄。(类似RC低通滤波)

超前补偿:凡是使相移超前的补偿即被称为超前补偿,超前补偿使幅频特性曲线出现零点,即放大器频带变宽 (类似RC高通滤波)

对于负载存在的容性(CL),环路增益在输出电阻和CL的作用下降低。同时,相位和增益之间不再有比例关系,相位滞后成为决定性因素。

1. 环路外补偿--超前补偿(适用小容性负载<1500pf或负载阻抗一定 )

在运放的输出端和负载电容之间串入一个电阻RX,一般而言它的阻值为10-100欧姆。

2. 环路内补偿--超前补偿(适用大容性负载>1500pf或负载阻抗不定 )

Rx在运放反馈环路以内,同时在反馈电阻上并联一个反馈电容(该电容可消除运放输入电容及杂散电容形成极点),一般而言:Rx=50~200Ω,Cf约为3~10pF

。。。。。。。。。。。。。。。。

待:

合集|一文搞定运放放大电路!

简单易懂的告诉你运放跟随的作用,看了这个你在设计电路时就会懂得什么时候用跟随_circuit in my brain的博客-CSDN博客_运放跟随-------------------------