ALtera DE2开发板学习03

在串行通讯时,要求通讯双方都采用一个标准接口,RS232的作用就是使不同的设备可以方便地连接起来进行通讯。

RS-232接口

符合美国电子工业联盟(EIA)制定的串行数据通信的接口标准,原始编号全称是EIA-RS-232(简称232,RS232)。它被广泛用于计算机串行接口外设连接。连接电缆和机械、电气特性、信号功能及传送过程。

特点:

1、接口的信号电平值较高,易损坏接口电路的芯片。RS232接口任何一条信号线的电压均为负逻辑关系。即:逻辑"1"为-3- -15V;逻辑"0":+3- +15V ,噪声容限为2V。即要求接收器能识别高于+3V的信号作为逻辑"0",低于-3V的信号作为逻辑"1",TTL电平为5V为逻辑正,0为逻辑负 。与TTL电平不兼容故需使用电平转换电路方能与TTL电路连接。

2、传输速率较低,在异步传输时,比特率为20Kbps;因此在51CPLD开发板中,综合程序波特率只能采用19200,也是这个原因。

3、接口使用一根信号线和一根信号返回线而构成共地的传输形式,这种共地传输容易产生共模干扰,所以抗噪声干扰性弱。

4、传输距离有限,最大传输距离标准值为50英尺,实际上也只能用在15米左右。

PS2接口的接口特性

物理连接:一般,具有五脚连接器的键盘称之为AT键盘,而具有六脚mini-DIN连接器的键盘则称之为PS/2键盘。其实这两种连接器都只有四个脚有意义。它们分别是Clock(时钟脚)、Data(数据脚)、+5V(电源脚)和Ground(电源地)。在PS/2键盘与PC机的物理连接上只要保证这四根线一一对应就可以了。PS/2键盘靠PC的PS/2端口提供+5V电源,另外两个脚Clock(时钟脚)和Data(数据脚)都是集电极开路的,所以必须接大阻值的上拉 电阻 。它们平时保持高电平,有输出时才被拉到低电平,之后自动上浮到高电平。

电气特性:PS/2通讯协议是一种双向同步串行通讯协议。通讯的两端通过Clock(时钟脚)同步,并通过Data(数据脚)交换数据。任何一方如果想抑制另外一方通讯时,只需要把Clock(时钟脚)拉到低电平。如果是PC机和PS/2键盘间的通讯,则PC机必须做主机,也就是说,PC机可以抑制PS/2键盘发送数据,而PS/2键盘则不会抑制PC机发送数据。一般两设备间传输数据的最大时钟频率是33kHz,大多数PS/2设备工作在10~20kHz。推荐值在15kHz左右,也就是说,Clock(时钟脚)高、低电平的持续时间都为40μs。

USB接口的优势

1.可以 热插拔 。就是用户在使用外接设备时,不需要关机再开机等动作,而是在电脑工作时,直接将USB插上使用。

2.携带方便。USB设备大多以“小、轻、薄”见长,对用户来说,随身携带大量数据时,很方便。当然USB硬盘是首要之选了。

3.标准统一。大家常见的是IDE接口的硬盘,串口的鼠标键盘,并口的打印机扫描仪,可是有了USB之后,这些应用外设统统可以用同样的标准与个人电脑连接,这时就有了USB硬盘、USB鼠标、USB打印机等等。

4.可以连接多个设备。USB在个人电脑上往往具有多个接口,可以同时连接几个设备,如果接上一个有四个端口的USB HUB时,就可以再连上;四个USB设备,以此类推,尽可以连下去,将你家的设备都同时连在一台个人电脑上而不会有任何问题。

振荡器(oscillator)是一种能量转换装置——将直流电能转换为具有一定频率的交流电能,其构成的电路叫振荡电路。振荡器主要可以分成两种:谐波振荡器(harmonic oscillator)与弛张振荡器(relaxation oscillator)。

石英是一种物理性质和化学性质均十分稳定的矿产资源,晶体属三方晶系的氧化物矿物。石英块又名硅石, 主要是生产石英砂 (又称硅砂)的原料, 也是石英耐火材料和烧制硅铁的原料。

石英是由二氧化硅组成的矿物,化学式SiO2。

有一些电子设备需要频率高度稳定的交流信号,而LC振荡器稳定性较差,频率容易漂移(即产生的交流信号频率容易变化)。在振荡器中采用一个特殊的元件——石英晶体,可以产生高度稳定的信号,这种采用石英晶体的振荡器称为晶体振荡器。

晶振是电子电路中最常用的电子元件之一,一般用字母“X”、“G”或“Z”表示,单位为Hz。晶振是电子电路中最常用的电子元件之一,一般用字母“X”、“G”或“Z”表示,单位为Hz。

石英晶体有两个谐振频率,即fs和fp,fp略大于fs。当加到石英晶体两端信号的频率不同时,它会呈现出不同的特性,,具体说明如下。

①当f=fs时,石英晶体呈阻性,相当于阻值小的电阻。

②当fs

晶振用一种能把电能和机械能相互转化的晶体在共振的状态下工作,以提供稳定,精确的单频振荡。在通常工作条件下,普通的晶振频率绝对精度可达百万分之五十。高级的精度更高。有些晶振还可以由外加电压在一定范围内调整频率,称为压控振荡器(VCO)。

晶振的作用是为系统提供基本的时钟信号。通常一个系统共用一个晶振,便于各部分保持同步。有些通讯系统的基频和射频使用不同的晶振,而通过电子调整频率的方法保持同步。

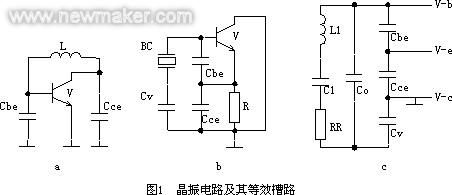

晶振一般采用如图1a的电容三端式(考毕兹) 交流等效振荡电路;实际的晶振交流等效电路如图1b,其中Cv是用来调节振荡频率,一般用变容二极管加上不同的反偏电压来实现,这也是压控作用的机理;把晶体的等效电路代替晶体后如图1c。其中Co,C1,L1,RR是晶体的等效电路。

分析整个振荡槽路可知,利用Cv来改变频率是有限的:决定振荡频率的整个槽路电容C=Cbe,Cce,Cv三个电容串联后和Co并联再和C1串联。可以看出:C1越小,Co越大,Cv变化时对整个槽路电容的作用就越小。因而能“压控”的频率范围也越小。实际上,由于C1很小(1E-15量级),Co不能忽略(1E-12量级,几PF)。所以,Cv变大时,降低槽路频率的作用越来越小,Cv变小时,升高槽路频率的作用却越来越大。这一方面引起压控特性的非线性,压控范围越大,非线性就越厉害;另一方面,分给振荡的反馈电压(Cbe上的电压)却越来越小,最后导致停振。采用泛音次数越高的晶振,其等效电容C1就越小;因此频率的变化范围也就越小。

微控制器的时钟源可以分为两类:基于机械谐振器件的时钟源,如晶振、陶瓷谐振槽路;RC(电阻、电容)振荡器。一种是皮尔斯振荡器配置,适用于晶振和陶瓷谐振槽路。另一种为简单的分立RC振荡器。

用万用表测量晶体振荡器是否工作的方法:测量两个引脚电压是否是芯片工作电压的一半,比如工作电压是51单片机的+5V则是否是2.5V左右。另外如果用镊子碰晶体另外一个脚,这个电压有明显变化,证明是起振了的。

晶振的类型有SMD和DIP型,即贴片和插脚型 。

先说DIP:常用尺寸有HC-49U/T,HC-49S,UM-1,UM-5,这些都是MHZ单位的。

再说SMD:有0705,0603,0503,0302,这里面又分四个焊点和二个焊点的,对我们公司来说默认的是四个焊点的,两个焊点的材料要求进口,周期长,一般说两个焊点的做不了。

Cyclone(飓风),Altera中等规模FPGA,2003年推出,0.13um工艺,1.5v内核供电,与Stratix结构类似,是一种低成本FPGA系列 ,是当前主流产品,其配置芯片也改用全新的产品。

CycloneII:Cyclone的下一代产品,2005年开始推出,90nm工艺,1.2v内核供电,属于低成本FPGA,性能和Cyclone相当,提供了硬件乘法器单元。

CycloneIII FPGA系列2007年推出,采用台积电(TSMC)65nm低功耗(LP)工艺技术制造,以相当于ASIC的价格实现了低功耗。

Cyclone IV FPGA系列2009年推出,60nm工艺,面向对成本敏感的大批量应用,帮助您满足越来越大的带宽需求,同时降低了成本。

CycloneV FPGA系列2011年推出,28nm工艺,实现了业界最低的系统成本和功耗,其性能水平使得该器件系列成为突出您大批量应用优势的理想选择。与前几代产品相比,它具有高效的逻辑集成功能,提供集成收发器型号,总功耗降低了40%,静态功耗降低了30%。

IrDA红外数据通讯简介

红外线是波长在750nm至1mm之间的电磁波,它的频率高于微波而低于可见光,是一种人的眼睛看不到的光线。

红外通讯一般采用红外波段内的近红外线,波长在0.75um至25um之间。红外数据协会(IRDA)成立后,为了保证不同厂商的红外产品能够获得最佳的通讯效果,红外通讯协议将红外数据通讯所用的光波波长的范围限定在850nm至900nm之内。

无线电波和微波已被广泛地应用在长距离的无线通讯之中,但由于红外线的波长较长,对障碍物的衍射能力差,所以更适合应用在需要短距离无线通讯的场合,进行点对点的直线数据传输。

红外通讯有着成本低廉、连接方便、简单易用和结构紧凑的特点,因此在小型的移动设备中获得了广泛的应用。这些设备包括笔记本电脑、掌上电脑、机顶盒、游戏机、移动电话、计算器、寻呼机、仪器仪表、MP3播放机、数码相机以及打印机之类的计算机外围设备等等。试想一下,如果没有红外通讯,连接这其中的两个设备就必须要有一条特制的连线,如果要使它们能够任意地两两互联传输数据,该需要多少种连线呢?而有了红外口,这些问题就都迎刃而解了。

要使各种设备能够通过红外口随意连接,一个统一的软硬件规范是必不可少的。但在红外通讯发展早期,恰恰就存在着这样的规范不统一问题:许多公司都有着自己的一套红外通讯标准,同一个公司生产的设备自然可以彼此进行红外通讯,但却不能与其它公司有红外功能的设备进行红外通讯。当时比较流行的红外通讯系统有惠普的HPSIR,夏普的ASKIR和General Magic的MagicBeam等,虽然它们的通讯原理比较相似,但却不能互相感知。混乱的标准给用户带来了很大的不便,并给人们造成了一种红外通讯不太实用的错觉。

为了建立一个统一的红外数据通讯的标准,1993年,由HP、COMPAQ、INTEL等二十多家公司发起成立了红外数据协会(Infrared Data Association,简称IRDA),1993年6月28日,来自50多家企业的120多位代表出席了红外数据协会的首次会议,并就建立统一的红外通讯标准问题达成了一致。一年以后,第一个IRDA的红外数据通讯标准发布,即IRDA1.0。

IRDA1.0简称为SIR(Serial InfraRed),它是基于HP-SIR开发出来的一种异步的、半双工的红外通讯方式。SIR以系统的异步通讯收发器(UART)为依托,通过对串行数据脉冲的波形压缩和对所接收的光信号电脉冲的波形扩展这一编码解码过程(3/16 EnDec)实现红外数据传输。由于受到UART通讯速率的限制,SIR的最高通讯速率只有115.2Kbps,也就是大家熟知的电脑串行端口的最高速率。

1996年,IRDA发布了IRDA1.1标准,即Fast InfraRed,简称为FIR。与SIR相比,由于FIR不再依托UART,其最高通讯速率有了质的飞跃,可达到4Mbps的水平。FIR采用了全新的4PPM调制解调(PulsePosition Modulation),即通过分析脉冲的相位来辨别所传输的数据信息,其通讯原理与SIR是截然不同的,但由于FIR在115.2Kbps以下的速率依旧采用SIR的那种编码解码过程,所以它仍可以与支持SIR的低速设备进行通讯,只有在通讯对方也支持FIR时,才将通讯速率提升到更高水平。

就象USB和IEEE 1394技术一样,红外数据通讯的速率也在不断地攀升之中。继FIR之后,IRDA又发布了通讯速率高达16Mbps的VFIR技术(Very Fast InfraRed),并将它作为补充纳入IRDA1.1标准之中。更高的通讯速率使红外通讯在那些需要进行大数据量传输的设备上也可以占有一席之地,而不再仅仅是连接线的替代。

IRDA标准包括三个基本的规范和协议:物理层规范(Physical Layer Link Specification),连接建立协议(Link Access Protocol:IRLAP) 和连接管理协议(Link Management Protocol:IrLMP)。物理层规范制定了红外通讯硬件设计上的目标和要求,IrLAP和IrLMP为两个软件层,负责对连接进行设置、管理和维护。在IrLAP和IrLMP基础上,针对一些特定的红外通讯应用领域,IRDA还陆续发布了一些更高级别的红外协议,如TinyTP、IrOBEX、IRCOMM、IrLAN、IrTran-P等等,在此不再赘述了。

SMA系列连接器是一种应用广泛的小型螺纹连接的同轴连接器,寿命长,性能优越、可靠性高,广泛用于微波设备和数字通信设备的射频回路射频同轴电缆或微带。

在无线设备上常用于单板上的GPS时钟接口及基站射频模块的测试口。现阶段手持对讲机*常见的接口,已经很普遍。

LCD ( Liquid Crystal Display 的简称)液晶显示器。LCD 的构造是在两片平行的玻璃基板当中放置液晶盒,下基板玻璃上设置TFT(薄膜晶体管),上基板玻璃上设置彩色滤光片,通过TFT上的信号与电压改变来控制液晶分子的转动方向,从而达到控制每个像素点偏振光出射与否而达到显示目的。

上位机是指可以直接发出操控命令的计算机,一般是PC/host computer/master computer/upper computer,屏幕上显示各种信号变化(液压,水位,温度等)。下位机是直接控制设备获取设备状况的计算机,一般是PLC/单片机single chip microcomputer/slave computer/lower computer之类的。上位机发出的命令首先给下位机,下位机再根据此命令解释成相应时序信号直接控制相应设备。下位机不时读取设备状态数据(一般为模拟量),转换成数字信号反馈给上位机。简言之如此,实际情况千差万别,但万变不离其宗:上下位机都需要编程,都有专门的开发系统。

在概念上,控制者和提供服务者是上位机,被控制者和被服务者是下位机,也可以理解为主机和从机的关系,但上位机和下位机是可以转换的。

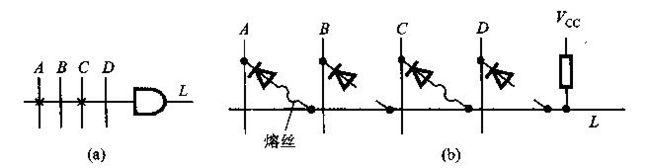

这是可编程逻辑电路PLD,熔丝在电压作用下熔断,编程的时候就通比它工作电压高很多的电压,然后熔丝就断了。

刻录也叫烧录,就是把想要的数据通过刻录机、刻录软件等工具刻制到光盘、烧录卡(GBA)等介质中。刻录也叫烧录,就是把想要的数据通过刻录机、刻录软件等工具刻制到光盘、烧录卡(GBA)等介质中。

这个词最早是用在一次性可编程只读存储器上。不同于更早的集成电路,这样的存储器出厂时是一枚空白的芯片,可以通过特殊设备写入内容。怎么写?高电压。比方说芯片正常的读取电压是3.3V,那么写入就需要16V的电压,这会永久性地改变写入位置的物理组成。写入之后再对特定针脚施加16V,烧断高压电路,这样这枚OTPNVM就无法再次写入了。

写入可写光盘原理也根本就是用大功率(远高于普通读取)的激光使可写光盘表面的特定位置的染料变性,使反光度发生变化,于是信息就记录上去了。

它的原理是在圆筒上的铁线上记录磁信号。

这时录制和消磁并不能在同一台设备上完成。直到磁记录设备家用化之前,消磁也必须在另外的设备上完成。这个消磁的过程看起来就像是把磁介质走过一个黑盒子里,这个盒子洗掉了磁信号。

因为刻录的物理过程就是激光头用激光打在光盘的涂层上,烧出一个一个小坑,来完成0和1的记录,所以也叫烧盘.

1.FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。

AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持 Cyclone系列。使用Altera串行配置器件来完成。Cyclone期间处于主动地位,配置期间处于从属地位。配置数据通过DATA0引脚送入 FPGA。配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。(见附图)

PS则由外部计算机或控制器控制配置过程。通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,在PS配置期间,配置数据从外部储存部件,通过DATA0引脚送入FPGA。配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。(见附图)

JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 1149.1联合边界扫描接口引脚,支持JAM STAPL标准,可以使用Altera下载电缆或主控器来完成。

FPGA在正常工作时,它的配置数据存储在SRAM中,加电时须重新下载。在实验系统中,通常用计算机或控制器进行调试,因此可以使用PS。在实用系统中,多数情况下必须由FPGA主动引导配置操作过程,这时FPGA将主动从外围专用存储芯片中获得配置数据,而此芯片中fpga配置信息是用普通编程器将设计所得的pof格式的文件烧录进去。

专用配置器件:epc型号的存储器

常用配置器件:epc2,epc1,epc4,epc8,epc1441(现在好象已经被逐步淘汰了)等

对于cyclone cycloneII系列器件,ALTERA还提供了针对AS方式的配置器件,EPCS系列.如EPCS1,EPCS4配置器件也是串行配置的.注意,他们只适用于cyclone系列.

除了AS和PS等单BIT配置外,现在的一些器件已经支持PPS,FPS等一些并行配置方式,提升配置了配置速度。当然所外挂的电路也和PS有一些区别。还有处理器配置比如JRUNNER 等等,如果需要再baidu吧,至少不下十种。比如Altera公司的配置方式主要有Passive Serial(PS),Active Serial(AS),Fast Passive Parallel(FPP),Passive Parallel Synchronous(PPS),Passive Parallel Asynchronous(PPA),Passive Serial Asynchronous(PSA),JTAG等七种配置方式,其中Cyclone支持的配置方式有PS,AS,JTAG三种.

2 对FPGA芯片的配置中,可以采用AS模式的方法,如果采用EPCS的芯片,通过一条下载线进行烧写的话,那么开始的"nCONFIG,nSTATUS"应该上拉,要是考虑多种配置模式,可以采用跳线设计。让配置方式在跳线中切换,上拉电阻的阻值可以采用10K

3,在PS模式下tip:如果你用电缆线配置板上的FPGA芯片,而这个FPGA芯片已经有配置芯片在板上,那你就必须隔离缆线与配置芯片的信号.(祥见下图).一般平时调试时不会把配置芯片焊上的,这时候用缆线下载程序.只有在调试完成以后,才把程序烧在配置芯片中, 然后将芯片焊上.或者配置芯片就是可以方便取下焊上的那种.这样出了问题还可以方便地调试.

&<60; 在AS模式下tip: 用过一块板子用的AS下载,配置芯片一直是焊在板子上的,原来AS方式在用线缆对配置芯片进行下载的时候,会自动禁止对FPGA的配置,而PS方式需要电路上隔离。

4,一般是用jtag配置epc2和flex10k,然后 epc2用ps方式配置flex10k.这样用比较好.(这是我在网上看到的,可以这样用吗?怀疑中)望达人告知.

5,下载电缆,Altera下的下载电缆分为byteblaster和byteblasterMV,以及ByteBlaster II,现在还推出了基于USB-blaster.由于BB基本已经很少有人使用,而USB-Blaster现在又过于昂贵,这里就说一下BBII和 BBMV的区别.

BBII支持多电压供电5.5v,3.3v,2.5v,1.8v;

BBII支持三种下载模式:AS,可对Altera的As串行配置芯片(EPCS系列)进行编程

&<60; &<60; &<60; &<60; &<60; &<60; &<60; &<60; &<60; &<60; PS,可对FPGA进行配置

&<60; &<60; &<60; &<60; &<60; &<60; &<60; &<60; &<60; JTAG,可对FPGA,CPLD,即Altera配置芯片(EPC系列)编程

&<60; &<60; 而BBMV只支持PS和JTAG

6,一般在做FPGA实验板,(如cyclone系列)的时候,用AS+JTAG方式,这样可以用JTAG方式调试,而最后程序已经调试无误了后,再用 AS模式把程序烧到配置芯片里去,而且这样有一个明显的优点,就是在AS模式不能下载的时候,可以利用Quartus自带的工具生成JTAG模式下可以利用的jic文件来验证配置芯片是否已经损坏,方法祥见附件(这是骏龙的人写的,摘自咱们的坛子,如有版权问题,包涵包涵).

7.Altera的FPGA可以通过单片机,CPLD等加以配置,主要原理是满足datasheet中的时序即可,这里我就不多说了,有兴趣的朋友可以看看下面几篇文章,应该就能够明白是怎么回事了.

8.配置时,quartus软件操作部分:

(1).assignment-->device-->device&pin options-->选择configuration scheme,configuaration mode,configuration device,注

意在不支持远程和本地更新的机器中configuration mode不可选择,而configuration device中会根据不同的配置芯片产生pof文件,

如果选择自动,会选择最小密度的器件和适合设计

(2).可以定义双口引脚在配置完毕后的作用,在刚才的device&pin option-->dual-purpose pins-->,可以在配置完毕后继续当I/O口

使用

(3).在general菜单下也有很多可钩选项,默认情况下一般不做改动,具体用法参见altera configuration

handbook,volume2,sectionII.

(4)关于不同后缀名的文件的适用范围:

sof(SRAM Object File)当直接用PS模式下将配置数据下到FPGA里用到,USB BLASTER,MASTERBLASER,BBII,BBMV适用,quartusII会自

动生成,所有其他的配置文件都是由sof生成的.

pof(Programmer Object File)也是由quartusII自动生成的,BBII适用,AS模式下将配置数据下到配置芯片中

rbf(Raw Binary File)用于微处理器的二进制文件.在PS,FPP,PPS,PPA配置下有用处

rpd(Raw Programing Data File)包含bitstream的二进制文件,可用AS模式配置,只能由pof文件生成

hex(hexadecimal file)这个就不多说了,单片机里很多

ttf(Tabular Text File)适用于FPP,PPS,PPA,和bit-wide PS配置方式

sbf(Serial Bitstream File)用PS模式配置Flex 10k和Flex6000的

jam(Jam File)专门用于program,verigy,blank-check

AS模式,上位机通过JTAG口向FPGA烧写flash loader可执行代码到RAM,编程代码也下载到RAM,上位机发送命令给flash loader再将编程代码挪到flash中。掉电还在flash中保存。

JTAG模式,上位机直接将代码下到FPGA里的SRAM.掉电易失。

AS模式(active serial configuration mode):FPGA器件每次上电时,作为控制器从配置器件EPCS主动发出读取数据信号,从而把EPCS的数据读入FPGA中,实现对FPGA的编程。

PS模式(passive serial configutation mode):EPCS作为控制器件,把FPGA当做存储器,把数据写人到FPGA中,实现对FPGA的编程。该模式可以实现对FPGA在线可编程。

在下载配置的时候对于cycloneII的器件,如ep2c8,在JTAG下载方式对应.sof,AS下载方式对应 .pof.

JTAG是直接烧到FPGA里面的 由于是SRAM 断电后要重烧,AS是烧到FPGA的配置芯片里保存的 每次上电就写到FPGA里

关于JTAG的原理,大家可以参考OPEN-JTAG 开发小组写的《ARM JTAG 调试原理》。JTAG、BDM 都比较类似,实际上是将仿真功能嵌入到芯片内部,接上比较简单的调试工具就可以进行开发了,省掉了高价的仿真器。

JTAG 调试用到了 TCK、TMS、TDI、TDO 和 TRST这几个脚。其中 TRST 是用来对 TAP controller进行复位的,它不是必须的。通过在 TMS脚也可以使 TAP controller复位。

Test Clock Input (TCK)

TCK为 TAP的操作提供了一个独立的、基本的时钟信号,TAP 的所有操作都是通过这个时钟信号来驱动的。TCK在 IEEE 1149.1 标准里是强制要求的。

Test Mode Selection Input (TMS)

TMS信号用来控制 TAP状态机的转换。通过 TMS信号,可以控制 TAP在不同的状态间相互转换。TMS信号在 TCK的上升沿有效。TMS在 IEEE 1149.1 标准里是强制要求的。

Test Data Input (TDI)

TDI 是数据输入的接口。所有要输入到特定寄存器的数据都是通过 TDI 接口一位一位串行输入的(由 TCK驱动)。TDI在 IEEE 1149.1 标准里是强制要求的。

Test Data Output (TDO)

TDO 是数据输出的接口。所有要从特定的寄存器中输出的数据都是通过 TDO 接口一位一位串行输出的(由 TCK驱动)。TDO在 IEEE 1149.1 标准里是强制要求的。

Test Reset Input (TRST)

TRST 可以用来对 TAP Controller 进行复位(初始化)。不过这个信号接口在 IEEE 1149.1标准里是可选的,并不是强制要求的。因为通过 TMS也可以对 TAP Controller进行复位(初始化)。

FPGA是现场可编程门阵列,是可编程逻辑器件(PLD)的一种。

NIOS II是一种知识产权核(IP Core),是嵌在FPGA内部的处理器软核,相当于在FPGA内部设计了一个微处理器。

NIOS2这种软核cpu思路很新颖 废物利用网表中闲置的逻辑门 就可以让FPGA平白无故就多了一块强大的控制器 而不用外接一个mcu。

但FPGA功耗/个头较大 更适合一些设计原型的开发中 或是对尺寸成本能耗不敏感的领域。

NIOS2是专为altera公司altera公司开发的系列FPGA的软核处理器(也就是我们说的MCU,但它是一个软核,也就是说,没有时间去里面添加NIOS2软核的FPGA并没有一个处理器,如果你添加,它会合成NIOS2 FPGA的处理器内部),用于NIOS2软件开发是基于C,C + +或汇编语言,软件开发环境和Qartus2支持NIOS2 IDE。

NIOS2的第一步是构建SOPC系统的开发,这一步是Qartus2 SOPC的建设者内进行,之后确定,NIOS2将形成的等待所谓的框图,外围数字电路的其余部分可以按照传统的FPGA开发完成。

FPGA开发完成后,单片机的硬件生产相当于完成后,接下来就需要进行编程NIOS2处理器调试,这一步是在NIOS2 IDE中进行。

EPCS(Erasable programmable configurable serial)是串行存储器,NiosII 不能直接从EPCS中执行程序,它实际上是执行EPCS控制器的片内ROM中的代码(即Bootloader),把EPCS中的程序搬到RAM中执行。

FPGA配置数据和NiosII程序都存放在EPCS器件中。FPGA配置数据放在最前面,程序放在后面,程序可能有多个段,每个段前面都插有一个“程序记录”。一个“程序记录”由2个32位的数据构成,一个是32位的整数,另一个是32位的地址,分别用于表示程序段本身的长度和程序段的运行时地址。这个“程序记录”用于帮助Bootloader把各个程序段搬到程序执行时真正的位置。