ZYNQ小实验:1.利用AXI DMA loop 环路测试

前言:

一个基本的 DMA 环路搭建,通过 PS 端控制 DMA 对 DDR 数据的读写和校验,完成环路测试

基本流程:

PS 端 ARM 将数据发送给 DDR。

PS 控制 DMA,使 DMA 通过数据通道读取 DDR 中的数据;DMA 将读取到的数据传给 FIFO。

FIFO 将数据传输给 DMA;PS 控制 DMA,使 DMA 通过数据通道将数据写入 DDR 中。

传输校验,对比接收数据与发送数据是否一致。

原理介绍:

AXI:AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首地址,同时分离的读写数据通道、并支持Outstanding传输访问和乱序访问,并更加容易进行时序收敛。AXI 是AMBA 中一个新的高性能协议。AXI 技术丰富了现有的AMBA 标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。

详见https://blog.csdn.net/mao0514/article/details/50569076

DMA:

DMA 传输将数据从一个地址空间复制到另外一个地址空间。当CPU 初始化这个传输动作,传输动作本身是由 DMA 控制器来实行和完成。典型的例子就是移动一个外部内存的区块到芯片内部更快的内存区。像是这样的操作并没有让处理器工作拖延,反而可以被重新排程去处理其他的工作。DMA 传输对于高效能 嵌入式系统算法和网络是很重要的。

在实现DMA传输时,是由DMA控制器直接掌管总线,因此,存在着一个总线控制权转移问题。即DMA传输前,CPU要把总线控制权交给DMA控制器,而在结束DMA传输后,DMA控制器应立即把总线控制权再交回给CPU。一个完整的DMA传输过程必须经过DMA请求、DMA响应、DMA传输、DMA结束4个步骤。

关于AXI和DMA的关系详见https://www.cnblogs.com/batianhu/p/zynq_axidma_xiangjie1.html

实验流程:

- FPGA BD 工程搭建

新建一个工程。创建一个 BD 文件,并命名为 system,添加并且配置好 ZYNQ IP。

根据自己的硬件类型配置好输入时钟频率、内存型号、串口,连接时钟等

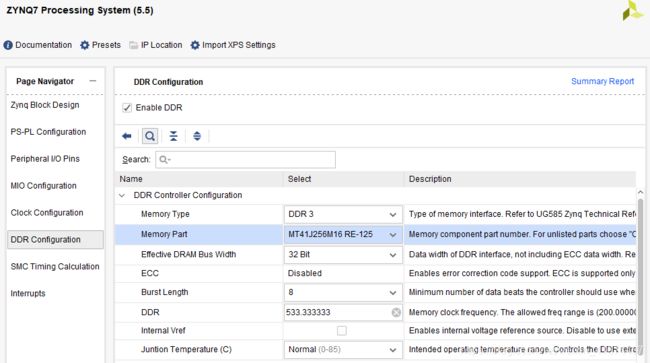

MZ7XA-7020、MZ7XB-7020、MZ702N、MZ702P、MZ7015、MZ7035、MZ7100 的内存型号为 1024GB,选取内存型号(兼容型号):MT41K256M16RE-125

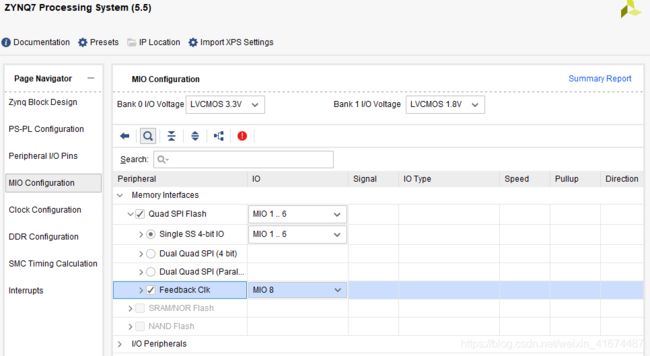

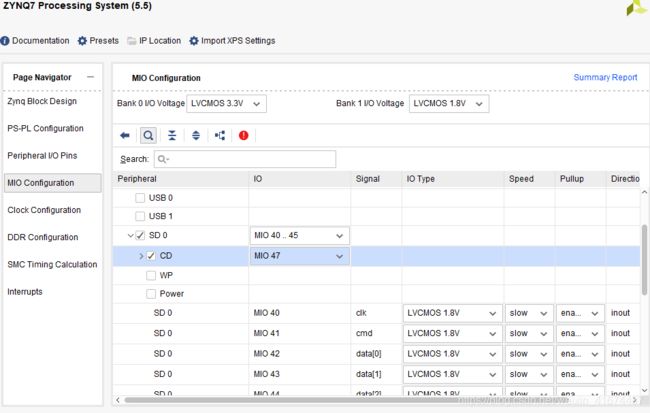

Bank0 IO Voltage为LVCMOS3.3V

Bank1 IO Voltage为LVCMOS1.8V

QSPI FLASH配置:

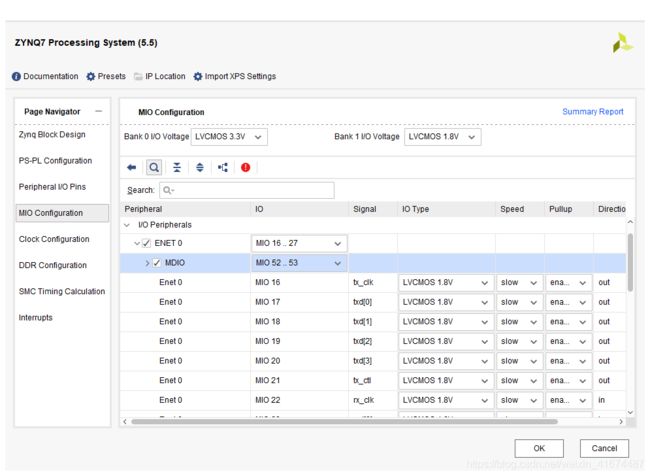

以太网配置:

SD(TF)卡配置:

串口配置:

配

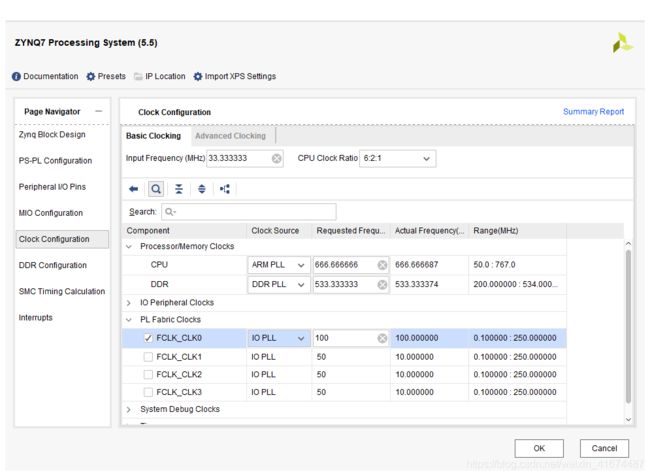

PL Fabric Clock:勾选 FCLK_CLK0,设置为 100,即 PS 的 PLL 提供本系统的时钟 100MHZ。

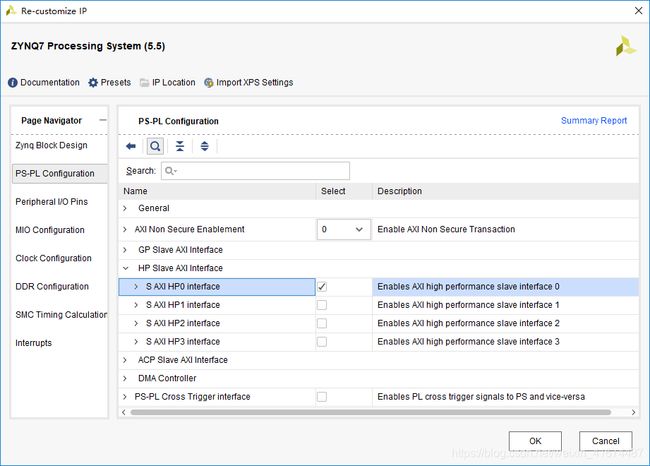

启动 1 路 HP 接口,HP 接口是 ZYNQ 个的高速数据接口。

PS-PL ConfigurationHP Slave AXI Interface勾选 S AXI HP0 interface。

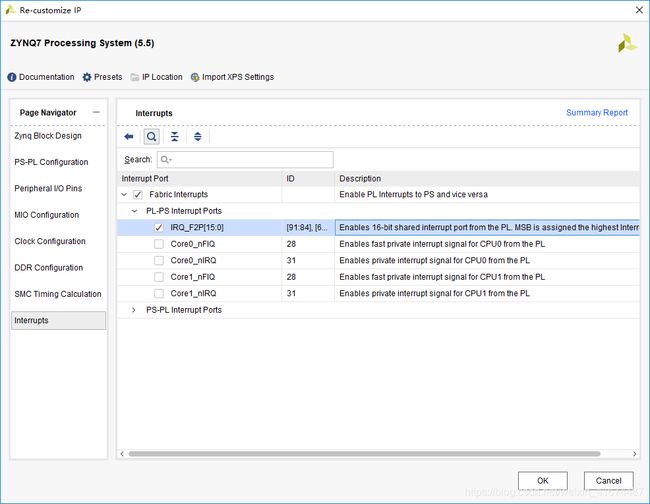

启动 PL 到 PS 的中断资源。Interurpts勾选 Fabric Interrupt,勾选 IRQ_F2P[15:0]

配置完成后单击OK

单击添加IP按钮“+”,输入如下模块IP名字的关键词,并双击添加

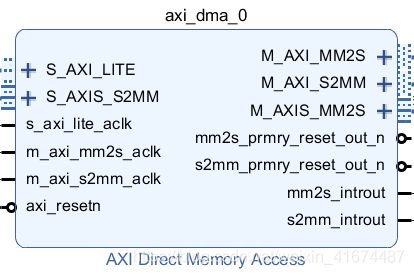

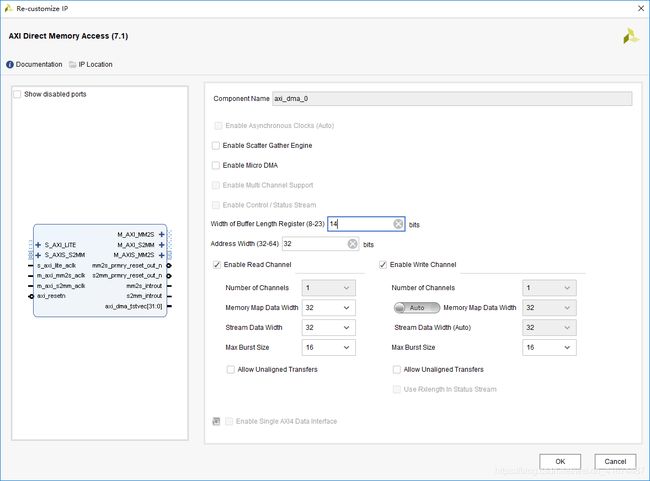

勾选读通道;勾选写通道;

设置 Wideh of buffer length register :14。(寄存器设置最大为 23,即 2 的 23 次方 8,388,607bytes,8M 大小,这里设置 14bit 就够用了,长度越大,需要的资源也就越多)

设置 TDATA Width 为 4。

Concate IP 实现了单个分散的信号,整合成总线信号。这里,将 2 个独立的中断信号,合并在一起连接到 ZYNQ IP

的中断信号接口上。

设置:Number of Ports:2

In0 Width :1

In1 Width :1

Dout Width:2

点击 Run Block Automation ,自动配置 ZYNQ IP

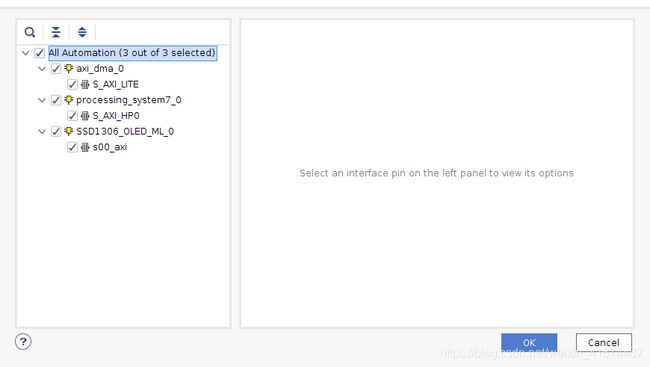

点击 Run Connection Automation 自动连线。只要软件提示你需要自动连线,一般都需要进行自动连线,除非自己知道如何连线,有特殊需求。

如果还有提示需要自动连线的继续让软件自动连线,直到出下如下。可以看到,还有未连线的模块。

把 DMA 收发中断信号,通过 contact IP 连接到 ZYNQ。连接如下:

mm2s_introut 连接到 In0;

s2mm_introut 连接到 In1;

dout 连接到 IRQ_F2P。

连接 FIFO 与 DMA。连接如下:

S_AXIS(FIFO 写端口) 连接到 M_AXIS_MM2S(DMA 读端口);

M_AXIS(FIFO 读端口) 连接到 S_AXIS_S2MM(DMA 写端口);

s_axis_aresetn(FIFO) 连接到 peripheral aresetn(Processor System Reset) ;

s_axis_ack(FIFO) 连接到 FCLK0(ZYNQ IP);

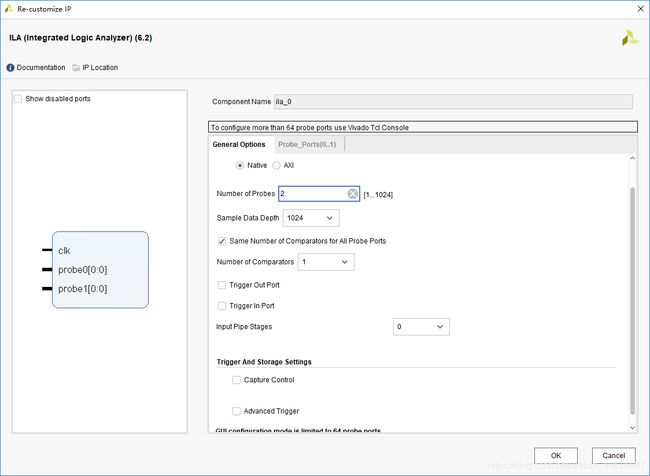

在后面调试中,可以添加 ila 核,观察到中断信号。添加 ila IP, 双击打开 ILA CORE ,进行如下配置,

设置结束点击 OK。

General Options 设置:

选择 Native;

Number of Probes:2

Sample Data Depth:1024

Number of Comparators:1

Probe_Ports 设置:

PROBE0:Probe Width1

PROBE1:Probe Width1

把 ila IP 的时钟与 FCLK_CLK0 连接,探针分别与 DMA 的中断信号连接。

Clk(ila) 连接到 FCLK_CLK0(ZYNQ)

Probe0 连接到 mm2s_introut(DMA)

Probe1 连接到 s2mm_introut(DMA)

置完成后单击OK

后面的操作过程是 Validate Design->Gerate Out products->Create wrappers->Generate Bitstream ,产生完成后导出硬件,加载 SDK。

新建一个名为 AXI_DMA_Test 的空的软件工程

将提供例程中 SDK 工程的源文件复制,并粘贴到新建 SDK 工程,软件会自动编译