自定义AXI IP核实验——FPGA Vitis篇

文章目录

- 1. 前言

- 2. Vivado工程的编写

-

- 2.1 创建自定义IP

- 2.2 添加自定义IP到工程

- 3. Vitis工程的编写

- A. 工程源码下载

1. 前言

Xilinx官方为大家提供了很多IP核,在Vivado的IP Catalog中可以查看这些IP核,用户在构建自己的系统中,不可能只使用Xilinx官方的免费IP核,很多时候需要创建属于自己的用户IP核,创建自己的IP核有很多好处,例如系统设计定制化;设计复用,可以在IP核中加入license,有偿提供给别人使用;简化系统设计和缩短设计时间。用ZYNQ系统设计IP核,最常用的就是使用AXI总线将PS同PL部分的IP核连接起来。本实验将为大家介绍如何在Vivado中构建 AXI总线类型的IP核,此IP核用来产生一个PWM,用这个控制开发板上的LED,做一个呼吸灯的效果。

2. Vivado工程的编写

2.1 创建自定义IP

(1)本实验使用的Vivado工程延用《ZYNQ 串口打印输出——FPGA Vitis篇》中使用的Vivado工程,大家可以查看该文章来了解Vivado工程的建立。

(2)修改Vivado工程,创建自定义IP。点击菜单“Tools->Create and Package IP…”,并点击“Next”。

(4)名称填写AXI_pwm,描述随便填写,然后选择一个合适的位置存放IP。

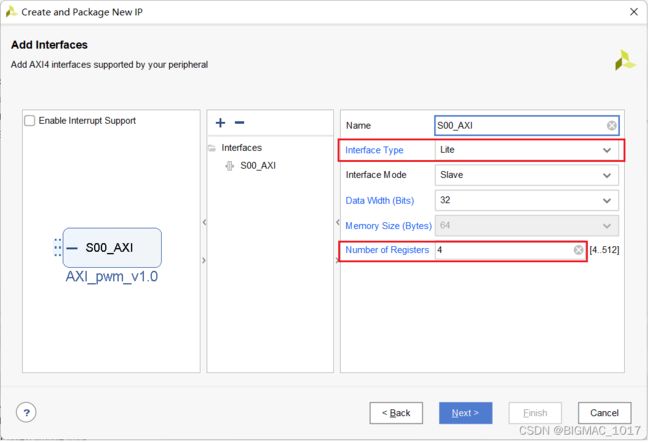

(5)下面参数可以指定接口类型、寄存器数量等,这里不需要修改,使用AXI Lite Slave接口,4个寄存器。点击“Next”-> “Finish”,完成IP的创建。

(6)重新打开“IP Catalog”,可以看到刚才我们创建的IP。

(7)但这时候的IP并没有PWM功能,只有简单的AXI总线读写寄存器功能。我们需要修改 IP,选择IP,右键“Edit in IP Packager”。在弹出的对话框中,不修改默认信息,点击“OK”。

(9)在Vivado “Flow Navigator”中点击“Add Source”,添加PWM功能代码。这里的PWM功能代码借用的是Alinx公司开发板提供的模块代码,用户也可以根据自己需要更改其它代码。

(10)在Vivado中,修改“AXI_pwm_v1_0.v”文件,增加“pwm”输出端口。

(11)修改“AXI_pwm_v1_0.v”,在例化“AXI_pwm_v1_0_S00_AXI”中添加pwm 端口的例化。

(12)修改“AXI_pwm_v1_0_S00_AXI.v”,添加pwm端口,这个文件是实现AXI4 Lite Slave的核心代码。

(13)修改“AXI_pwm_v1_0_S00_AXI.v”文件,例化我们刚添加的axi_pwm.v文件,并将寄存器slv_reg0和slv_reg1用于pwm模块的参数控制。

(14)在工程源文件“Sources”一栏中双击“component.xml”文件。在“File Groups”选项中点击,“Merge changes from File Groups Wizard”。

(15)同样在“Customization Parameters”选项中点击,“Merge changes from Customization Parameters Wizard”。

2.2 添加自定义IP到工程

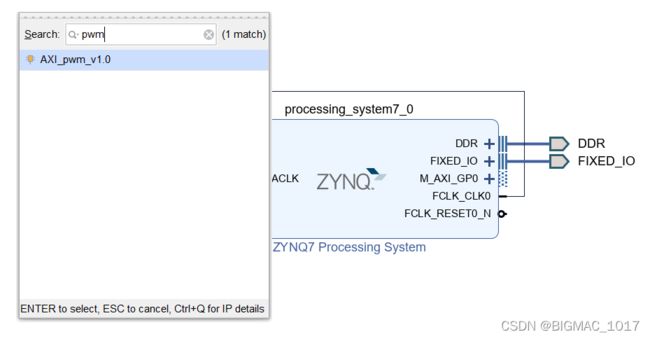

(1)在Block Design中,点击添加IP,搜索“pmw”,添加“AXI_pwm_v1.0” IP核,并点击“Run Connection Automation”。

(2)导出“pwm”IP核的端口,保存设计,并“Generate Output Products”。

(3)添加“XDC”文件,把pwm_led输出端口分配给ZedBoard上的一个LED灯,编译生成Bit文件。

(4)点击Vivado “Flow Navigator”一栏里的“Generate Bitstream”,等待Vivado生成好bit文件后,在菜单栏“File -> Export -> ExportHardware…”导出硬件信息(.xsa文件),这里就包含了PS端的配置信息。该步骤如有疑问,可以参考以前的文章《ZYNQ串口打印输出——FPGA Vitis篇》。

3. Vitis工程的编写

(1)点击 Vivado 菜单“Tools-> Launch Vitis IDE”,启动 Vitis。

(2)新建 Vitis平台工程。Vitis工程的建立可以参考以前的文章《ZYNQ串口打印输出——FPGA Vitis篇》。

(3)新建 Vitis应用工程,创建一个名为“AXI_UserIPDemo”的工程,工程模板可以选择“Hello World”。

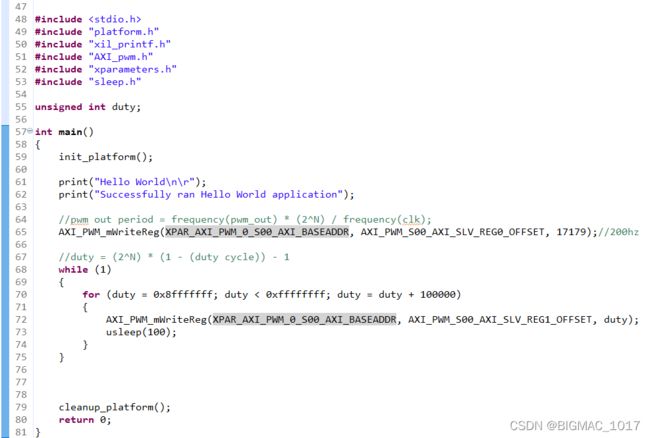

(4)在APP工程的目录下,可以找到对应我们开发IP的AXI_pwm.h的文件,这个头文件里包含里对自定义IP寄存器的读写宏定义。

(5)在“helloworld.c”文件中,修改“main”函数。我们先通过写寄存器 AXI_PWM_S00_AXI_SLV_REG0_OFFSET,控制PWM输出频率,然后通过写寄存器AXI_PWM_S00_AXI_SLV_REG1_OFFSET控制PWM输出的占空比。

(6)编译工程,将工程下载到硬件板卡上(编译和下载方式见《ZYNQ 串口打印输出——FPGA Vitis篇》)。

实验结果为: 板卡上的LED0灯呈呼吸状亮灭;

A. 工程源码下载

如果大家对我们的文章感兴趣,可以关注我们的公众号:“FpgaHome”:

该工程对应的源码可以通过关注该微信公众号,在公众号输入 ZYNQ_UserIP 来获取工程的下载链接,工程采用的是Vivado2021.1版本。

参考文献:

[1] http://www.alinx.com.cn/.

[2] Zynq-7000 SoC Technical Reference Manual(UG585). Xilinx官方文档

[3] ZYNQ 串口打印输出——FPGA Vitis篇. 图灵研究院