1、验证1101序列(Moore)

题目要求:

用Moore型状态机验证1101序列。

题目描述:

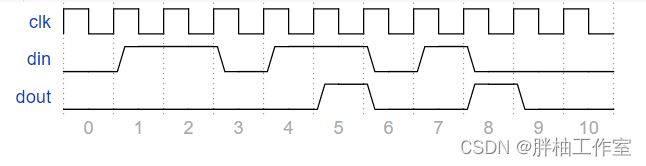

用使用状态机验证1101序列,注意:允许重复子序列。如图

端口描述:

module moore_1101(

input clk,//时钟信号

input clr,//reset复位信号,高电平有效

input din,//输入序列

output dout //输出结果

);

方法一:状态机的通用解法——基础状态转移方程

module moore_1101(

input clk,//时钟信号

input clr,//reset复位信号,高电平有效

input din,//输入序列

output reg dout //输出结果

);

reg [2 : 0] curr, next;//状态保存

parameter temp = 3'd0, s1 = 3'd1, s2 = 3'd2, s3 = 3'd3, s4 = 3'd4;

always @ (posedge clk) begin

if (clr) curr = temp;

else curr = next;

end//这一段需要用阻塞赋值

always @ (*) begin

case(curr)

temp: next <= din ? s1 : temp;//闲置状态

s1: next <= din ? s2 : temp;//已有一个1的状态,再得到一个1进s2,得到0则进闲置

s2: next <= din ? s2 : s3;//已有11的状态,再得到1进s2,得到0进s3

s3: next <= din ? s4 : temp;//已有110的状态,再得到一个1进s4,得到0进闲置

s4: next <= din ? s2 : temp;//已经1101,再得到一个1进s2,得到0进闲置

endcase

end//状态转移

always @ (posedge clk) begin

if (clr) dout <= 0;

else dout <= ((curr == s4) ? 1 : 0);

end//这一段可以用阻塞赋值也可以用非阻塞赋值

endmodule

方法二: D触发器灵活得出状态转移方程

假设需对 n n n位序列进行检测,则最多需要 n n n个 D D D触发器(很好理解,最多的情况就是储存全部信息,每位一个 D D D触发器)

以四位为例,于是有D触发器 D 0 , D 1 , D 2 , D 3 D_0,D_1,D_2,D_3 D0,D1,D2,D3,现态为 q 0 , q 1 , q 2 , q 3 q_0,q_1,q_2,q_3 q0,q1,q2,q3。

显然状态转移方程为

D 0 = c i n D_0= \rm cin D0=cin

D 1 = D 0 D_1=D_0 D1=D0

D 2 = D 1 D_2=D_1 D2=D1

D 3 = D 2 D_3=D_2 D3=D2

注意:如果状态转移方程不显然,则需严格按照设计状态-状态化简-状态转移真值表-状态转移方程过程进行来得出转移方程,相关内容在数电-同步时序电路。

module moore_1101(

input clk,//时钟信号

input clr,//reset复位信号,高电平有效

input din,//输入序列

output dout //输出结果

);

reg q3 = 0, q2 = 0, q1 = 0, q0 = 0;

always @ (posedge clk) begin

if (!clr) begin

q0 <= din;

q1 <= q0;

q2 <= q1;

q3 <= q2;

end

else begin

q0 <= 0;

q1 <= 0;

q2 <= 0;

q3 <= 0;

end

end

assign dout = (({q3, q2, q1, q0} == 4'b1101) ? 1 : 0);