ic验证简单面试题

自我介绍:

转行的原因

- 当然是发展的前景,往后的时间内IC行业的发展好。

- 针对于我个人而言,我觉得编码运行通过的感觉很爽。

- 最后就是薪资的水平普遍高于传统的制造业。

MCDF 如何提高覆盖率:

最终的总结,就是通过以上的学习

1.通过修改约束和创建新的条件进行测试

2.或者写新的测试来进行测试

3.创建conner case来进行测试

4.对于我们不需要的覆盖率,通过exclude的方式进行排除,也可以提高覆盖率的收集

5.使用不同的随机种子来进行测试(也就是说(随机测试+定向测试)

4.对于代码覆盖率:line、paths、toggle、FSM这几个的行覆盖率。

代码覆盖率的成果:

1.通过对MCDF 编写MCDF的测试用例使得寄存器的读写测试覆盖率达到100%

2.通过对异步fifo的读写寄存器编写,使得FIFO的代码覆盖率达到90%以上,

其中的一个难点就是:

1.分支覆盖率没有满足:回头review代码,发现满状态下写没有满足。

2.toggle覆盖率没有满足,是因为randmoize的次数不够。

验证点:

寄存器的读写测试

寄存器的稳定性测试

数据通道的开关测试

优先级测试

下行从端低带宽测试

APB协议

1.APB有8个信号: clk与rst信号、psel片选信号与penble使能信号、pwrite读写信号(高为写入、低为读出信号)、paddr 地址位、还有padta与rdata信号

2.APB:有3个状态、idel状态、setup状态与enable状态,各个状态的使能拉高情况

3.APB的VIP实现的功能,有slave、maser连个agent。agent中有dr、mon、sequencer、等。从master—driver中发的数据,直接传输到slaver-DRIVER

中的一个小的men然后与test中的men进行比较。

实现了读操作、写操作、先读后写和先写后读的操作。连续写再连续读的操作。

断言分为:

立即断言:非时序的,如同过程语句、可以在initial过程块中执行

并行断言:proporty为关键字,与时序有关。他们可以与设计模块一同执行。

先定义sequence,然后在定义proprety。

比如:

psel信号拉高的时候penable不能为x。

psel信号拉高的上一个周期,penable为高。

penable拉高的下一个周期,penable应该为低。

psel与pwrite同时保持为高的阶段,pdata需要保持。

对同一个地址做两次写操作再从中读数据。

写操作时,先分别发生连续写和非连续写。

当然我写的case比较简单,所以覆盖率也达到了100%。

AHB总线的协议:

1.AHB中包括master、slave译码器与编码器,

有两个类型的突发操作:增量突发、回环突发。

基本传输:包括地址相位与数据相位。地址相位只存在单个周期。数据相位:可存在多个周期,这里通过HREADY信号实现。

HTRANS[1:0],有四种状态。空闲、忙、非连续、连续的传输。

突发操作由HBURST的来表示SINGLE 单一传输 \INCR4\8\16突发传输 \WRAP4\8\16增量回环。

Router

于这里是sa是固定的端口,而da是随机的端口。所以实现了,由不同的端口向不同的端口传输数据的实现。

在scoraboard中可以表示出先将driver中的数据push_back到队列中,之后根据pak中的da的值与reciver中的匹配,然后进习性比较。

也收获了关于覆盖率。可以将覆盖率100%作为表示将每一个端口都覆盖到。

0-15一共是16个端口进行操作从一个端口写,在另一边的端口读出数据,进行比较。看内容是否一样,发数的端口属于轮寻的机制,就是在这边写完在另一边进行读数据,读的端口是随机的,所义randmoize的次数需要足够才可以。

PCIE

物理层(PhysicalLayer)。电力方面,使用两个单向的低电压差分信号实现数据传输。也承担8b/10b的数据解码。

2 数据链路层(DataLink Layer)。对该层传输的TLPs进行组装和分拆。为上下两层服务。

3传输层(TransactionLayer)。接受从软件方面送来的请求,并生成请求包传输到数据层时接受从数据链路层来的数据包,传递给软件。也就是对TLPs进行分装和组装。

多时域设计中,如何处理信号跨时域?

不同的时钟域之间信号通信时需要进行同步处理,这样可以防止新时钟域中第一级触

发器的亚稳态信号对下级逻辑造成影响。

信号跨时钟域同步: 当单个信号跨时钟域时, 可以采用两级触发器来同步; 数据或地址

总线跨时钟域时可以采用异步FIFO 来实现时钟同步;第三种方法就是采用握手信号。

MOORE 与MEELEY 状态机的特征?

Moore 状态机的输出仅与当前状态值有关, 且只在时钟边沿到来时才会有状态变化。

Mealy 状态机的输出不仅与当前状态值有关, 而且与当前输入值有关。

建⽴和保持时间

建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间如

果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;

保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间果

保持时间不够,数据同样不能被打入触发器。

寄存器的前后门访问的区别与联系!

Dut是如何与interface连接到一起的

Message的几个冗余程度:low mediem high none full debug

Set_report_verbosity_level_hire

还有是关于memary的储存的方式是怎么样的?

异部fifo的功能测试点的描述。

1. 简单阐述一下你的这个MCDF项目,他是怎么运作的。MCDF的验证平台与其他的是有什么区 别。是否有用到总线,他们是如何相连接的。是用SV集成的还是通过MCDF集成的?reference modle是如何收集数据的?

(1)寄存器控制3个channl的开关、arbiter的优先级、还有formater的发包的长度

叫做多通道数据整形器。

由于设计分为了3个channel slave、一个arbiter、一个formater、一个register

所以我们的tb设计成了4个package。对应各个模块。

最重要的一个package为mcdf_package.主要是包含了各个sequence和test、ref_model

还有checker。

(2)Ref model是通过mailbox在各个3个发送数据的channel和reg agent中将数据通过reference model中,通过model,出来的数是完全按照formater的逻辑出来的,最后通过out-mailbox放入compare中formayter中monitor中检测到的数据进行比较

(3)在uvm中也是通过在mailbox做了buffer将channel和reg的uvm-blocking_port

- Gvim的操作模式,搜索是如何让写的。

/***

- Linux的搜索是怎么搜索的。他里面的数据的权限是如何让进行修改的。

Gerp …* find

- Dut是如何与interferce相连接的band是什么。

通过interferce在我们的dut中进行实例化。

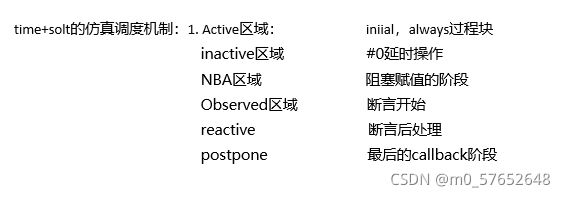

- Phase的12个小的phase是如何执行的。Main phase与run phase的区别

并行执行的,12个小的phase是顺序执行的,当所有的都执行完,才后跳转到下一个phase。Reset、confige、main、shutdown。

9大·phase:build、connect、end of elab、start of elab、run、extract、check、report、final。

- Function与task的区别,在forkjoin里面可以执行function可以调用task。

- Logic与wire和reg的区别是什么与联系是什么。

wire表示导线结构,reg表示存储结构。

wire使用assign赋值,reg赋值定义在always、initial、task或function代码块中。

wire赋值综合成组合逻辑,reg可能综合成时序逻辑,也可能综合成组合逻辑。

单驱动时logic可完全替代reg和wire,除了Evan提到的赋初值问题。

多驱动时,如inout类型端口,使用wire。

- Prority的测试你是如何发的。

在checker中设定了一个任务,直接在dut抓取到优先级最高的信号(此时arbiter的优先级最高,通过这个req的信号拉高得到,最高的优先级的channel的id,然后再放到另一个task内看对应的ack信号是否为高)(arbter的interferce里面有信号ack),在这里面是新建了一个接口

- 与reference module是如何相连接的。

是在test中例化,然后create+ configu+build+lockmodel(锁定模型,不允许加入新的寄存器)+reset(复位)+rgm.default_map.set_sequencer(env.bus_agt.sqr,reg_sqr_adapter)通过set_sequencer函数将其连接在一起。

- Linux下面的搜索你是如何去搜索的。

参照上面。

- 写一个程序找出100以内的所有质数。

i=2

for i in range(2,100): # 取i从2开始,2 最小的质数

for j in range(2,i): #j在i的范围内取,range区间取不到i,看i是否有其他因数

if i%j==0:

break

if i%j!=0: #最好用if 如果用else不规范

print(i)

- 异步的fifo都分为哪几个模块。

- 将计数器跟空满的信号关联起来

- 计数器的模块,采用counter的计数器,分为4个模块,同写同读、只读、只写、不独不写、

- 写入数据和读出数据时,将数据放入men中

- 读写状态下的指针变化情况。

- 各个变量的数据类型都是什么,我们在tb里面写的数如果传到dut里面,这里的所有的变量是如何让进行转换的。

通过interferce中的logic进行转换

- Fork join/fork join_none / fork_join_any的区别是什么。

Join_none代表块内和块外的内容都是同时执行的

- Verilog中的代码是如何实现fip-flop的也就是D触发器的。

Module DFF(q,clk,data_in);

Output q;

Input clk,data_in;

Reg q;

Always @(posedge clk) q<=data_in;

Endmodule

- 寄存器模型写一下?

由reg_filed、 uvm_reg、 uvm_reg_block这三个块所构成。

- Reg map与reg block的区别是什么?

每个寄存器在加入寄存器模型之后都有其对应的地址,map就是储存这些地址,并将其转化为可以访问的物理地址。

- Fifo的空满的覆盖率你是如何描述的。

直接写进去16个数,在读出来16个数,这样就知道了FIFO的空满状态。得出结论。

- Vcs在仿真的时候都经历娜3部,编译的时候生成了simv的文件然后编译器才会仿真

Makefile是如何让生成的。。

Vlogen vcs simv

- Ahb的burst的总线操作是什么样的。如果连续发了两个数的话,burst信号是如何发生变化的。。

- 阻塞和非阻塞赋值的联系与区别是什么?用什么符号进行表示的。

阻塞= 常用于组合逻辑电路。需要等上一条执行完了在执行下一条命令。

非阻塞<=常用于时序逻辑电路,不需要等,都是同时执行。

- 描述一个简单的时钟产生信号。是用什么样的赋值语句实现:<=是非阻塞赋值实现的。

- Assign和always的区别。

Assign用于组合逻辑电路,不可综合 wire型,开始就执行。

Always用于时序逻辑电路。可综合 reg型 等always块中有时序变化的时候可以执行

- Class的子类可以继承于class的父类的哪些东西

方法和属性。

- 如果是virtual class呢

Virtual task与virtual function的区别:v如果使用了virtual 那么父类的句柄可以直接调用子类的改写之后的方法。

Virtual class的方法我们可以得出一个结论,就是,可以被扩展但是不可以被实力化的类。

- 约束里面的solve before

Solve X before Y 代表的是关于先解决X的·分布概率,在解决Y的分布概率。

- 异或的工作原理是什么

相同为0,不同为1

- Router的运行原理是什么样的?

- 如何将·APB-UVC和UART-UVC,集成到验证环境中去?

例化

- 三分频和二分频的verilog实现

采用计数器

- Makefile后面的编译命令都是什么意思

- 跨时钟域CDC的基础概念:FIFO 格雷码

- FIFO为啥会打慢了3拍,1拍是由于读指针需要用wclk来进行同步。

读指针需要用写时钟同步,同步了一拍

异步的空信号同步到读时钟,经过了两个d触发器,同步了两拍

Conpnent与object的区别:?

- 有无phase

- Component是一直存在的,而对于component的不一样的

- 有无parent,New函数是否一样

- 继承的关系,component是继承于object的,object是继承于void的

哪些是component哪些是object?

Object:sequence 、sequence_item、config

Component:driver、monitor、scoreboard、agent、test 、reg、adapter、sequencer、

Config#db的作用是什么?

Uvm中为什么要phase机制?

目的就是用来做不同的component做同步的。

哪些是重上到下的phase,哪些是从下到上的?

Bulid是从uvm_void,开始重上致下。是从上往下派生的。

Connect的参数是parent,所以是从下往上长的

一种sequence只能是sequence item

Filed automation的标志位的使用:

`uvm_component_utils_begin

Copy与colne的需要写一些utils begin utilus end的区别。

表示的是这样的是写一些,copy和colne的说明。

Compare、pack、pack_byte

`uvm_component_utils_end

Apb的信号的只需要两个周期。

Idel、setup、ENABLE三个状态

Uvm中是如何开始的,如何结束的?

会检查phase中有无raise_objection提起,必须要在消耗时间的语句之前完成。

Drop_objection的时候代表仿真的结束。

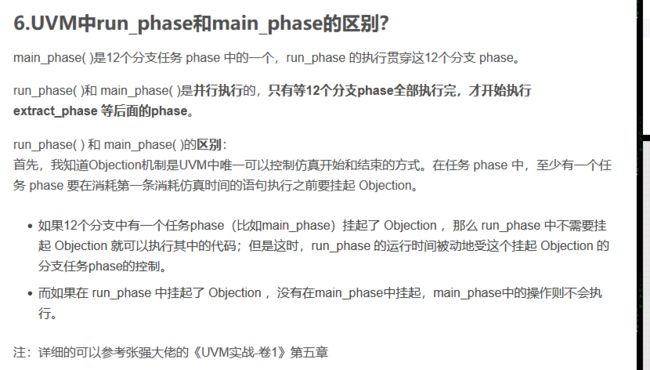

Run-phase与main_phase的区别?

main_phase执行run_phase一定会执行的,反过来不会执行。

Sequence和driver的握手机制?

- sequence_item port sequence_item_export

有两种方式:1.通过driver中的put_response(rsp)、和sequence中的get_response(rsp).

- 在driver中调用seq_item_port.item_done(rsp);

俩步的关键就是设定rsp.set_id_info(req).这个函数将req的id信息复制到rsp。

uvm可重用性性主要是要用uvc的sequence

Function与task的区别:

- function必须与module公用一个timescale而对于task可以定义自己的。

- function有返回值而task无返回值。

- function至少有一个输入变量,而task可以没有或者有多个任意类型的变量。

- task消耗时间而function不消耗时间。

#

I2c与apb的时序图是如何画的?

APB与URAT的接口是如何做的?

解释一下config函数的各个参数的意义:(能不能写出来)

Config#db(virtual interfere)::set(uvm_root::get(),”uvm_test_top.uart_env*”,”vif”,”apb_vif”)

多态:

不同的子类,在继承父类的方法之后,分别都重写,覆盖了父类的方法,即父类的同一方法在,在继承的子类中出现了不同的形式。所以多态和继承是密不可分的。

当一个父类被扩展之后,其所有的变量和方法(local)的除外,都会被其扩展类所继承。

一般情况下,父类是不会访问派生类的重写和新增的部分的,假如希望重写的方法被看到,就需要依靠虚方法和多态。

I2C与UART总线的区别:

区别主要是:I2C可以1对多,而U只可以一对一的发

12c接口带有同步时钟,而uart没有,所以对时钟的要求远不如uart那么高。

波特率是指每秒可以传输9600个bit位

25Mhz=25000000/9600*16=162.7604.

常见的波特率有1200、2400、4800、9600、19200.这几种。

覆盖的操作是什么?

Set_type_override();

同步复位与异步复位怎么写

同步always@(posedge clk)

优点:1. 一般能够确保电路是百分之百同步的

- 确保复位只发生在有效时钟沿,可以作为过滤掉毛刺的手段

缺点:1.复位信号的有效时长必须大于时钟周期

2.由于大多数的厂商目标库内的触发器都只有异步复位端口,采用同步复位的话,就会耗费较多的逻辑资源

异步always@(posedge clk or negedge rst_n)

优点:1.异步复位信号识别方便,而且可以很方便的使用全局复位;

2.由于大多数的厂商目标库内的触发器都有异步复位端口,可以节约逻辑资源

异步复位缺点:

1.复位信号容易受到毛刺的影响;

2.复位结束时刻恰在亚稳态窗口内时,无法决定现在的复位状态是1还是0,会导致

Apb-uart画一下apb的协议?

Config#db如何去写?里面的参数都有什么意义?写一下你这个项目里面用到的都是如何去用的?

Uvm中的compnent的上一层是什么,他是怎么来的,再上一层是什么?

如何再linux下写一段话,把下面的.C文件替换为.cpu文件?

写一下同步fifo 10010序列状态检测机?