AD9361 介绍 (中)

AD936x 系列快速入口

校准、数据接口 (CMOS) 在AD9361 介绍 (下)

MGC、Slow AGC、Fast AGC补充: AD9361 补充(上)

通过AD936x Evaluation Software加深了解: AD936x 配置软件介绍 上

文章目录

- 六、 增益控制

-

- 6.1 增益表

-

- 6.11 Full table

- 6.12 Split table

- 6.13 digital gain

- 6.2 增益控制模式

-

- 6.21 MGC

- 6.22 Slow attack AGC

- 6.23 Fast attack AGC

- 6.3 增益阈值检测

-

- 6.31 LMT overload detector

- 6.32 ADC overload detector

- 6.33 digital saturation

- 6.34 LOW power threshold

- 6.35 average signal power

- 6.36 peak overload wait time

- 6.37 settling delay

- 七、 时钟和PLL

-

- 7.1 DCXO

- 7.2 RF PLL

- 7.3 BB PLL

- 八、Enable state machine

-

- 8.1 SPI 控制

- 8.2 ENABLE/TXNRX 引脚控制

-

- 8.21 脉冲模式

- 8.22 电平模式

- 8.3 FDD 独立控制

-

- 8.31 FDD 独立控制 电平模式

- 8.32 FDD 独立控制 脉冲模式

六、 增益控制

AD9361有几种增益控制模式,AGC (automatic gain control)模式适用于时分双工(TDD)和频分双工(FDD)场景,也有手动增益控制(MGC)模式,BBP可以控制接收机的增益。

- ad9361_set_rx_gain_control_mode函数可以配置所有的增益控制模式。

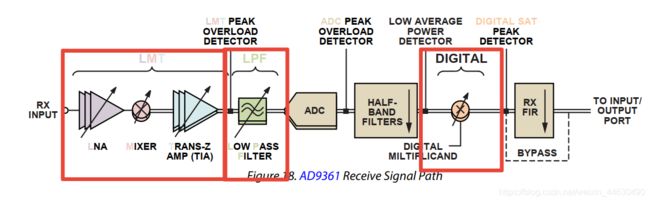

如上图所示,AD9361接收信号的路径可以被分割成几个块,几乎所有块的增益都是可变的。

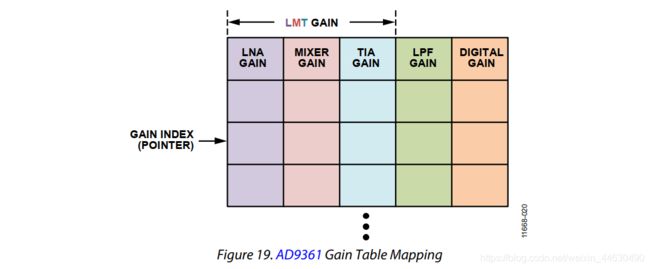

如上图所示,每个接收通道都有自己的增益表,AD9361使用指针指向增益表中的一行,该行包含每个独立增益模块的增益值。增益索引(指针)映射到一组增益值(每个增益块的)。增益表将增益控制字映射到每个可变增益模块,指向表的指针确定发送到每个块的控制字值。无论使用自动增益控制(AGC)还是手动增益控制(MGC),指针都会在表格中上下移动,从而改变上图所示的一个或多个模块的增益。

- AD9361有两种不同的方法来实现增益表。在全表模式下,有一个表用于接收。在分离表模式下,AD9361将LMT和LPF表分离开,并用独立的指针控制。如果digital gain使能,有第三个独立控制的表,也有自己的指针,每个接收通道都有自己的一组两个(或三个)表。增益表模式在ad9361_load_gt函数中设置。表架构影响所有增益控制模式(AGC、MGC),并且是两个接收通道的通用设置。

6.1 增益表

6.11 Full table

全表模式下单个增益表包含Rx信号路径中的所有可变增益模块,上图显示了完整增益表的一部分。该图还显示了每个增益索引(如LPF INDEX)旁边的每个模块的增益。如果指针向上或向下移动,一个或多个块的增益都将改变,如果增益指针向下移动一步(55指向索引54),LNA增益和LPF增益都将改变。这可以使AD9361能够处理变化很大的电平信号,同时仍能优化噪声系数和线性度。

- 使用ad9361_get_rx_rf_gain函数可在任何增益控制模式下得到全表增益索引

- 最大LMT/Full 增益寄存器限制允许的最大索引。

6.12 Split table

在经常出现高功率带外干扰信号的情况下,可以拆分增益表来优化存在这些干扰时的噪声系数,使用独立的指针控制LMT增益和LPF增益以及digital gain,这可以区域性的改变接收路径中过载部分的增益。而对于全增益表,无论过载发生在哪里,增益变化时都会影响接收路径中的其他增益模块。

-

LMT表的架构取决于所使用的增益控制模式,在增益控制模式中介绍。必须使用ad9361_load_gt函数将LMT表写入AD9361。

-

LPF表本身不存在,LPF索引直接转化为LPF的增益(分贝),LPF增益范围从0到24(d)。数字增益也是索引直接转化为增益,增益范围从0到31(d)。

AD9361的总增益(单位为分贝)不一定等于LMT和LPF索引之和。LMT级的实际增益随本振频率 LO而变化,另外,一些LMT步长大于1分贝。因此,将LMT索引改变1可能不会将增益改变1 dB。

- 使用分离表模式时, LMT表最大索引为40(d)。

- 在任何增益控制模式下回读分离表增益索引,使用ad9361_get_rx_rf_gain函数。

6.13 digital gain

所有增益控制模式(MGC、AGC)和两种增益表模式(全表模式、分割表模式)都允许增加数字增益,最大数字索引为31(d)。

全增益表的最大允许索引为90(d),仅含模拟增益的标准全增益表的最大索引为76(d)。对于ADI公司提供的增益表,剩下24(d)个索引用于数字增益。替代增益表(在索引低于76(d)时达到了最大模拟增益)可以容纳更多数字增益步长(最高31)。

- digital gain不会增加信噪比,因为它只是乘以一个因子,噪声和信号都增加了,因此信噪比保持不变。如果修改增益表,牺牲模拟增益来增加更多的数字增益将降低系统的性能。

- 对于许多应用,不需要数字增益。 如果BBP希望接收的信号功率等于某个标称值,采用最大模拟增益后仍不足以达到的极低电平信号,可以使用数字增益。

6.2 增益控制模式

MGC、Slow attack AGC、Fast attack AGC详细介绍在 AD9361 补充(上)

6.21 MGC

在MGC模式下,BBP控制增益索引指针,这个模式通过ad 9361 _ set _ rx _ gain _ control _ mode函数设置。最简单的形式是,BBP通过评估 I/O口的信号电平(除了接收到的数字信号电平,BBP不需要其他信息),然后适当调整增益。

AD9361具有可编程阈值,可指示各接收链路的信号状况,将这些信号路由到控制输出引脚,然后将它们连接到BBP,BBP能够更详细地确定接收信号的状态。对于分割增益表,依据接收信号(可指示过载发生的位置LMT , LPF , digital),BBP可以调整过载区域的增益。

6.22 Slow attack AGC

Slow attack模式旨在缓慢改变信号,比如某些FDD应用场景—WCDMA和FDD LTE。 slow attack AGC使用具有滞后的二阶控制环路将平均信号功率保持在可编程范围内。功率在HB1和Rx FIR滤波器之间测量。

- BBP可通过设置位,对超过 LMT 和 ADC阈值的信号做出更快的反应。利用ad 9361 _ set _ rx _ gain _ control _ mode函数使能AGC Slow attack模式。

6.23 Fast attack AGC

Fast attack AGC 模式适用于突发的波形,如TDD或GSM/EDGE FDD应用。AGC在突发开始时对过载做出非常快速的响应,以便在信号的数据部分到达时AGC能够稳定在最佳增益索引。AGC还有一个可选的缓慢衰减,当AGC锁定在最佳增益时,如果信号功率降低,则允许增益增加。

- Fast attack AGC通过ad 9361 _ set _ rx _ gain _ control _ mode函数配置。

6.3 增益阈值检测

AD9361使用检测器来确定接收信号是否使特定模块过载,或者信号是否降至可编程阈值以下。LMT和ADC过载检测器(也称为峰值检测器)可以对几乎瞬时的过载信号做出反应。检测器在信号路径中的位置如上图所示。

6.31 LMT overload detector

LNA/混频器/跨阻放大器过载检测是一种模拟峰值检测器,用于确定接收信号是否使模拟低通滤波器之前的模块过载。如果发生LMT 过载,但ADC没有过载,这可能表明带外干扰信号导致过载情况。

- 有两种不同的LMT过载阈值,一种用于指示较大的过载,另一种用于指示较小的过载。两个阈值均可编程,并在ad 9361 _ set _ rx _ gain _ control _ mode函数中配置。

- 小阈值应该被设置为低于(或等于)大阈值,因为AGC 将根据哪个阈值被超过而受到不同的影响。在MGC模式下,BBP可以通过控制输出引脚监测过载标志。

6.32 ADC overload detector

该ADC是一个高度过采样的sigma-delta调制器(SDM),输出范围为+4到-4。由于ADC高度过采样,ADC时钟速率比接收信号采样速率快得多,需要抽取和低通滤波产生数字信号。当ADC过载时,其采样和输入信号之间的误差将导致ADC输出更多值为+4或4的采样信号。

- ADC最大输入(0 dBFS)为0.625 V峰值。然而,为了避免压缩,ADC的最大推荐峰值输入电平为0.5 V,比满量程低1.9dB。

下图显示了 ADC过载检测器如何处理信号以及如何使用阈值

有两个可编程阈值,都在ad 9361 _ set _ rx _ gain _ control _ mode函数中配置。两个接收通道的阈值是相同的。平方和计算中使用的样本数也在ad 9361 _ set _ rx _ gain _ control _ mode函数中设置。将平方和的结果值z与两个阈值进行比较,如果超过特定阈值,则设置一个标志。在MGC模式下,BBP可以通过控制输出引脚监测过载标志。

6.33 digital saturation

和LMT和ADC过载一样,AD9361使用计数器 (Dig Saturation Exceeded Counter)来确定digital saturation发生的次数,如果超出,增益索引会降低。

6.34 LOW power threshold

低功率阈值是以-dBFS为单位进行测量的绝对阈值,分辨率为0.5 dBFs/LSB。范围为0 dBFS至-63.5 dBFS。该值通过ad 9361 _ set _ rx _ gain _ control _ mode函数进行配置。

- AD9361在fast attack AGC 模式下使用该阈值,也可以在MGC模式下使用

- 在fast attack AGC 模式下,平均信号功率(见6.34) 降至低功率阈值以下后,低功率标志不会立即置位。只有当信号功率在增量时间内一直保持低于低功率阈值时,该标志才有效。增量时间值以ClkRF周期(接收通道FIR滤波器输入端使用的时钟)为单位进行测量。

- 在MGC模式下,只要功率降至低功率阈值以下,低功率标志就会马上置位。

6.35 average signal power

测量功率时(如低功率阈值),测量值是由功率测量期间抽取的一定数量样本的平均值。两个接收器的持续时间相同。在每个测量周期结束时,平均信号功率值会更新。

- 在增益改变后,AD9361必须复位过载检测器和功率测量电路,并等待接收路径稳定,然后重新启用检测器和功率测量块。

- 测量持续时间实际以 Rx sample periods 计 ,如上图所示,范围:0到16*32768=524288个

6.36 peak overload wait time

所有增益控制模式都使用峰值过载等待时间。在增益改变后,AD9361等待该寄存器设置的时间,使模拟路径中的信号和ADC稳定下来,然后重新使能它的LMT和ADC过载检测器。默认值适用于所有应用程序,除非带有旁路模式的外部LNA是信号路径的一部分。峰值过载等待时间由ad9361_set_rx_gain_control_mode函数设置,并以ClkRF(Rx FIR滤波器时钟速率的输入)计时。

6.37 settling delay

所有 AGC 模式都使用建立延迟,即增益变化后 AGC 将功率测量模块保持在复位状态的时间。功率测量发生在接收HB1滤波器的输出端(接收FIR滤波器的输入端),因此在增益改变后功率测量恢复之前,Rx FIR之前的所有级都必须建立。

- 延迟等于寄存器值乘以2,并以ClkRF速率计时。建立延迟的默认值为20个ClkRF周期,这是基于30.72 MHz的ClkRF速率。为了获得最佳的 fast attack AGC性能,延迟需要根据ClkRF进行调整。

七、 时钟和PLL

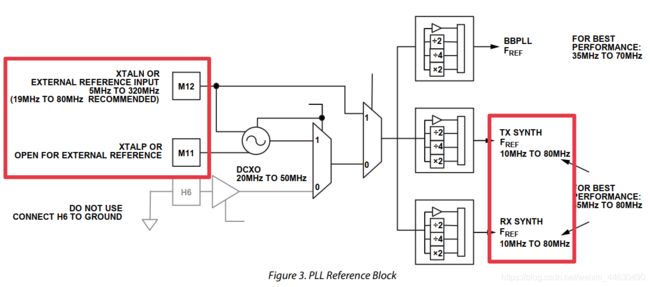

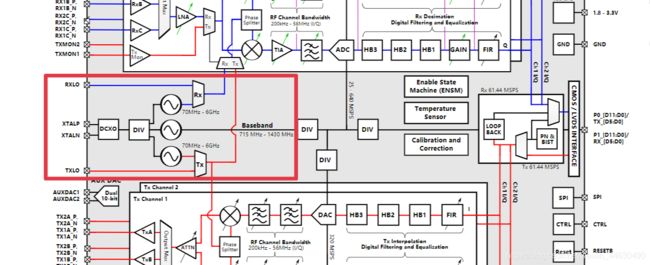

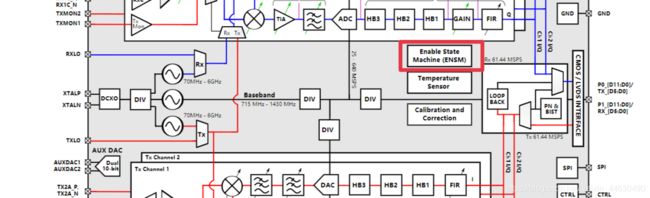

AD9361使用分数分频锁相环(PLL)来产生发射机和接收机本地振荡器(LO)频率,以及BB PLL(baseband PLL)。BB PLL 可用于数据转换、数字滤波器和 I/O 端口。

PLL的参考时钟可以由外部振荡器或外部晶体(XO)和数字可编程片内可变电容提供,电容微调产生参考时钟频率,XO和微调电容的组合统称为DCXO。

7.1 DCXO

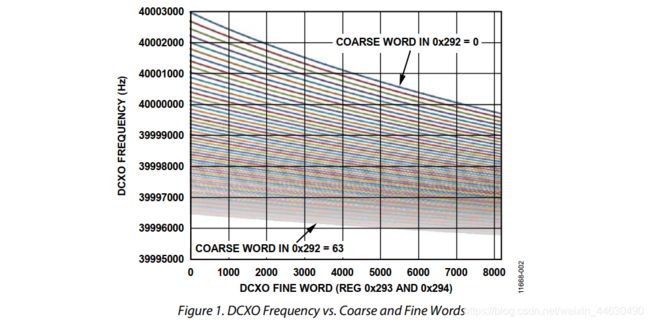

通过调整AD9361中的电容,可以调整产生的DCXO频率,以补偿XO频率容差和稳定性。DCXO的分辨率随coarse word而变化,最差分辨率(coarse word= 0)为0.0125 ppm。DCXO可以使用coarse word和 fine word,在±60 ppm范围内改变频率。

上图为一XO(标称40MHz)的DCXO频率随fine word和coarse word的变化图,横轴为fine word,纵轴是频率,每条线的分辨率随coarse word变化。

使用bench测试确定标称DCXO微调字,在初始化期间使用。这些标称字应该在BBPLL校准前写好。初始化后(BBPLL和RFPLL编程、校准和锁定后),DCXO字可以随时写入。

- XTALP/XTALN:参考频率 REF_CLK晶振连接。使用晶振时,将其连接于这两个引脚之间。使用外部时钟源时,将其连接至XTALN,使XTALP保持断开。

- 第一个选择是使用一个专门的晶振,其频率在19 MHz和50MHz之前,连接于XTALP和XTALN引脚之间。

- 第二个选择是将一个外部振荡器或时钟分配器件(如AD9548)连接至XTALN引脚(其中, XTALP引脚保持断开状态)。如果使用外部振荡器,则频率可在10 MHz和80 MHz之间变化。

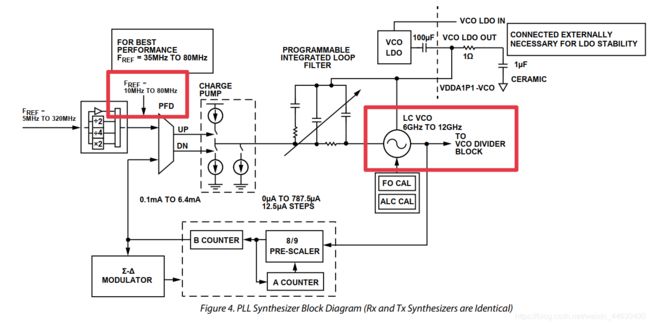

7.2 RF PLL

AD9361含有两个完全相同的频率合成器,用于为RF信号路径生成需要的LO信号:一个用于接收器,一个用于发射器。锁相环(PLL)频率合成器采用分数分频,融入了完全集成式电压控制振荡器(VCO)和环路滤波器。

REF_CLK频率可以通过DCXO产生,或者外部时钟源向器件提供,多路复用器选择所需的信号源。然后,REF_CLK被分离并加到三个独立的调节模块,也称为REF分频器。调节模块提供四种选择——/2 、*2 、/4 、*1,可以得到F_REF为10MHz到80MHz

由锁相环频率合成框图可知,锁相环工作范围6 GHz至12 GHz,并输入VCO 分频模块。

LO频率范围从47 MHz到6GHz是通过分频锁相环频率创建的。

- Rx PLL使用ad9361_set_rx_lo_freq函数配置和校准,Tx PLL使用ad9361_set_tx_lo_freq函数配置。每个合成器必须单独配置和校准。

7.3 BB PLL

AD9361中的BB PLL频率合成器,用于生成所有与基带相关的时钟信号,包括ADC和DAC采样时钟、 DATA_CLK信号(见后续“数据接口”部分)、数字滤波器和 I/O 端口等。

- FREF在35MHz到70MHz之间。

- 该PLL的频率编程范围为715 MHz至1.430 GHz,具体取决于系统的数据速率和采样速率要求。BB PLL输出到可编程分频器链,来产生所需的采样率和总线通信速率。

- 所需的BB PLL频率通常通过反算得到,然后选择适当的分频器,以使BB PLL能够在范围内工作。

八、Enable state machine

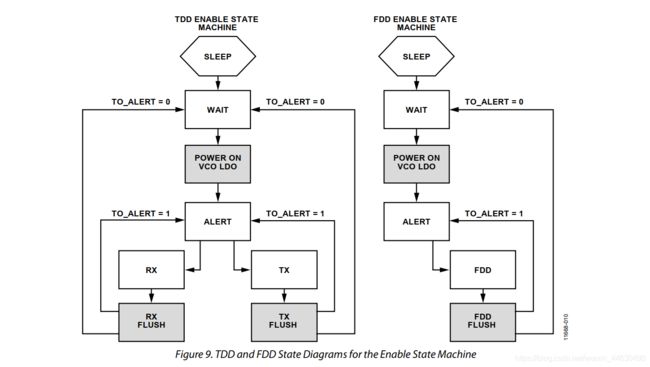

AD9361收发器有一个使能状态机(ENSM),可以对器件的当前状态进行实时控制,ENSM有两种可能的控制方法——SPI控制和引脚控制。

AD9361收发器有一个使能状态机(ENSM),可以对器件的当前状态进行实时控制,ENSM有两种可能的控制方法——SPI控制和引脚控制。

1)通过SPI写寄存器将当前状态推进到下一个状态,可以异步控制ENSM。

2)使用ENABLE和TXNRX引脚实时控制当前状态。

上图中灰色状态不需要用户控制,经过设定的时间后进入下一个状态。TO_ALERT位在ENSM配置寄存器中,如果要切换到WAIT状态,需要在RX或TX状态下清除TO_ALERT位,这样从 Rx, Tx或FDD状态移出时,ENSM将转移到WAIT状态,如果TO_ALERT被置1,ENSM将转换到ALERT 状态。

- SLEEP状态是指禁用AD9361时钟的状态,要进入SLEEP状态,先转换到WAIT状态,然后禁用BPLL寄存器中的AD9361时钟。

- FDD模式下,TX、RX频率综合器在ENSM从WAIT进入ALERT状态或频率控制字写入时会进行校准。

- TDD模式与FDD类似,也会在ENSM从WAIT进入ALERT状态时进行校准,而在频率控制字写入时,会根据TXNRX判断,让当前使能的VCO进行校准。

8.1 SPI 控制

SPI控制默认是禁用,可以在ENSM配置寄存器中使能。一旦进入 ALERT状态,AD9361就会启用发射机和接收机的射频合成器,如果由于某些原因合成器没有正确校准,ENSM将无法转换到RX或TX状态,这样可防止AD9361发送或接收数据,从而保护无线频谱。

-

一旦进入 ALERT状态,射频PLL经过适当校准,ENSM就可以进入RX、TX或FDD状态。要从ALERT切换到RX,需要设置Force Rx On 位,要返回ALERT或WAIT,需要清除该位。

-

要从ALERT模式切换到TX或FDD模式,需要设置Force Tx On位,要返回到ALERT或WAIT状态,需要清除该位。

-

在FDD下,Force Rx On位被忽略,在TDD下,ENSM必须在RX和TX状态之间转换到ALERT状态,ENSM不能从RX直接移动到TX,或者从TX直接移动到RX。

8.2 ENABLE/TXNRX 引脚控制

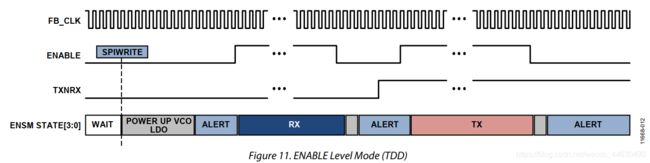

默认情况下,使用ENABLE/TXNRX引脚控制模式。ENABLE引脚可以通过脉冲或电平操作,将ENSM状态转换到下一个状态。

8.21 脉冲模式

在脉冲模式下,需要最小宽度为一个FB_CLK周期的脉冲来推进当前的ENSM状态。BBP发送一个ENABLE脉冲进入TX或RX状态或FDD状态(在FDD中,TXNRX的逻辑电平被忽略),然后再发送一个脉冲回到ALERT或WAIT状态。

在TDD中,TXNRX引脚的状态控制AD9361是从ALERT状态转换到RX状态还是从ALERT状态转换到Tx状态。

- 如果TXNRX为高电平,器件将进入TX状态。

- 如果TXNRX为低电平,器件将进入RX状态。

- TXNRX引脚电平在ALERT状态下设置,TXNRX的逻辑电平在RX、TX或FDD状态下不能改变。

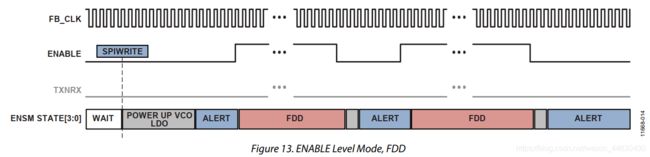

8.22 电平模式

在电平模式下,ENABLE引脚电平控制ENSM状态,ENABLE引脚的下降沿将AD9361器件置于ALERT状态,处于ALERT状态时,必须设置或清除TXNRX位。

- 如果TXNRX为低电平,ENABLE引脚的上升沿将AD9361移入Rx状态。

- 如果TXNRX为高电平,ENABLE引脚的上升沿将AD9361移入Tx状态。

在FDD中,TXNRX的逻辑电平被忽略,当ENABLE引脚拉回到逻辑低电平时,ENSM将退出RX、TX或FDD状态。如果To Alert 位为0,器件将从RX、TX或FDD状态进入WAIT 状态。

要在电平模式下从WAIT 模式切换到ALERT模式,对Force Alert State位执行 SPI写操作,或者BBP可以在ENABLE引脚上驱动一个脉冲。

- 如果使用ENABLE脉冲,其脉冲宽度必须大于一个FB_CLK周期。

- ENABLE脉冲的上升沿将ENSM状态从WAIT转到ALERT状态,在ALERT中,ENABLE脉冲的下降沿是被忽略的。

8.3 FDD 独立控制

8.31 FDD 独立控制 电平模式

当AD9361处于FDD模式时,FDD独立控制模式可以允许接收链和发射链独立使能。该模式通过设置FDD External Control Enable位(0x015[D7])来使能。

| 引脚电平 | 描述 |

|---|---|

| ENABLE=0,TXNRX=0 | Rx and Tx disabled |

| ENABLE=1,TXNRX=0 | Rx enabled, Tx disabled |

| ENABLE=0,TXNRX=1 | Rx disabled, Tx enabled |

| ENABLE=1,TXNRX=1 | Rx and Tx enabled |

FDD 独立控制状态下,使用SPI写将ENSM移动到FDD状态,然后,ENABLE和TXNRX引脚分别在内部重新映射为Force Rx On和Force Tx On,ENABLE和TXNRX的控制组合如上表所示。FDD 独立控制状态,根据ENABLE和TXNRX引脚电平,ENSM状态转移如下图所示。

在这种模式下,ENSM始终处于FDD状态,没有移动到FDD FLUSH状态,BBP必须在启用接收链后留出足够的时间让数字滤波器刷新,在发送数据后留出足够的时间让发送完成传输,同时需要我们控制好时间,在两次收或者发开启之间留下足够的时间清空残留数据。

8.32 FDD 独立控制 脉冲模式

在脉冲模式下,如上图所示,当使用SPI写操作从ALERT状态进入FDD状态时,接收和发送信号链开始时是禁用状态,直到接收到第一个脉冲。BBP应在ENABLE引脚上发送脉冲,以enable/disable接收信号链。TXNRX引脚上发送的脉冲将enable/disable 发送信号链。

从参考手册和寄存器手册等资料学习总结,如有不对的地方,欢迎大家在评论区指正,非常感谢!