Synopsys DW_apb_i2c_databook 笔记

第二章 功能描述

2.1概述

每个设备有唯一地址,具备收发功能;

超快模式设备不向下兼容,不应纳入传统的I2C速度(高速,快速/快速Plus,标准模式速度),因为超快模式遵循更高的传输速率(高达5Mb/s),只有写传输,没有从机的确认。

2.2术语

2.2.1 总线术语

发送器 Transmitter、接收器 Reveiver、主机 Master、从机 Slave;

多主机Multi-master: 多个主机同时在总线上共存而不会发生碰撞或数据丢失的能力;

仲裁 Arbitration:预定义的过程,一次只授权一个主机控制总线;

SDA SCL

2.2.2总线传输术语

START(RESTART):总线忙碌的开始条件--SDA从高变低,同时SCL保持高电平。表征START 数据开始传输。 如下图红框S

STOP: SDA从低变高,同时SCL保持高,此时总线转为空闲;如是RESTART,总线继续保持忙碌

2.3 I2C行为

Master通信时,发送 START/RESTART+Slave Address+R/W(表示读还是写操作);之后Slave在地址后发送ACK脉冲;

2.3.2组合格式

只支持同一地址格式的组合事务,比如两组数据都是7bit地址格式,或都是10bit地址格式,可以组合处理;但不支持7bit地址后跟数据+10bit地址后跟数据的格式。

2.4 I2C协议

2.4.1 START STOP条件

当总线空闲时,SCL和SDA信号都通过总线上的外部上拉电阻被拉高。当MASTER想要在总线上启动传输时,MASTER发出一个start条件。定义为SCL为1时,SDA信号从高到低的转换。当MASTER想要终止传输时,MASTER发出一个STOP条件,这被定义为SDA线从低到高的转变,而SCL为1。

2.4.2 寻址从协议

2.4.2.1 7-bit地址格式

START->7bit Address->R/W->ACK

2.4.2.1 10-bit地址格式

START->7bit Address->R/W->ACK

在10位寻址过程中,传递两个字节来设置10位地址。第一个字节的传输包含以下位定义。前五个比特(比特7:3)通知从机这是一个10位的传输,接下来的两个比特(比特2:1)将从机地址设置为9:8,LSB比特(比特0)描述R / W。传输的第二个字节设置从地址的位7:0。10位地址格式如图2-6所示。

2.4.3发送和接收协议

主发送,从接收时,数据的字节数不限制,但每个字节后从机必须响应ACK,不响应时主机必须STOP,从机离开SDA;

主收从发时,由主机发送ACK,没有时即NACK使从机退出SDA,主机发出STOP;主机若不想STOP,就在ACK之后发送RESTART;

2.4.4起始字节传输协议

起始字节传输协议是为没有板载专用I2C硬件模块的系统设置的。当DW_apb_i2c作为从设备寻址时,它总是以支持的最高速度对I2C总线进行采样,因此它不需要START BYTE传输。但是,当DW_apb_i2c是主设备时,它支持在每次传输开始时生成START BYTE传输,以防从设备需要它。该协议由7个0加1组成,如下图所示。允许正在轮询总线的处理器对地址阶段进行欠采样,直到检测到0。一旦微控制器检测到0,它就从欠采样率切换到主机的正确速率。

START BYTE过程如下:

1.Master生成START条件。

2.Master发送START字节(0000 0001)。

3.Master发送ACK时钟脉冲。(仅为符合总线上使用的字节处理格式而出现)。

4.No slave将ACK信号设置为0。

5. Master生成一个RESTART (R)条件。

硬件接收器不响应START字节,因为它是一个保留地址,在RESTART条件生成后重置。

2.5 TX FIFO管理和START/STOP/RESTART产生

当作为主机运行时,DW_apb_i2c器件支持两种模式的TX FIFO管理。

可以使用IC_EMPTYFIFO_HOLD_MASTER_EN参数在这两种模式中选择:

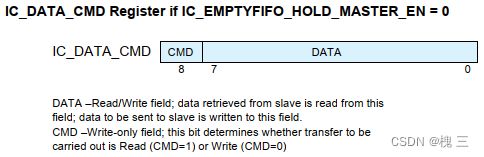

IC_EMPTYFIFO_HOLD_MASTER_EN=0,1

DATA和CMD同上,增加了STOP和RESTART:

STOP:只写有效,此bit决定数据字节在被发送或接收后是否产生STOP;

RESTART:只写有效此bit决定在数据字节被发送或接收之前是否产生RESTART;如果RESTART没被使能,则此bit代表的是STOP后跟一个START指令。

2.5.1 IC_EMPTYFIFO_HOLD_MASTER_EN=0时的Tx FIFO管理

=0时,每当TX FIFO变空时器件会产生一个STOP。如果使能RESTART,则会在TX FIFO指令从读变为写或者从写变为读时产生RESTART;如果RESTART没被使能则在STOP后会跟一个START指令。

DATA:【7:0】存贮读从slave发送的数据 和 写进slave的数据

CMD: 只写有效;1表征读,0表征写。

2.5.2 IC_EMPTYFIFO_HOLD_MASTER_EN=1时的Tx FIFO管理

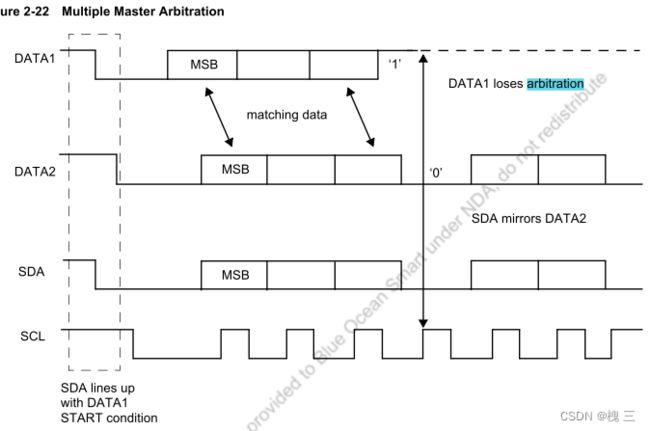

2.6多主机仲裁

DW_apb 2c总线协议允许多个主机驻留在同一总线上。如果同一总线上有两个主机,如果两者都试图通过同时生成START条件来控制总线,则存在仲裁过程。一旦其中一个主机控制了总线,在该主机发送停止条件并将总线置于空闲状态之前,其他主机都不能控制总线。仲裁发生在SDA线上(SCL保持1)。当主机A发送1,而主机B发送0,则A失去仲裁并关闭其数据输出阶段。失去仲裁的主机可以继续生成时钟,直到字节传输结束。如果两个主设备都寻址同一个从设备,仲裁可以进入数据阶段。如下图: 简言之:多主争夺总线时会出现仲裁,两主PK SDA,当出现一个发1另一个发0时,发1的退出;之前一样的SDA保留在总线上且已经被传输。 就和剪刀石头布一样。。。。

MARK:I2C的仲裁机制并不只有多主抢夺总线控制权这一种,还有MASTER/SLAVE丢失仲裁的情况,待学习吸收后另起篇幅归总。