Synopsys DW_apb_i2c的IIC协议解读

I2C总线是一个双线串行接口,由串行数据线(SDA)和串行时钟(SCL)组成。这些线在连接到总线的设备之间传输信息。每个设备都由一个唯一的地址识别,根据设备的功能,可以作为“发射机”或“接收机”运行。在执行数据传输时,设备也可以被视为主设备或从设备。主设备是一种在总线上启动数据传输并生成时钟信号以允许该传输的设备。在那个时候,任何被寻址的设备都被认为是从设备。

DW_apb_i2c模块可以在标准模式(数据速率为0至100 Kb/s)、快速模式(数据率小于或等于400 Kb/s),快速模式+(数据速率小于或等于1000 Kb/s)和高速模式(数据速度小于或等于3.4 Mb/s)以及超高速模式(数据速率小于或大于5 Mb/s)下运行。

DW_apb_i2c只能与这些连接到总线的设备通信。

此外,高速模式和快速模式设备向下兼容。例如,高速模式设备可以与混合速度总线系统中的快速模式和标准模式设备进行通信;

快速模式设备可以在0到100Kb/s I2C总线系统中与标准模式设备通信。但是:

1.标准模式设备不向上兼容,不应包含在快速模式I2C总线系统中,因为它们不能遵循更高的传输速率,并且会出现不可预测的状态。

2.超快模式设备不向下兼容,不应包含在传统的I2C速度(高速、快速/快速模式+速度、标准模式速度)中,因为超快模式遵循更高的传输速率(高达5Mb/s),只有写入传输,并且没有来自从机的确认。

高速模式设备的一个例子是LCD显示器、高位计数ADC和高容量EEPROM。这些设备通常需要传输大量数据。大多数维护和控制应用,即I²C总线的常见用途,通常在100 kHz下运行(在标准和快速模式下)。

超快速度模式设备的一个例子是LED控制器和其他不需要反馈的设备。这些设备通常需要传输大于1Mhz的大量数据。

任何DW_apb_i2c设备都可以连接到I²C总线,每个设备都可以与任何主设备通信,来回传递信息。总线上需要至少有一个主控器(如微控制器或DSP),但可以有多个主控,这需要它们仲裁所有权。本章后面将解释多主机和仲裁。

DW_apb_i2c还支持用于系统管理和电源管理的SMBus和PMBus协议。

DW_apb_i2c由AMBA apb从接口、i2c接口和FIFO逻辑组成,以保持两个接口之间的一致性。该组件的简化框图如图3-1所示。

I2C术语

以下术语贯穿本手册,定义如下:

以下术语涉及I2C设备的作用以及它如何与总线上的其他I2C设备交互。

Transmitter ——向总线发送数据的设备。发送器可以是启动到总线的数据传输的设备(主发送器),也可以响应来自主发送器的向总线发送数据的请求(从发送器)。

■ Receiver –从总线接收数据的设备。接收器可以是根据其自身请求(主接收器)或响应于来自主接收器的请求(从接收器)来接收数据的设备。

■ Master -初始化传输(START命令)、生成时钟(SCL)信号并终止传输(STOP命令)的组件。主机可以是发射机,也可以是接收机。

■ Slave –由主设备寻址的设备。从设备可以是接收机,也可以是发射机。

这些概念如图3-2所示。

■ Multi-master-多个主机同时在总线上共存而不会发生冲突或数据丢失的能力。

■ Arbitration - 一次只授权一个主机控制总线的预定义程序。有关这种行为的更多信息,请参阅第55页的“多重主仲裁”。

■ Synchronization –对两个或多个主控器提供的时钟信号进行同步的预定义过程。有关此功能的更多信息,请参阅第57页的“时钟同步”。

■ SDA–数据信号线(串行data)

■ SCL–时钟信号线(串行时钟锁定)

总线传输过程

以下术语专用于发生在I2C总线之间的数据传输。

■ START(RESTART)–数据传输以START或RESTART条件开始。SDA数据线的电平从高变为低,而SCL时钟线保持高。当这种情况发生时,总线变得繁忙。

■ STOP–数据传输因STOP条件而终止。当SDA数据线上的电平从低状态转变为高状态,而SCL时钟线保持高电平时,就会发生这种情况。当数据传输终止时,总线再次空闲。如果生成RESTART而不是STOP条件,则总线将保持繁忙状态。

I2C行为

DW_apb_i2c可以通过软件控制为:

■ 仅I2C主机,与其他I2C从机通信;或者

■ 仅I2C从机,与一个以上I2C主机通信。

主机负责生成时钟并控制数据传输。从设备负责向主设备发送数据或从主设备接收数据。数据确认由接收数据的设备发送,该设备可以是主设备,也可以是从设备。如前所述,I2C协议还允许多个主机驻留在I2C总线上,并使用仲裁程序来确定总线所有权。

每个从设备都有一个由系统设计者确定的唯一地址。当主设备想要与从设备通信时,主设备发送START/RESTART条件,该条件之后是从设备的地址和控制位(R/W),以确定主设备想要发送数据还是从从设备接收数据。然后,从设备在地址之后发送一个确认(ACK)脉冲。

如果主设备(主发送器)正在向从设备(从接收器)写入,则接收器将获得一个字节的数据。

此事务一直持续到主机以STOP条件终止传输为止。如果主设备正在从设备(主接收器)读取数据,则从设备向主设备发送(从发送器)一个字节的数据,然后主设备用ACK脉冲确认事务。该事务继续进行,直到主设备在接收到最后一个字节后通过不确认(NACK)事务来终止传输,然后主设备发出STOP条件或在发出RESTART条件后寻址另一个从设备。这种行为如图3-3所示。

在超快模式下,主设备只能向从设备发出写入传输,而从设备始终不确认(NACK)。在此模式下不允许读取传输。

DW_apb_i2c是一个同步串行接口。SDA线是双向信号,仅在SCL线为低电平时发生变化,STOP、START和RESTART条件除外。输出驱动器是开路漏极或开路集电极,用于在总线上执行导线AND功能。总线上设备的最大数量仅受最大电容规格400 pF的限制。数据以字节封装传输。

START and STOP 信号生成

当作为i2c主机操作时,将数据放入发送FIFO会导致DW_apb_i2c在i2c总线上生成START条件。如果IC_EMPTYFFO_HOLD_MASTER_EN参数设置为0,则允许传输FIFO清空会导致DW_apb_i2c在i2c总线上生成STOP条件。如果IC_EMPTYFFO_HOLD_MASTER_EN设置为1,则将1写入IC_DATA_CMD[9]会导致DW_apb_i2c在i2c总线上生成STOP条件;如果该位未被设置,即使发送FIFO为空,也不会发出STOP条件。

当作为从设备运行时,DW_apb_i2c不会根据协议生成START和STOP条件。然而,如果向DW_apb_i2c发出读取请求,它将SCL线保持为低电平,直到向其提供了读取数据。这将暂停i2c总线,直到向从属DW_apb_id2c提供读取数据,或者通过向IC_ENABLE寄存器的位0写入0来禁用DW_apb_i2c从属。

组合格式

DW_apb_i2c支持7位和10位寻址模式下的混合读写组合格式事务。

DW_apb_i2c不支持混合地址和混合地址格式,即7位地址事务后接10位地址事务,反之亦然。

要启动组合格式传输,应将IC_CON.IC_RESTART_EN设置为1。通过设置该值并作为主设备操作,当DW_apb_i2c完成i2c传输时,它检查传输FIFO并执行下一次传输。如果此转移的方向与上一次转移不同,则使用组合格式发出转移。如果当前I2C传输完成时传输FIFO为空,取决于IC_EMPTYFIFO_HOLD_MASTER_EN的值:

■ 要么发出STOP,

■ 要么检查IC_DATA_CMD[9]:

❑ 如果设置为1,则发出STOP位。

❑ 如果设置为0,SCL保持为低电平,直到下一个命令被写入传输FIFO。

I2C 协议

START and STOP条件

当总线空闲时,SCL和SDA信号都通过总线上的外部上拉电阻器拉高。当主机想要启动总线上的传输时,主机会发出start(启动)条件。

这被定义为当SCL为1时SDA信号的高到低转变。当主机想要终止传输时,主机发出STOP(停止)条件。这被定义为当SCL为1时SDA线的低到高转变。图3-4显示了启动和停止条件的时间安排。

当数据在总线上传输时,当SCL为1时,SDA线路必须稳定。

启动/停止条件下的信号转换,如图3-4所示,反映了在驱动I2C总线的主设备输出信号处观察到的信号转换。在从设备的输入信号处观察SDA/SCL信号时应小心,因为不相等的线路延迟可能导致不正确的SDA/SCL-时序关系。

启动/停止条件下的信号转换,如图3-4所示,反映了在驱动I2C总线的主设备输出信号处观察到的信号转换。在从设备的输入信号处观察SDA/SCL信号时应小心,因为不相等的线路延迟可能导致不正确的SDA/SCL-时序关系。

寻址从协议

有两种地址格式:7位地址格式和10位地址格式。

7位地址格式

在7位地址格式中,第一个字节的前七位(位7:1)设置从地址,LSB位(位0)为R/W位,如图3-5所示。当位0(R/W)被设置为0时,主设备向从设备写入。当位0(R/W)被设置为1时,主设备从从设备读取。

10位地址格式

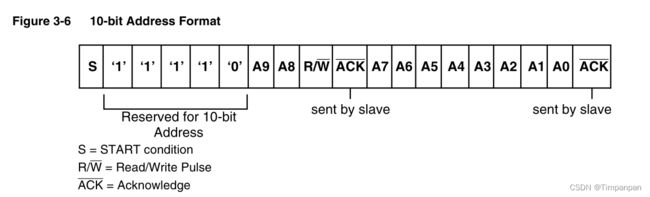

在10位寻址期间,传输两个字节以设置10位地址。第一个字节的传输包含以下位定义。前五个比特(比特7:3)通知从设备这是10比特的传输,随后是设置从设备地址比特9:8的下两个比特(bit 2:1),并且LSB比特(bit 0)是R/W比特。所传输的第二个字节设置从地址的位7:0。图3-6显示了10位地址格式。

表3-1 I2C/SMBus第一字节中位的定义

表3-1 I2C/SMBus第一字节中位的定义

DW_apb_i2c不会限制您使用这些保留地址。但是,如果您使用这些保留地址,您可能会遇到与其他I2C组件不兼容的问题。

DW_apb_i2c不会限制您使用这些保留地址。但是,如果您使用这些保留地址,您可能会遇到与其他I2C组件不兼容的问题。

发送和接收协议

主机可以启动到总线的数据传输和从总线的数据接收,充当主机发送器或主机接收器。从机响应来自主机的请求,向总线发送数据或从总线接收数据,分别充当从机发送器或从机接收器。

主机发送和从机接收

所有数据都以字节格式传输,每次数据传输的字节数没有限制。

在主设备发送地址和R/W位或主设备向从设备发送一字节数据后,从设备接收器必须用确认信号(ACK)进行响应。当从接收器没有响应ACK脉冲时,主接收器通过发出STOP条件中止传输。从设备必须使SDA线路保持高电平,以便主设备可以中止传输。

如果主发射机正在传输数据,如图3-7所示,则在接收到每个字节的数据后,从接收机用确认脉冲响应主发射机。

在超快模式下,从接收器总是用来自主接收器的地址和写入数据的无确认信号(NACK)进行响应。

主机接收和从机发送

如果主设备正在接收如图3-8所示的数据,则在接收到一个字节的数据(最后一个字节除外)后,主设备用确认脉冲对从发射机作出响应。这是主接收器通知从发送器这是最后一个字节的方式。在检测到无确认(NACK)后,从发射机放弃SDA线路,以便主发射机可以发出STOP条件。

当主设备不想在STOP条件下放弃总线时,主设备可以发出RESTART条件。这与START条件相同,只是发生在ACK脉冲之后。在主模式下操作,DW_apb_i2c可以使用不同方向的传输与同一从设备通信。

有关DW_apb_i2c支持的组合格式事务的说明,请参阅第45页的“组合格式”。

如果i2c_DYNAMIC_TAR_UPDATE=0,则必须完全禁用DW_apb_i2c;如果i2c_DYNAMIC_TAR_UPDA=1,则必须禁用串行端口上的DW_apb_id2c,然后才能重新编程目标从属地址寄存器(IC_TAR)。

在超快模式下,主接收器和从发送器不适用,因为不支持读取传输。

start byte传输协议

START BYTE传输协议是为没有板载专用I2C硬件模块的系统设置的。当DW_apb_i2c被寻址为从机时,它总是以支持的最高速度对i2c总线进行采样,因此它从不需要START BYTE传输。但是,当DW_apb_i2c是主设备时,它支持在每次传输开始时生成START BYTE传输,以备从设备需要。

如图3-9所示,该协议由传输的七个零和一个1组成。这允许轮询总线的处理器对地址相位进行欠采样,直到检测到0为止。一旦微控制器检测到0,它就从欠采样率切换到主控制器的正确速率。

START BYTE(旁通起动)程序如下:

1.Master生成START条件。

2.主机发送START字节(0000 0001)。

3.主设备发送ACK时钟脉冲。(仅用于符合总线上使用的字节处理格式)

4.没有从设备将ACK信号设置为0。

5.Master生成RESTART(R)条件。

硬件接收器不响应START BYTE,因为它是一个保留地址,并在生成RESTART条件后重置。