- 【从零开始学习计算机科学】计算机体系结构(一)计算机体系结构、指令、指令集(ISA)与量化评估

贫苦游商

学习服务器网络计算机体系结构ISA指令集量化评估

【从零开始学习计算机科学】计算机体系结构(一)计算机体系结构、指令、指令集(ISA)与量化评估概论计算机体系结构简介计算机的分类并行体系结构指令集体系结构(ISA)分类存储器寻址寻址模式操作数大小指令ISA的编码程序的优化计算机体系结构量化评估存储器体系结构概论计算机体系结构与计算机组成原理之间的联系非常紧密,其研究范畴基本一致,计算机体系结构与计算机组成原理两者是相辅相成的。但是,计算机体系结构

- Java复习路线

Code good g

面试准备javamysql数据库

Java复习1、Java基础2、Java多线程3、Javaweb的复习4、MySql复习数据库常用的代码:思维导图:5、计算机组成原理6、网络编程7、Java注解和反射8、计算机网络9、html/css/js10、ssm11、spring12、springmvc13、springboot14、vue15、springcloud16、jvm17、Juc18、mybatis-plus学习19、git2

- 探索 ESP32:物联网时代的全能微控制器

菜只因C

物联网

引言:从ESP8266到ESP32的进化之路在物联网(IoT)蓬勃发展的今天,嵌入式设备需要兼具高性能、低功耗和联网能力。乐鑫科技(RobinLi)推出的ESP32系列芯片,正是这一需求下的产物。自2016年发布以来,ESP32凭借其卓越的综合性能,迅速成为物联网开发者的首选平台。本文将从硬件架构、核心功能、开发生态到实际应用,全面解析这款"物联网心脏"的奥秘。一、ESP32的硬件架构解析1.1双

- 2023计算机组成原理考研知识点:哈佛结构

计算机考研

考研资料计算机网络哈佛结构数据结构

2023年计算机考研初试科目一般分四门,基本都考政治、英语一、数学一和计算机基础(计算机综合),报考院校不同专业课考试内容一般不同,建议考生下正式备考2023年研考时先确认报考院校计算机研招科目内容,避免无效备考。计算机组成原理:哈佛结构将指令和数据放在两个独立的存储器,允许在一个机器周期内同时获得指令和操作数,提高了执行速度。2023年计算机组成原理复习题示例(来源于网络,如有侵权,请联系删除)

- 一文读懂stm32和51单片机的区别

对error说不

stm3251单片机嵌入式硬件

一、引言在嵌入式系统开发领域,STM32和51单片机是两款被广泛使用的微控制器。51单片机以其简单易学、成本低廉的特点,在早期的电子开发中占据了主导地位;而STM32作为后起之秀,凭借其高性能、丰富的外设和强大的处理能力,逐渐成为了中高端应用的首选。本文将从多个方面详细阐述STM32和51单片机的区别,并给出相应的代码示例进行对比。二、硬件架构2.1内核51单片机:采用8位的8051内核,数据处理

- 嵌入式硬件篇---龙芯UART通信

Ronin-Lotus

嵌入式硬件篇上位机知识篇程序代码篇嵌入式硬件cUART龙芯2k1000pwm

文章目录前言一、代码结构解析1.头文件部分作用2.宏定义与全局变量龙芯特性3.主函数流程关键点4.UART发送函数龙芯实现5.串口配置函数(set_port)龙芯注意事项6.GPIO控制函数龙芯GPIO特性7.PWM控制函数龙芯PWM实现二、龙芯UART深度解析1.硬件架构控制器类型时钟源寄存器映射2.关键寄存器3.驱动配置内核配置设备树配置4.波特率计算公式示例三、代码优化建议错误处理增强非阻塞

- 河南大学计算机组成原理实验报告1

凡巾

计算机组成原理teambition

Ⅰ、单片机键盘操作方式实验注:在进行单片机键盘控制实验时,必须把开关K4置于“OFF”状态,否则系统处于自锁状态,无法进行实验。1、实验连线(键盘实验):实验连线如图1-1所示。(连线时应按如下方法:对于横排座,应使排线插头上的箭头面向自己插在横排座上;对于竖排座,应使排线插头上的箭头面向左边插在竖排座上。注意:F4只用一个排线插头孔)图1-1实验一键盘实验连线图2、实验过程:注意:操作过程中,可

- 计算机组成原理(知识点+易错点,超详细)|第四章 指令系统

sailing_c

计算机组成原理计算机组成原理学习笔记

目录4.1指令系统4.1.1指令集体系结构4.1.2指令的基本格式4.1.3定长操作码指令格式4.1.4扩展操作码指令格式4.1.5指令的操作类型4.2指令的寻址方式4.2.1指令寻址和数据寻址4.2.2常见的数据寻址方式4.3程序的机器级代码表示4.3.1常用汇编指令介绍4.3.2选择语句的机器级表示4.3.3循环语句的机器级表示4.3.4过程调用的机器级表示4.4CISC和RISC的基本概念4

- Ubuntu常用命令

欲登绝巘

ubuntulinux运维

以下是一些常用的Ubuntu命令,可以帮助您在终端中进行各种任务和操作:文件和目录操作:ls:列出当前目录下的文件和目录。cd:切换目录。pwd:显示当前工作目录的路径。mkdir:创建新目录。rm:删除文件或目录。cp:复制文件和目录。mv:移动文件和目录。系统信息和管理:uname-a:显示系统信息,包括内核版本和硬件架构。top:实时显示系统资源使用情况和运行进程。free:显示内存使用情况

- 计算机组成原理知识点精汇(一)计算机基础知识

A.sir啊

计算机组成原理计算机组成原理冯诺依曼硬件架构CPU

一、冯·诺伊曼计算机的特点(1)计算机由运算器、控制器、存储器、输人设备和输出设备五大部件组成。(2)程序和数据存放在同一存储器中,并按地址寻访。(3)指令和数据均采用二进制运算。(4)指令由操作码和地址码组成,操作码用来表示操作的类型,地址码用来表示操作数和操作结果的地址。(5)机器以运算器为核心,输人输出设备与存储器之间的数据传送都要通过运算器。二、机器字长CPU一次操作中能够处理的数据的位数

- 计算机组成原理与系统结构 知识点总结-简答题3【中央处理器+Flynn分类法+指令级并行+线程级并行-多处理机】

Geometry Fu

计算机组成原理与系统结构算法

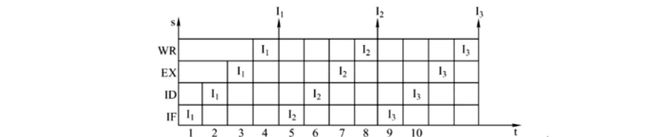

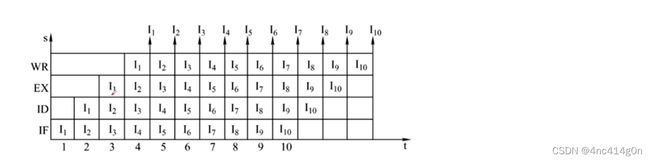

中央处理器42.流水线中有哪三种冒险?请简述,并至少举出一种解决冒险的方法。结构冒险:需要的资源被占用(硬件资源冲突)。将指令和数据分别存储;设计指令/数据高速缓存。数据冒险:需要等待前面指令完成其读写操作。转发(旁路);代码重排;阻塞和冒泡。控制冒险:根据前面正在执行的指令决策控制操作。静态分支预测;动态分支预测;分支延迟。Flynn分类法43.请简述Flynn分类法将计算机系统结构分成哪四类。

- 专业 英语

程序员爱德华

英语专业英语

文章目录一、计算机1.计算机基础(1)计算机组成原理(2)计算机网络(3)数据库(4)编译原理(5)离散数学2.软件开发(1)编程词汇(2)开发术语(3)Linux(4)软件3.就业领域(1)职场(2)芯片(3)自动驾驶(4)嵌入式硬件4.深度学习(1)论文(2)深度学习DL(3)计算机视觉CV(4)自然语言处理NLP(5)推荐系统(6)计算机图形学二、数学三、机械、材料四、医药五、英美计量单位一

- Computer Systems A Programmer‘s Perspective 深入理解计算机系统 1

清水湾的水

linux

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档文章目录前言一、编译系统1.编译系统的流程二、硬件架构1.CPU2.内存3.总线4.输入输出设备三、解释内存中的指令1.程序执行的流程2.程序执行过程中发生了什么3.设备容量4.Cache5.存储设备的层次结构四、操作系统的作用1.操作系统的作用2.进程3.进程角度五、虚拟内存1.虚拟内存2.文件3.系统之间利用网络通信六、系统加速1

- 深入解析:FIR滤波器在FPGA上的设计与实现全流程

king-agic

FPGAfpga开发经验分享

在FPGA中实现FIR(FiniteImpulseResponse)滤波器涉及多个步骤,包括滤波器设计、系数量化、硬件架构设计、HDL(HardwareDescriptionLanguage)编码、综合、布局布线以及验证。1.滤波器设计使用软件工具如MATLAB、Octave或者Python中的SciPy库来设计FIR滤波器。定义滤波器的规格,例如采样频率、截止频率、通带和阻带衰减等。生成滤波器的

- 计算机组成原理----计算机系统概述

王嘉俊925

计算机组成原理计组计算机组成原理

计算机分类按照输入输出信号的形式可以将电子计算机分为:电子模拟计算机和电子数字计算机。电子模拟计算机定义:采用连续的模拟信号(如电压、电流)进行输入和输出,模拟物理量之间的关系。特点:计算过程基于模拟电路,反映连续变化的物理现象。擅长处理微分方程、动态系统仿真。应用:早期用于科学计算(如飞行模拟、天气预报)和工程设计。局限:精度较低,难以编程和扩展。电子数字计算机定义:使用离散的数字信号(通常为二

- “计算机组成原理-电子科技大学-学堂在线”———课堂笔记——第一章计算机系统概述

日熙!

#学校学习笔记计算机组成原理

第一章计算机系统概述1.1计算机的概念和类型1>计算机的基本概念2>计算机的主要特点3>计算机的常见类型1.2计算机的诞生与发展1.3计算机系统的层次结构1.4计算机的性能评价指标1.1计算机的概念和类型1>计算机的基本概念什么是电子计算机?——————存储程序,执行程序,对数字信息进行各种复杂处理,输出运算结果的智能电子设备一个计算机系统主要包括以下5个逻辑模块:输入设备,存储器,输出设备,运算

- 深度学习批次数据处理的理解

_DCG_

计算机视觉深度学习人工智能

基础介绍在计算机视觉深度学习网络中,在训练阶段数据输入通常是一个批次,即不是一次输入单张图片,而是一次性输入多张图片,而神经网络的结构内部一次只能处理一张图片,这时候很自然就会考虑为什么要这样的输入?神经网络是如何处理多个数据的,下面从硬件架构的角度去分析处理。GPU硬件架构GPU的硬件架构设计是批处理能够高效运行的关键原因之一。GPU现阶段一般采用SIMT架构,它的特点如下:SIMT(Singl

- 23西安电子科技大学 西电 833计算机专业基础综合 834 数据结构 计算机组成原理 考研参考书及学长学姐全程复习经验分享

西电研梦

考研数据结构经验分享

23西安电子科技大学西电833计算机专业基础综合834数据结构计算机组成原理考研参考书及学长学姐全程复习经验分享我觉得考研本身并不算难,难得在于给自己一个可以一直坚持下去的动力,所以第一个问题是我们要清楚为什么要考研?我并不能直接告诉你考研好还是工作好?但所有考研的人都需要把信息进行收集:1.你希望考的那个专业前景怎么样?2.各个学校的这个专业怎么样,业内是否认可,能给你提供什么资源?3.各个学校

- 华为出品Python入门教程:从零基础入门到精通,这一篇就够了

学Python的AA

python数据科学python开发语言

前言本文罗列了了python零基础入门到精通的详细教程,内容均以知识目录的形式展开。01.python由来与发展介绍02.项目开发流程第一章markdown编辑器01.markdown基本语法02.Typora简介与安装03.Windows上gitee+Typora设置图床04.macOS上gitee+Typora设置图床第二章计算机核心基础01.计算机组成原理第三章编程语言01.编程语言介绍02

- Linux操作系统:基于Linux的智能安防系统

暮雨哀尘

Linux的那点事linux运维服务器大数据集群技术

基于Linux的智能安防系统开发文档1.项目概述本项目旨在开发一个基于Linux的智能安防系统,集成火灾报警、门禁控制和传感器数据采集功能。系统通过多种传感器实时监测环境状态,并在检测到异常时触发报警,同时将数据上传至云平台供远程监控。该系统适用于家庭、办公室、仓库等场景,能够有效提升安全性和管理效率。2.系统架构系统的整体架构分为硬件部分和软件部分,具体如下:2.1硬件架构核心控制器:树莓派(推

- OceanBase 初探学习历程之——安装部署

羽书飞影

oceanbase学习

一、介绍OceanBase数据库是一个原生的分布式关系数据库,它是完全由阿里巴巴和蚂蚁集团自主研发的项目。OceanBase数据库构建在通用服务器集群上,基于Paxos协议和分布式架构,提供金融级高可用和线性伸缩能力,不依赖特定硬件架构,具备高可用、线性扩展、高性能、低成本等核心技术优势。OceanBase数据库具有如下特点:高可用单服务器故障能够自愈,支持跨城多机房容灾,数据零丢失,可满足金融行

- **ARM Cortex-M4** 和 **ARM Cortex-M7* 运行freeRTOS

BlueBirdssh

arm开发

**是的,Cortex-M4和Cortex-M7都可以运行FreeRTOS**。FreeRTOS是一个轻量级的实时操作系统(RTOS),专为嵌入式系统设计,支持多种硬件架构,包括ARMCortex-M系列(如Cortex-M0、M3、M4、M7等)。由于FreeRTOS的设计灵活且硬件需求较低,Cortex-M4和Cortex-M7都能很好地运行FreeRTOS。以下是关于FreeRTOS在Cor

- 开发一个音响控制板程序,需要从硬件架构设计、通信协议选择、核心功能实现三个层面进行系统化开发。以下是基于工业级开发流程的实施方案

星糖曙光

后端语言(nodejavascriptvue等等)stm32emacsAI编程设计规范课程设计

一、硬件架构设计阶段主控芯片选型推荐采用STM32F4系列(如STM32F407VGT6),其168MHz主频和硬件浮点单元可满足实时音频处理需求[7]外围电路需集成PT2313音频处理芯片,实现4通道输入选择、音量/音调调节功能[13]存储系统采用W25Q128闪存保存用户配置参数,预留SDIO接口支持扩展存储信号处理架构cc//典型信号链路配置voidAudioPath_Init(void){

- 如何学习ARM嵌入式系统的设计

AAAA%

学习嵌入式硬件单片机

学习ARM嵌入式系统设计是一个系统性的过程,需要理论知识与实践技能相结合。以下是一份详细的学习路径指南,帮助你逐步掌握ARM嵌入式系统的设计:1.基础知识储备了解计算机体系结构:学习计算机组成原理,了解CPU、内存、IO等基本概念。学习C语言编程:C语言是嵌入式系统开发的主流语言,需要熟练掌握。理解操作系统原理:虽然嵌入式系统可能不总是运行完整的操作系统,但了解操作系统的基本概念对于理解系统设计至

- 大规模GPU集群的进阶之路

卢旗

人工智能

大家好,我是卢旗。今天来聊聊GPU。GPU,全称GraphicProcessingUnit,即图形处理器。它的并行处理能力非常强大,能够同时处理多个任务和数据,因此被广泛用于图形渲染、视频处理、深度学习、科学计算等领域。研发团队在负责制定硬件选型策略并设计优化下一代大规模GPU集群的软硬件架构时,我们需要关注GPU技术的最新进展、重点研究问题以及潜在的技术突破。一、GPU在重点研究的问题算力提升与

- 【linux numa】 NUMA 绑核

Dayu_log

linuxlinux

1.NUMA的前世今生NUMA(NonUniformMemoryAccess)和UMA(UniformMemoryAccess)是两种CPU相关的硬件架构。在早期的UMA架构中,CPU通过前端总线(FSB,FrontSideBus)连接到北桥芯片,然后北桥芯片连接到内存,即内存控制器集成在北桥芯片中。外部IO设备与南桥芯片相连,南桥芯片与北桥芯片通过内部总线相连。下图为UMA架构图下图为早期的UM

- 《探秘AI绿色计算:降低人工智能硬件能耗的热点技术》

程序猿阿伟

人工智能

在人工智能飞速发展的当下,其硬件能耗问题愈发凸显。据国际能源署预测,人工智能的能源消耗可能大幅增长。因此,降低人工智能硬件能耗,实现绿色计算,已成为行业关键课题。以下是一些正在崭露头角的热点技术。新型硬件架构与材料计算随机存取内存(CRAM):明尼苏达大学的研究团队开发的CRAM,能让数据完全在内存阵列内处理,无需离开计算机存储信息的网格,打破了传统冯·诺依曼体系结构中计算与内存之间的壁垒,可将人

- 嵌入式工程师全攻略:岗位职责与技能要求详解

Nebula嵌入式

嵌入式科普嵌入式

文章目录一、前言二、**硬件架构中最常用的有哪几种**三、嵌入式的岗位及技能要求3.1嵌入式硬件3.1.1主要职责3.1.2技能要求3.1.3学习建议3.2嵌入式单片机3.2.1主要职责3.2.2技能要求3.2.3学习建议3.3嵌入式linux3.3.1主要职责3.3.2技能要求3.3.3学习建议一、前言这是根据我个人和网上的一些资料编写的,可能有不对的地方请及时提醒。二、硬件架构中最常用的有哪几

- 计算机组成原理——总线系统

汐颜花

零知识证明

总线大致分为三类:CPU内部连接各寄存器及运算部件之间的总线,称为内部总线。CPU同计算机系统的其他高速功能部件,如储存器、通道等互相连接的总线,称为系统总线。中、低速I/O设备之间互相连接的总线,称为I/O总线。总线的特性物理特性:总线的物理特性是指总线的物理连接方式,包括总线的根数,总线的插头、插座的形状,引脚线的排列方式等。功能特性:功能特性描述总线中每一根线的功能。如地址总线的宽度指明了总

- 【计算机组成原理】1_绪论

BroccoliKing

计组网络硬件架构fpga开发arm开发iotmcu

chap1绪论1.国产芯片现状MIPS阵营:龙芯X86阵营(常见于桌面和服务器):兆芯(VIA),海光(AMD)ARM阵营(常见于移动嵌入式、手机平板等):飞腾,海思,展讯,松果RISC-V阵营:阿里平头哥玄铁9102.冯·诺伊曼结构计算机2.1组成硬件系统:运行程序的基本组成部分运算器控制器:控制信号的产生方式包括微程序和硬布线存储器输入输出设备软件系统:系统软件和应用软件2.2层次结构3.指令

- PHP,安卓,UI,java,linux视频教程合集

cocos2d-x小菜

javaUIPHPandroidlinux

╔-----------------------------------╗┆

- 各表中的列名必须唯一。在表 'dbo.XXX' 中多次指定了列名 'XXX'。

bozch

.net.net mvc

在.net mvc5中,在执行某一操作的时候,出现了如下错误:

各表中的列名必须唯一。在表 'dbo.XXX' 中多次指定了列名 'XXX'。

经查询当前的操作与错误内容无关,经过对错误信息的排查发现,事故出现在数据库迁移上。

回想过去: 在迁移之前已经对数据库进行了添加字段操作,再次进行迁移插入XXX字段的时候,就会提示如上错误。

&

- Java 对象大小的计算

e200702084

java

Java对象的大小

如何计算一个对象的大小呢?

- Mybatis Spring

171815164

mybatis

ApplicationContext ac = new ClassPathXmlApplicationContext("applicationContext.xml");

CustomerService userService = (CustomerService) ac.getBean("customerService");

Customer cust

- JVM 不稳定参数

g21121

jvm

-XX 参数被称为不稳定参数,之所以这么叫是因为此类参数的设置很容易引起JVM 性能上的差异,使JVM 存在极大的不稳定性。当然这是在非合理设置的前提下,如果此类参数设置合理讲大大提高JVM 的性能及稳定性。 可以说“不稳定参数”

- 用户自动登录网站

永夜-极光

用户

1.目标:实现用户登录后,再次登录就自动登录,无需用户名和密码

2.思路:将用户的信息保存为cookie

每次用户访问网站,通过filter拦截所有请求,在filter中读取所有的cookie,如果找到了保存登录信息的cookie,那么在cookie中读取登录信息,然后直接

- centos7 安装后失去win7的引导记录

程序员是怎么炼成的

操作系统

1.使用root身份(必须)打开 /boot/grub2/grub.cfg 2.找到 ### BEGIN /etc/grub.d/30_os-prober ### 在后面添加 menuentry "Windows 7 (loader) (on /dev/sda1)" {

- Oracle 10g 官方中文安装帮助文档以及Oracle官方中文教程文档下载

aijuans

oracle

Oracle 10g 官方中文安装帮助文档下载:http://download.csdn.net/tag/Oracle%E4%B8%AD%E6%96%87API%EF%BC%8COracle%E4%B8%AD%E6%96%87%E6%96%87%E6%A1%A3%EF%BC%8Coracle%E5%AD%A6%E4%B9%A0%E6%96%87%E6%A1%A3 Oracle 10g 官方中文教程

- JavaEE开源快速开发平台G4Studio_V3.2发布了

無為子

AOPoraclemysqljavaeeG4Studio

我非常高兴地宣布,今天我们最新的JavaEE开源快速开发平台G4Studio_V3.2版本已经正式发布。大家可以通过如下地址下载。

访问G4Studio网站

http://www.g4it.org

G4Studio_V3.2版本变更日志

功能新增

(1).新增了系统右下角滑出提示窗口功能。

(2).新增了文件资源的Zip压缩和解压缩

- Oracle常用的单行函数应用技巧总结

百合不是茶

日期函数转换函数(核心)数字函数通用函数(核心)字符函数

单行函数; 字符函数,数字函数,日期函数,转换函数(核心),通用函数(核心)

一:字符函数:

.UPPER(字符串) 将字符串转为大写

.LOWER (字符串) 将字符串转为小写

.INITCAP(字符串) 将首字母大写

.LENGTH (字符串) 字符串的长度

.REPLACE(字符串,'A','_') 将字符串字符A转换成_

- Mockito异常测试实例

bijian1013

java单元测试mockito

Mockito异常测试实例:

package com.bijian.study;

import static org.mockito.Mockito.mock;

import static org.mockito.Mockito.when;

import org.junit.Assert;

import org.junit.Test;

import org.mockito.

- GA与量子恒道统计

Bill_chen

JavaScript浏览器百度Google防火墙

前一阵子,统计**网址时,Google Analytics(GA) 和量子恒道统计(也称量子统计),数据有较大的偏差,仔细找相关资料研究了下,总结如下:

为何GA和量子网站统计(量子统计前身为雅虎统计)结果不同?

首先:没有一种网站统计工具能保证百分之百的准确出现该问题可能有以下几个原因:(1)不同的统计分析系统的算法机制不同;(2)统计代码放置的位置和前后

- 【Linux命令三】Top命令

bit1129

linux命令

Linux的Top命令类似于Windows的任务管理器,可以查看当前系统的运行情况,包括CPU、内存的使用情况等。如下是一个Top命令的执行结果:

top - 21:22:04 up 1 day, 23:49, 1 user, load average: 1.10, 1.66, 1.99

Tasks: 202 total, 4 running, 198 sl

- spring四种依赖注入方式

白糖_

spring

平常的java开发中,程序员在某个类中需要依赖其它类的方法,则通常是new一个依赖类再调用类实例的方法,这种开发存在的问题是new的类实例不好统一管理,spring提出了依赖注入的思想,即依赖类不由程序员实例化,而是通过spring容器帮我们new指定实例并且将实例注入到需要该对象的类中。依赖注入的另一种说法是“控制反转”,通俗的理解是:平常我们new一个实例,这个实例的控制权是我

- angular.injector

boyitech

AngularJSAngularJS API

angular.injector

描述: 创建一个injector对象, 调用injector对象的方法可以获得angular的service, 或者用来做依赖注入. 使用方法: angular.injector(modules, [strictDi]) 参数详解: Param Type Details mod

- java-同步访问一个数组Integer[10],生产者不断地往数组放入整数1000,数组满时等待;消费者不断地将数组里面的数置零,数组空时等待

bylijinnan

Integer

public class PC {

/**

* 题目:生产者-消费者。

* 同步访问一个数组Integer[10],生产者不断地往数组放入整数1000,数组满时等待;消费者不断地将数组里面的数置零,数组空时等待。

*/

private static final Integer[] val=new Integer[10];

private static

- 使用Struts2.2.1配置

Chen.H

apachespringWebxmlstruts

Struts2.2.1 需要如下 jar包: commons-fileupload-1.2.1.jar commons-io-1.3.2.jar commons-logging-1.0.4.jar freemarker-2.3.16.jar javassist-3.7.ga.jar ognl-3.0.jar spring.jar

struts2-core-2.2.1.jar struts2-sp

- [职业与教育]青春之歌

comsci

教育

每个人都有自己的青春之歌............但是我要说的却不是青春...

大家如果在自己的职业生涯没有给自己以后创业留一点点机会,仅仅凭学历和人脉关系,是难以在竞争激烈的市场中生存下去的....

&nbs

- oracle连接(join)中使用using关键字

daizj

JOINoraclesqlusing

在oracle连接(join)中使用using关键字

34. View the Exhibit and examine the structure of the ORDERS and ORDER_ITEMS tables.

Evaluate the following SQL statement:

SELECT oi.order_id, product_id, order_date

FRO

- NIO示例

daysinsun

nio

NIO服务端代码:

public class NIOServer {

private Selector selector;

public void startServer(int port) throws IOException {

ServerSocketChannel serverChannel = ServerSocketChannel.open(

- C语言学习homework1

dcj3sjt126com

chomework

0、 课堂练习做完

1、使用sizeof计算出你所知道的所有的类型占用的空间。

int x;

sizeof(x);

sizeof(int);

# include <stdio.h>

int main(void)

{

int x1;

char x2;

double x3;

float x4;

printf(&quo

- select in order by , mysql排序

dcj3sjt126com

mysql

If i select like this:

SELECT id FROM users WHERE id IN(3,4,8,1);

This by default will select users in this order

1,3,4,8,

I would like to select them in the same order that i put IN() values so:

- 页面校验-新建项目

fanxiaolong

页面校验

$(document).ready(

function() {

var flag = true;

$('#changeform').submit(function() {

var projectScValNull = true;

var s ="";

var parent_id = $("#parent_id").v

- Ehcache(02)——ehcache.xml简介

234390216

ehcacheehcache.xml简介

ehcache.xml简介

ehcache.xml文件是用来定义Ehcache的配置信息的,更准确的来说它是定义CacheManager的配置信息的。根据之前我们在《Ehcache简介》一文中对CacheManager的介绍我们知道一切Ehcache的应用都是从CacheManager开始的。在不指定配置信

- junit 4.11中三个新功能

jackyrong

java

junit 4.11中两个新增的功能,首先是注解中可以参数化,比如

import static org.junit.Assert.assertEquals;

import java.util.Arrays;

import org.junit.Test;

import org.junit.runner.RunWith;

import org.junit.runn

- 国外程序员爱用苹果Mac电脑的10大理由

php教程分享

windowsPHPunixMicrosoftperl

Mac 在国外很受欢迎,尤其是在 设计/web开发/IT 人员圈子里。普通用户喜欢 Mac 可以理解,毕竟 Mac 设计美观,简单好用,没有病毒。那么为什么专业人士也对 Mac 情有独钟呢?从个人使用经验来看我想有下面几个原因:

1、Mac OS X 是基于 Unix 的

这一点太重要了,尤其是对开发人员,至少对于我来说很重要,这意味着Unix 下一堆好用的工具都可以随手捡到。如果你是个 wi

- 位运算、异或的实际应用

wenjinglian

位运算

一. 位操作基础,用一张表描述位操作符的应用规则并详细解释。

二. 常用位操作小技巧,有判断奇偶、交换两数、变换符号、求绝对值。

三. 位操作与空间压缩,针对筛素数进行空间压缩。

&n

- weblogic部署项目出现的一些问题(持续补充中……)

Everyday都不同

weblogic部署失败

好吧,weblogic的问题确实……

问题一:

org.springframework.beans.factory.BeanDefinitionStoreException: Failed to read candidate component class: URL [zip:E:/weblogic/user_projects/domains/base_domain/serve

- tomcat7性能调优(01)

toknowme

tomcat7

Tomcat优化: 1、最大连接数最大线程等设置

<Connector port="8082" protocol="HTTP/1.1"

useBodyEncodingForURI="t

- PO VO DAO DTO BO TO概念与区别

xp9802

javaDAO设计模式bean领域模型

O/R Mapping 是 Object Relational Mapping(对象关系映射)的缩写。通俗点讲,就是将对象与关系数据库绑定,用对象来表示关系数据。在O/R Mapping的世界里,有两个基本的也是重要的东东需要了解,即VO,PO。

它们的关系应该是相互独立的,一个VO可以只是PO的部分,也可以是多个PO构成,同样也可以等同于一个PO(指的是他们的属性)。这样,PO独立出来,数据持