HDLBits刷题Day6

2.3.6 Adder1

问题陈述

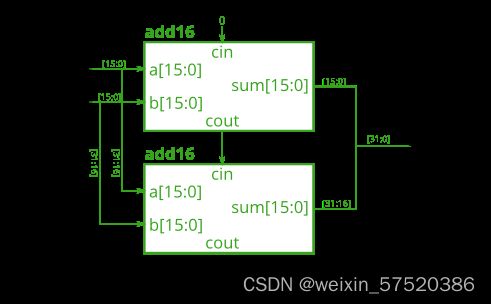

您将获得一个add16执行 16 位加法的模块。实例化其中两个以创建一个 32 位加法器。一个 add16 模块计算加法结果的低 16 位,而第二个 add16 模块在接收到第一个加法器的进位后计算结果的高 16 位。您的 32 位加法器不需要处理进位(假设为 0)或进位(忽略),但内部模块需要才能正常工作。(换句话说,add16模块执行 16 位 a + b + cin,而您的模块执行 32 位 a + b)。

如下图所示将模块连接在一起。提供的模块add16具有以下声明:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0]

sum, output cout );

Verilog代码:

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire [31:0] w1,w2;

wire cout;

assign w1=a;

assign w2=b;

add16 low (.a(w1[15:0]),.b(w2[15:0]),.cin(1'b0),.sum(sum[15:0]),.cout(cout));

add16 high(.a(w1[31:16]),.b(w2[31:16]),.cin(cout),.sum(sum[31:16]));

endmodule

2.3.7 Adder2

问题陈述:

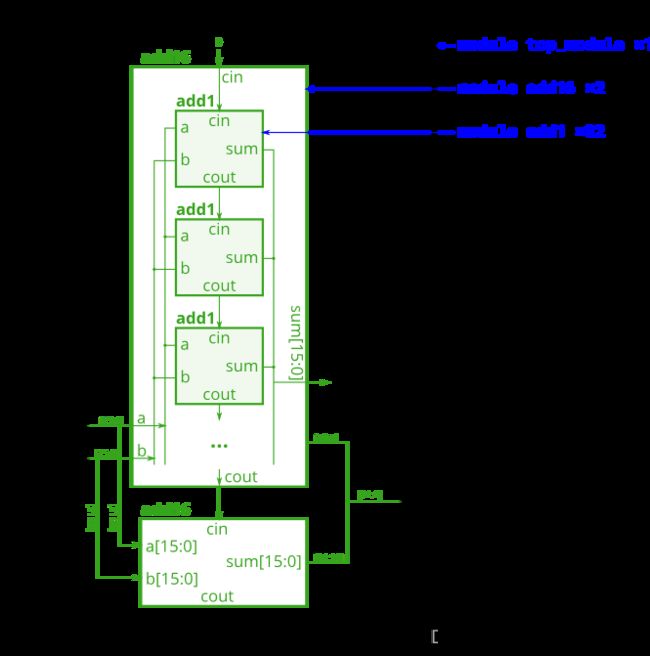

您top_module将实例化add16(提供)的两个副本,每个副本将实例化add1(您必须编写)的 16 个副本。因此,您必须编写两个模块:top_module和add1.

您将获得一个add16执行 16 位加法的模块。您必须实例化其中的两个以创建 32 位加法器。一个add16模块计算加法结果的低 16 位,而第二个add16模块计算结果的高 16 位。您的 32 位加法器不需要处理进位(假设为 0)或进位(忽略)。add16如下图所示将模块连接在一起。提供的模块add16具有以下声明:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0]

sum, output cout );在每个add16中,16 个全加器(模块add1,未提供)被实例化以实际执行加法。您必须编写具有以下声明的完整加法器模块:

module add1 ( input a, input b, input cin, output sum, output cout );

回想一下,全加器计算 a+b+cin 的和和进位。

综上所述,本设计共有三个模块:

top_module— 您的顶级模块包含两个… add16, 提供 — 一个 16 位加法器模块,由 16 个… add1— 1

位全加器模块。如果您的提交缺少 a module add1,您将收到一条错误消息,内容为Error (12006): Node instance

“user_fadd[0].a1” instantiates undefined entity "add1

Verilog代码:

module top_module (

input [31:0] a,

input [31:0] b,

output [31:0] sum

);//

wire cout1;

add16 low(.a(a[15:0]),.b(b[15:0]),.cin(1'b0),.cout(cout1),.sum(sum[15:0]));

add16 high (.a(a[31:16]),.b(b[31:16]),.cin(cout1),.sum(sum[31:16]));

endmodule

module add1 ( input a, input b, input cin, output sum, output cout );

// Full adder module here

assign {cout,sum}=a+b+cin;

endmodule

2.3.8 Carry-select adder

问题陈述:

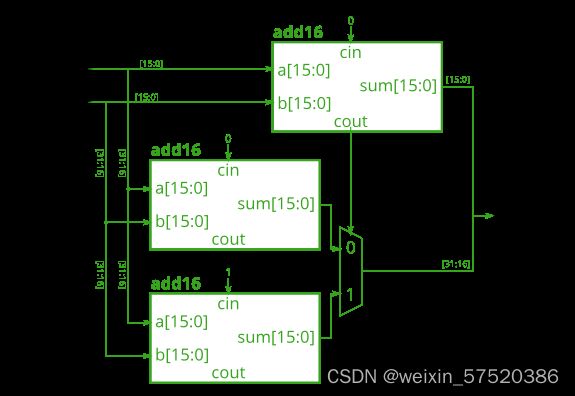

纹波进位加法器的一个缺点是加法器计算进位的延迟(从进位开始,在最坏的情况下)相当慢,并且第二级加法器在第一级加法器完成之前无法开始计算其进位. 这使加法器变慢。一种改进是进位选择加法器,如下所示。第一级加法器与之前相同,但我们复制第二级加法器,一个假设进位=0,一个假设进位=1,然后使用快速2对1多路复用器选择哪个结果碰巧是正确的。

在本练习中,您将获得与上add16一个练习相同的模块,该模块将两个 16 位数字与进位相加,并产生一个进位和 16 位和。您必须使用您自己的

16 位 2 对 1 多路复用器来 实例化其中的三个以构建进位选择加法器。如下图所示将模块连接在一起。提供的模块add16具有以下声明:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0]

sum, output cout );

Veriog代码:

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire cout1;

wire [15:0]sum0,sum1;

add16 one(.a(a[15:0]),.b(b[15:0]),.cin(1'b0),.sum(sum[15:0]),.cout(cout1));

add16 two(.a(a[31:16]),.b(b[31:16]),.cin(1'b0),.sum(sum0));

add16 three(.a(a[31:16]),.b(b[31:16]),.cin(1'b1),.sum(sum1));

assign sum[31:16]=(cout1?sum1:sum0);

endmodule

2.3.8 Adder-subtractor

问题陈述:

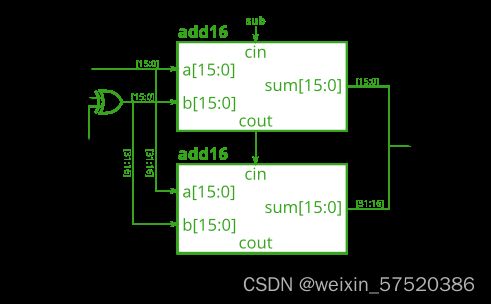

加法器-减法器可以通过选择性地取反一个输入来从加法器构建,这相当于将输入反相然后加 1。最终结果是一个可以执行两个操作的电路:(a + b + 0) 和 ( a + ~b + 1)。构建下面的加减法器。

为您提供了一个 16 位加法器模块,您需要对其进行两次实例化:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0]

sum, output cout );每当sub为 1 时,使用 32 位宽的 XOR 门来反转b输入。(这也可以视为b[31:0]与 sub 复制 32

次进行异或。还将子输入连接到加法器的进位。

Verilog代码:

module top_module(

input [31:0] a,

input [31:0] b,

input sub,

output [31:0] sum

);

wire cout1,cout2;

wire [31:0]out;

assign out=b^{32{sub}};

add16 di(a[15:0],out[15:0],sub,sum[15:0],cout1);

add16 gao(a[31:16],out[31:16],cout1,sum[31:16],cout2);

endmodule

每日总结:

三目运算符(?:)

1.格式:

条件表达式?真的表达式:假的表达式

2.可以嵌套使用

例子:

reg out,M,CTL,CLT,A,B,C,D;

assign OUT=(M==1?(CLT?A:B):(CLT?C:D));//四选一多路选择器