Design Compiler

1.

DC默认的设计环境:同步时钟,上升沿

2.

时钟路径划分以及判断约束是否满足步骤

三个步骤:a. 把需要综合的设计拆分成时序路径的组合

b. 计算每条路径的延时

c. 用路径延时和期望到达的时间作比较,判断约束是否满足

四条路径

起始点:输入端口(不包括时钟端口),时钟引脚

终点: 输出端口(不包括时钟端口),时序逻辑的输入引脚(不包括时钟引脚)

3.

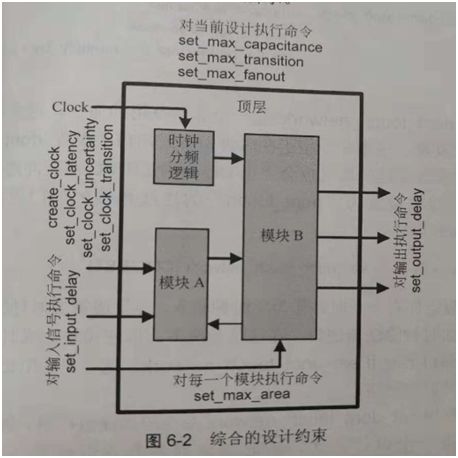

设定时钟的period,latency,transiton,uncertainty,还有对所有的输入信号执行命令input delay,对所有的输出信号执行命令 output delay。

对当前设计执行命令set_max_capacitance,set_max_transition,set_max_fanout

对每一个模块执行命令set_max_area

4.

create_clock命令用于定义有特定周期和波形的时钟对象,-period选项定义时钟周期,而-waveform选项控制时钟的占空比和起始边沿。

下例指定端口Clk为时钟类型,周期2ns,时钟正边沿开始于0ns,下降边沿发生在1ns,通过改变下降沿的值,可以改变时钟的占空比。

create_clock -period 2 -waveform [list 0 1] [get_ports Clk] 时钟的单位由工艺库定义,通过report_lib

此时钟的时钟周期为2ns。如果creat_clock命令中没有 -waveform 选项,则时钟默认 rises at 0ns with 50% duty cycle 。

注意:

在某些情况下,模块可能只包括组合逻辑,为定义这一模块的延迟约束,可生成一个虚时钟,并指定相对于虚时钟的输入和输出延迟。也可选择使用set_max_delay和set_min_delay来约束这样的模块。

create_generated_clock命令用于设计内部生成的时钟。这一命令可用于描述作为主时钟函数的分频/倍频时钟。

create_generated_clock -name