高速高精密ADC数据采集-ADS62P49

此篇是我在学习中做的归纳与总结,其中如果存在版权或知识错误或问题请直接联系我,欢迎留言。

PS:本着知识共享的原则,此篇博客可以转载,但请标明出处!

目录

0、ADS62P49特性

1、实现框架

2、配置模块

3、同步校准

4、数据提取

5、测试

参考资料:

0、ADS62P49特性

TI公司的模/数转换芯片ADS62P49。如表所示,该芯片可以实现双通道14位高速高精度数据采集,最大采样速率可达250MSPS。它结合了高动态性能和低功耗在一个紧凑的64-QFN封装中,这使得它非常适合多载波、宽带通信应用。

表 ADS62P49主要参数

| 主要参数 |

典型值 |

| 最大采样率 |

250MSPS |

| 分辨率 |

14bit |

| 功耗 |

1.25W@250MSPS |

| SFDR-LVDS |

75dBc |

| SINAD-LVDS |

69.8dBFS |

ADS62P49具有增益选项,可用于提高较低满量程输入范围下的SFDR性能。它包括一个DC偏移校正环路,可以用来消除ADC偏移。DDR LVDS (Double Data Rate)和并行CMOS数字输出接口都是可用的,该芯片具备灵活的配置特性,同时又能实现很好的高速性能。

1、实现框架

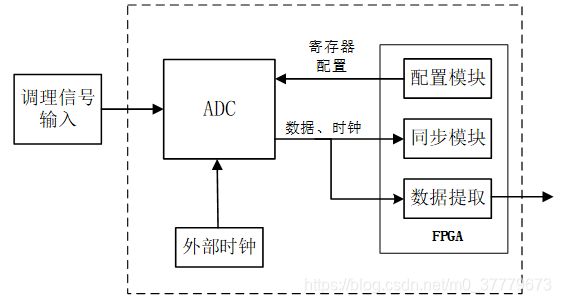

将经过模拟接收链路后的电信号作为ADS62P49芯片的输入,通过该芯片完成对信号的模数转换,并将转化后的数字信号输出到Zynq中。其ADC数据采集实现框图如图1所示。

图1 ADC数据采集实现框图

当ADS62P49经过配置后处于正常的工作状态后,要保证能正确提取有效数据就必须要保证正确的数据与时钟的相位关系。在FPGA提取发送来的数据之前,需要设计位时钟同步模块来保证时钟与数据流正确的相位关系。

2、配置模块

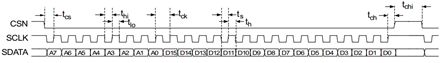

ADS62P49芯片配置寄存器是通过一个串行端口接口(SPI)来访问的,该串行接口由SDATA(串行接口数据)、SCLK(串行接口时钟)和CSN(片选,低电平有效)引脚组成。当CSN设为低电平时,发生下列事件:

1.串行数据移入芯片

2.在SCLK的每个上升沿,锁存SDATA上存在的值

3.在SCLK的每第24个上升沿,SDATA载入寄存器

图2显示了具体的串行端口接口时序,保证正确有效的数据发送。

图2 串行端口接口(SPI)时序

3、同步校准

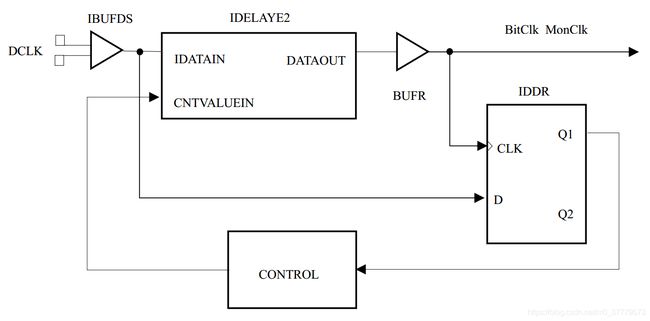

理想情况下ADC提供的位时钟相对于数据和帧时钟信号是90°,但由于FPGA网格内的路由和时钟缓冲延迟,所以必须重新定位位时钟以捕获数据和帧时钟信号。

保持正确有效的相位关系本质上是为了保证数据信号有足够建立时间和保持时间,同步校准是为了满足数据进入寄存器时拥有有效的建立和保持时间。本文中时钟同步校准设计映射电路如图3所示。

图3 时钟同步校准设计映射电路

如图3所示,来自ADC的位时钟DCLK通过用于可变模式的IDELAYE2路由到 BUFR的输入。DCLK变为BitClk_MonClk(对齐后的DCLK)。DCLK也作为数据输入于IDDR的D输入端。IDDR的Q1作为数据输入于CONTROL,当这个数据处于稳定状态(一直为0或一直为1)时,通过递增或递减IDELAYE2的节拍数量从IDDR的CLK中增加或减少IDELAYE2延迟,直至数据正确采集,此时象征着内部时钟与外部时钟对齐。

时钟同步校准设计主要由以下几种关键部分组成:

(1)IBUFDS原语是为了将差分信号输入转为单端信号使用。而对于时钟信号来说,该单元不仅将差分时钟转为单端时钟,还提升了时钟信号的驱动能力,这对于数据采样速率很高的ADC来说是非常重要的一步。

(2)IDDR是专门为接收双倍数据速率(DDR)的输入信号而设计的单元,它的输出有以下三种工作模式:OPPOSITE_EDGE模式、SAME_EDGE模式和SAME_EDGE_PIPELINE模式。SAME_EDGE和SAME_EDGE_PIPELINE模式允许设计中将下降的边缘数据传输到ILOGIC块内上升的边缘域,节省了CLB和时钟资源,并提高了性能。本文采取的是SAME_EDGE_PIPELINE模式,图4是该模式的工作时序:

图4 SAME_EDGE_PIPELINE模式下工作时序

(3)IDELAYE2原语是用来调节输入信号的延迟的可编程单元,该原语一般选择200MHz时钟作为IODELAYE2的参考时钟,具有32个可调步长,每个步长78ps的延迟时间。

IDELAYCTRL IDELAYCTRL_inst (

.RDY(RDY), // 1-bit output: Ready output

.REFCLK(clk200m), // 1-bit input: Reference clock input

.RST(rst) // 1-bit input: Active high reset input

);

(* IODELAY_GROUP = "ADC_DCLK_DELAY" *) // Specifies group name for associated IDELAYs/ODELAYs and IDELAYCTRL

IDELAYE2 #(

.CINVCTRL_SEL("FALSE"), // Enable dynamic clock inversion (FALSE, TRUE)

.DELAY_SRC("IDATAIN"), // Delay input (IDATAIN, DATAIN)

.HIGH_PERFORMANCE_MODE("TRUE"), // Reduced jitter ("TRUE"), Reduced power ("FALSE")

.IDELAY_TYPE("FIXED"), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE

.IDELAY_VALUE(5'h0E), // Input delay tap setting (0-31)

.PIPE_SEL("FALSE"), // Select pipelined mode, FALSE, TRUE

.REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz (190.0-210.0, 290.0-310.0).

.SIGNAL_PATTERN("CLOCK") // DATA, CLOCK input signal

)

IDELAYE2_inst (

.CNTVALUEOUT(cntvalueout), // 5-bit output: Counter value output

.DATAOUT(a_adc_dclk_delay), // 1-bit output: Delayed data output

//.C( 1'b1 ), // 1-bit input: Clock input a_adc_clk_bufio_div_4

.C( a_adc_clk_bufio ), // 1-bit input: Clock input

.CE(1'b0), // 1-bit input: Active high enable increment/decrement input

.CINVCTRL(1'b0), // 1-bit input: Dynamic clock inversion input

.CNTVALUEIN(cntvaluein), // 5-bit -input: Counter value input

.DATAIN(1'b0), // 1-bit input: Internal delay data input

.IDATAIN(a_adc_dclk), // 1-bit input: Data input from the I/O

.INC(1'b0), // 1-bit input: Increment / Decrement tap delay input

.LD( LD ), // 1-bit input: Load IDELAY_VALUE input

.LDPIPEEN(1'b0), // 1-bit input: Enable PIPELINE register to load data input

.REGRST(~RDY) // 1-bit input: Active-high reset tap-delay input

);

注意:IDELAY_TYPE("FIXED")中FIXED模式为延时步长确定后的IDELAY2工作模式,当测试时,使用VAR_LOAD模式,以减小测试步骤中的工作量

(4)区域时钟缓冲器(BUFR)是同步校准过程中用到的另一种时钟缓冲器,该缓冲器用来指定将时钟信号驱动到独立于全局时钟树的专用时钟网络上。

需要注意的是,BUFR可以由具有时钟功能的引脚、本地互连和MMCMs HPCs (CLKOUT0到CLKOUT3)或位于相同和相邻区域的BUFMRS驱动;

在7系列的FPGA中,一个BUFR可以驱动缓冲器自身所处区域的四个区域时钟网,而且可以驱动该区域内的I/O逻辑和逻辑资源(CLB、块RAM等)。

综上所述,BUFR非常适合需要时钟域交叉或串并联转换的源同步应用程序。

高速ADC采集时的同步跟踪功能是当FPGA布局布线完成,电路的延迟已经固定后完成的,因此IDELAYE2通过遍历即可以确定最合适的延迟。该模块的部分RTL门级电路见图5所示:

图5 位同步模块部分RTL实现电路

4、数据提取

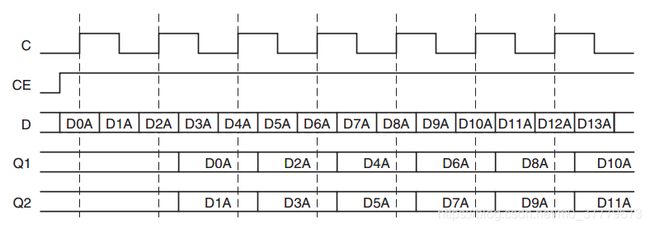

当位时钟边沿对齐后,数据的建立时间和保持时间都得到了满足,这时可以确保每一位提取到的数据是有效的。ADS62P49数据采集后通过LVDS模式以双倍数据速率(DDR)并行输入FPGA中,如图6所示,数据提取以同步校准后的BitClk_MonClk作为时钟,通过IBUFDS和IDDR原语对数据进行提取,以正确获得采集的双通道14bit采集数据。

图6 数据提取设计映射电路

module UA_adc_data_receive(

input a_adc_clk_bufio , //Bit clock

//input a_adc_clk_bufio2 ,

input rst ,

input [13:0] adc_dxp , //P of DB12 DB10 DB8 DB6 DB4 DB2 DB0 , DA12 DA10 DA8 DA6 DA4 DA2 DA0

input [13:0] adc_dxn , //N of DB12 DB10 DB8 DB6 DB4 DB2 DB0 , DA12 DA10 DA8 DA6 DA4 DA2 DA0

output reg [13:0] Q_Simple_N_A ,

output reg [13:0] Q_Simple_N_B

);

wire rst_n;

assign rst_n = ~rst;

wire [13:0] Q1 ;

wire [13:0] Q2 ;

wire [13:0] adc_dx ;

wire [13:0] adc_dx_n ;

genvar index;

generate

for (index=0; index< 14;index=index+1) begin

IBUFDS_DIFF_OUT #(

.DIFF_TERM("TRUE"), // Differential Termination, "TRUE"/"FALSE"

.IBUF_LOW_PWR("FALSE"), // Low power="TRUE", Highest performance="FALSE"

.IOSTANDARD("LVDS_25") // Specify the input I/O standard

) IBUFDS_inst_adc_dx (

.O(adc_dx[index]), // Buffer output

.OB(adc_dx_n[index]), // Buffer diff_n output

.I(adc_dxp[index]), // Diff_p buffer input (connect directly to top-level port)

.IB(adc_dxn[index]) // Diff_n buffer input (connect directly to top-level port)

);

IDDR #(

.DDR_CLK_EDGE("SAME_EDGE_PIPELINED"), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1(1'b0), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2(1'b0), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) IDDR_inst (

.Q1( Q1[index] ), // 1-bit output for positive edge of clock

.Q2( Q2[index] ), // 1-bit output for negative edge of clock

.C( a_adc_clk_bufio ), // 1-bit clock input

.CE( 1'b1 ), // 1-bit clock enable input

.D( adc_dx[index] ), // 1-bit DDR data input

.R( 1'b0 ), // 1-bit reset

.S( 1'b0 ) // 1-bit set

);

end

endgenerate

always@(posedge a_adc_clk_bufio or negedge rst_n) begin

if(~rst_n) begin

Q_Simple_N_A <= 0 ;

Q_Simple_N_B <= 0 ;

end else begin

Q_Simple_N_A <= {Q2[6],Q1[6],Q2[5],Q1[5],Q2[4],Q1[4],Q2[3],Q1[3],Q2[2],Q1[2],Q2[1],Q1[1],Q2[0],Q1[0]};

Q_Simple_N_B <= {Q2[13],Q1[13],Q2[12],Q1[12],Q2[11],Q1[11],Q2[10],Q1[10],Q2[9],Q1[9],Q2[8],Q1[8],Q2[7],Q1[7]};

end

end5、测试

当高速ADC芯片功能配置、时钟同步校准和数据提取功能完成后,从ADC配置到ADC发送数据、数据经过路由进入FPGA再到FPGA处理数据的有效性都可以得到保证。

ADS62P49芯片的提供了几种已知的数据模式(输出常0、常1、递增序列)便于开发测试,该模式可通过配置ADC来实现,这使得人为判断数据采样数据是否正确成为可能。本课题中,设置ADC发送递增序列码,那么最终查看得到的数据是否递增即可完成验证。

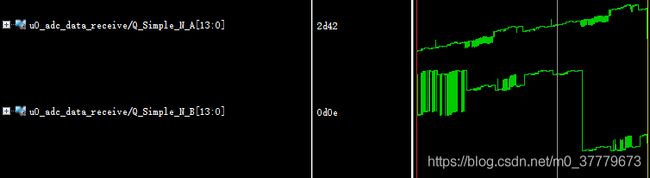

图7 ADC递增采集ila波形图 (a) 同步前波形图 (b) 同步后波形图

使用Vivado设计软件中ILA IP核抓取ADC采集信号,如图7所示:同步校准后的递增采集数据无异常数据出现,说明同步校准功能实现良好。

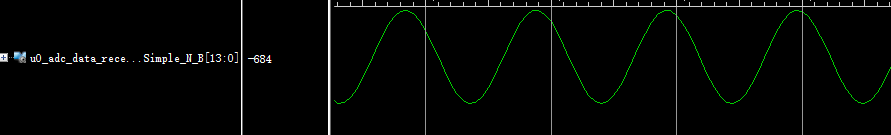

配置ADC工作模式为外部信号采集,输入10MHz、0dBm的正弦波信号,其同步校准后的数据ila波形图如图8所示。

图5-29 ADC正弦波采集ila波形图

参考资料:

- Texas Instruments, Inc. ADS62P49 Datasheet[EB/OL]. https://www.ti.com.cn/product/ADS62P49.pdf

- ug471_7Series_SelectIO

- ug472_7Series_Clocking

- xapp524-serial-lvds-adc-interface