VHDL硬件描述语言(一)基本概念

一、EDA技术概述

电子设计自动化(EDA)技术是新一代电子设计工程师及从事电子技术开发和研究人员的必备技能,也是电子技术类专业学生学习的重要内容。

EDA以功能强大的计算机为工具,在EDA工具软件平台上,根据设计文件(硬件描述语言 Hardware Description Language为系统的主要逻辑描述手段),自动完成编译、仿真、综合、优化、适配(或布局布线)以及下载,实现既定的电子线路系统功能。

典型的EDA工具应包括:编译器、仿真器、综合器、适配器和下载器。

二、EDA技术的基本特征

- “自顶向下”设计方法:根据系统功能将整个系统划分为 若干功能模块,而后对功能模块进行逻辑设计。

- 用硬件描述语言来描述数字电路与系统 :在系统级、算 法级、RTL(又称数据流级)和门级各个层次上进行描述。

- 综合及优化 :把较高层次的描述转换到较低层次描述的 过程,从行为级到RTL级,从RTL级到门级。并且可根据综合 结果对设计进行优化。

- 开放性与标准化的框架结构 :建立与硬件平台无关的图 形用户界面以及工具之间的通信、设计数据和设计流程的管 理平台,为EDA工具提供操作环境。

- 库(Library)的引入:模拟库、综合库、版图库。

三、EDA技术的常用设计工具

- Synopsys:逻辑综合、逻辑验证

- Cadence:前端仿真、版图工具

- Mentor-Graphics:自动测试、提取验证

四、硬件描述语言

HDL(Hardware Description Language)是硬件描述语言的缩写,是用于设计硬件电子系统的计算机语言,它描述系统的逻辑功能、电路结构和连接方式,是EDA技术应用中最主要的设计输入方法之一。

当前常用的HDL主要有:ABEL-HDL、VHDL和VERILOG-HDL。

- ABEL-HDL主要用于数字系统寄存器传输级的描述,其特点是格式简洁、易学、易用,编译要求宽松,适合初学者使用。早期主要应用于PLD器件。

- Verilog-HDL主要用于数字系统寄存器传输级的描述,其学习相对来说也比较容易。Verilog-HDL主要是在集成电路设计中应用。

- VHDL主要也是用于描述数字系统的结构、行为、功能和接口,但其行为描述能力更强,是数字系统设计领域最佳的硬件描述语言之一。VHDL学习难度相对要大一些。

五、数字系统的概念

逻辑器件:门、触发器;

逻辑功能部件:由逻辑器件构成,能执行某个单一功能的电路,如计数器、译码器、加法器等;

数字系统:由若干逻辑部件组成,能实现复杂功能的电路

通常说来,系统与部件之间的区别在于功能是否单一:一个存储器尽管规模很大,可达数兆字节,但因其功能单一,只能称为部件;而只需几片MSI器件即可实现的数字锁控制电路却应称之为系统

近年来,数字系统的设计大多仿效计算机组成方式,将整个系统分为控制器和受控器二部分(或分成控制器、处理器和存储器三个部分)。

在这种结构下,系统与部件的区别就在于其中有无控制器:一个数字电路,无论其规模大小,必须具有控制器才可称之为系统。

六、数字系统设计流程

- 自顶向下设计方法(Top-Down Desgin)

分层次的:

先做顶层设计(概念设计、总体框图,抽象级别较高 的设计)

后做底层设计(子系统、子电路,接近物理实现的设 计)

每一层次,都要进行描述、划分、综合、验证

- 自底向上设计方法(Bottom-Up Design)

- 混合式设计方法(mixed Design)

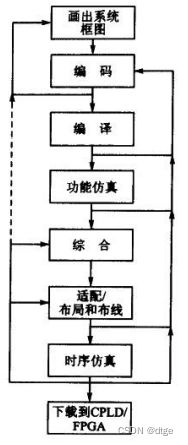

(1)系统层次划分/画出系统框图

按照“自顶向下”的设计方法对系统进行划分(确定系统由那些模块构成,个模块又由哪些子模块构成)

(2)编码

写出VHDL代码。

(3)编译

编译器会对VHDL程序进行语法检测,还会产生用于仿真的一些内部信息。这一步通常由编译器自动完成,无需我们干预。如果VHDL语法有错误,需要回到第(2)步修改程序。

(4)功能仿真

VHDL仿真器允许定义输入并应用到设计中去,不必生成实际电路就可以观察输出。此仿真功能只要用于检测系统功能设计的正确性,不涉及具体器件的硬件特性。

(5)综合

利用综合器对VHDL代码进行综合优化处理,生成门级描述的网表文件,这是将VHDL语言描述转化为硬件电路的关键步骤。这一步通常由综合器自动完成,但设计者可以设定一些技术上的约束条件(如限定逻辑层次的最大数等)来“帮助”综合器。

(6)适配

利用适配器将综合后的网表文件针对某一具体的目标器件进行逻辑映射操作,包括底层器件配置、逻辑分割、逻辑优化、布局布线等。此步骤将产生多项设计结果:

- 适配报告,包括芯片内部资源的利用情况、设计的布尔方程描述情况等;

- 适配后的仿真模型;

- 器件编程文件。

(7)时序仿真

根据适配后的仿真模型,可以进行时序仿真。因为这时已经得到目标器件的实际硬件特性(如时延特性等),所以仿真结果能比较精确地预期芯片的实际性能。如果仿真结果达不到设计要求,就需要修改VHDL源代码或选择不同的目标器件,甚至要重构整个系统(看到图1- 1里那个虚线的箭头了吗?这是所有设计者极力避免出现的情况)。

(8)下载到CPLD/FPGA

如果时序仿真通过,那么可以将‘适配”时产生的器件编程文件下载到CPLD或FPGA中。(FPGA的编程通常被称为“配置”)。虽然流程图中未标出从此步“往回走”的箭头,但事实上,实际的结果有可能与仿真结果有差异(可能是设计时未考虑到外部硬件的实际情况;也可能是由于仿真时测试的条件不够多,没有发现其中隐藏的错误),这时,必须再回头重新找出问题所在。

七、可编程逻辑器件基础

PLD的应用和发展简化了电路设计、降低了成本,提高了系统的可靠性和保密性,推动了EDA工具的发展,而且改变了数字系统的设计方法。

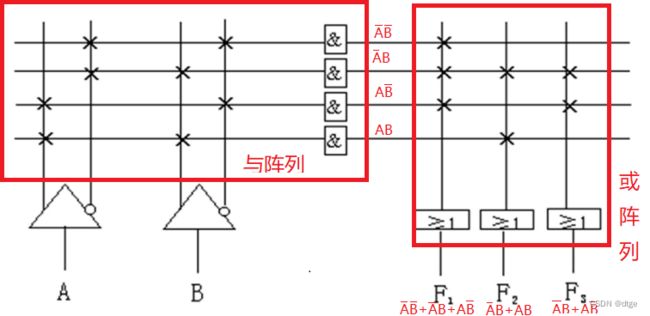

PLD(可编程逻辑器件)的基本结构有两种:与或阵列结构和查找表结构

7.1与或阵列结构

任何一个逻辑函数都可以用与—或逻辑式表示,亦即用一个与—或阵列来实现。

7.2查找表的概念

- 一个N输入查找表 (LUT,Look Up Table)可以实现N个输入变量的任何组合逻辑功能,如N输入“与” 、 N输入“异或”等。

- 输入多于N个的逻辑函数、逻辑方程等必须分开用几个查找表( LUT)实现。

使用多路开关实现,其基本原理是将多路开关的数据输入端接固定电平,将其地址输入作为函数的输入,多路开关的输出为逻辑函数值。

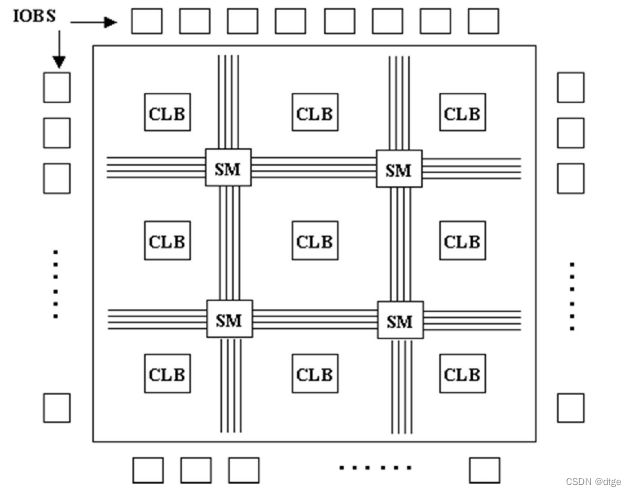

7.3 PLD分类

1)按集成度分类

- 低密度PLD:ROM、PAL、GAL等

- 高密度PLD:EPLD CPLD、FPGA等

2)按结构分类

- 阵列型:“与阵列+或阵列+寄存器”的形式,如PAL、GAL、CPLD等

- 单元型:“查找表+寄存器”的形式,如FPGA。

3)按编程工艺分类:

- ROM: 称为掩膜编程,由半导体生产厂家对器件进行编程;

- PROM: 使用熔丝或反熔丝编程器件,一次性编程;

- EPROM: 紫外线擦除/电编程,可多次编程;

- EEPROM: 电擦除/电编程,可多次编程。和EPROM相比,具有擦除方便和编程速度快的优点;

- SRAM: 使用SRAM为编程器件,可多次编程。