spi时序图怎么分析,怎么看懂spi时序图

我做产品的时候,最怕就是做IIC和SPI的通信。

这两种协议时序哪怕是延时时间有误差,都有可能导致通信不上。

出现问题的时候,如果没设备也很难排查问题到底出在哪里。

有时候这个产品写好的时序程序,换一个单片机用同一个程序移植过去就不行了。

而且很多公司都没有设备可以调试这些协议,大多数时候都是完全靠蒙。

今天就拿新手比较头痛的SPI来进行时序图的分析和讲解,看不懂你打我!

我记得第一次SPI通讯的时候,完全是照抄网络上的程序,因为芯片手册的时序图看起来太可怕了,根本看不懂。

后面各种模拟时序写多了,才有了经验,然后用经验去理解数据手册以及网络上的教程。

很多新手看各种数据手册和教程被吓到了,其实很多时候不是你的问题,而是数据手册和教程写的太学术化了。

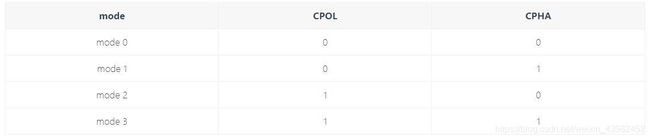

举个例子,就像SPI协议用CPOL和CPHA真值表来选择不同的模式。

因为在很多SPI接口芯片的数据手册根本没提CPOL和CPHA这两个东西,那要怎么知道芯片的通讯模式?

其实是要我们自己根据芯片手册的时序图去分析模式的,而不会直接告诉你是用的哪个模式。

所以在看时序之前,我们先要了解CPOL和CPHA到底有啥区别。

CPHA是用来控制数据是在第一个跳变沿还是第二个跳变沿采集的。

通过上图可以看到:

CPHA=0的时候,数据是在第一个跳变沿的时候就会被采集。

CPHA=1的时候,数据是在第二个跳变沿的时候才会被采集。

那问题来了,到底是上升沿还是下降沿采集?

这个就由CPOL来决定了:

CPOL=0的时候是上升沿采集。

CPOL=1的时候是下降沿采集。

除此以外,CPOL还决定了我们时钟线SCLK空闲时的状态。

CPOL=0的时候表示SCLK在空闲时为低电平。

CPOL=1的时候表示SCLK在空闲时为高电平。

Ok,明白了这个,我们再分析4种模式的时序图。

1.模式0(CPOL=0 CPOL=0)

CPOL = 0:时钟线空闲时是低电平,第1个跳变沿是上升沿,第2个跳变沿是下降沿

CPHA = 0:数据在第1个跳变沿(上升沿)采样

时序图如下:

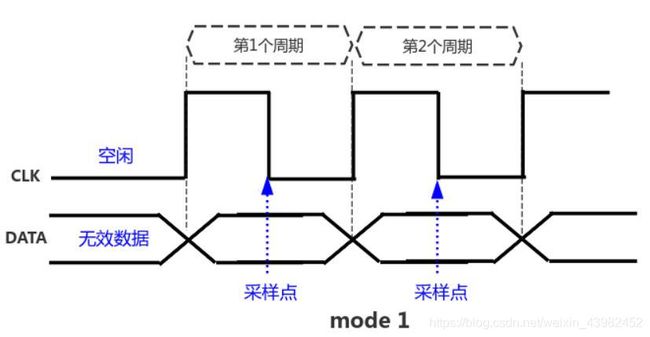

2.模式1(CPOL=0 CPOL=1)

CPOL = 0:空闲时是低电平,第1个跳变沿是上升沿,第2个跳变沿是下降沿

CPHA = 1:数据在第2个跳变沿(下降沿)采样

时序图如下:

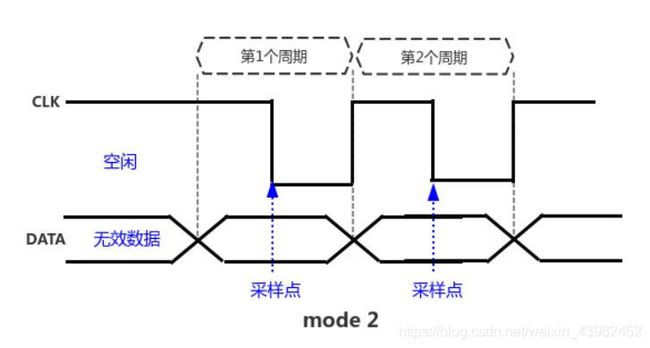

3.模式2(CPOL=1 CPOL=0)

CPOL = 1:空闲时是高电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿

CPHA = 0:数据在第1个跳变沿(下降沿)采样

时序图如下:

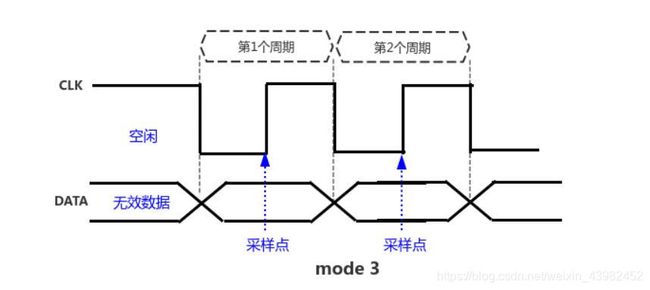

4.模式3(CPOL=1 CPOL=1)

CPOL = 1:空闲时是高电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿

CPHA = 1:数据在第2个跳变沿(上升沿)采样

时序图如下:

这样看是不是对4种模式的区别比较清晰了?

下面,我们再拿OLED的驱动芯片SSD1306的时序图来作为实战讲解。

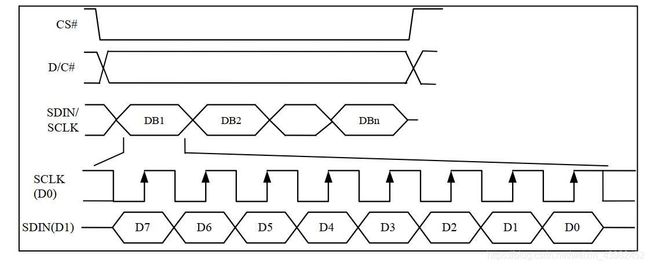

SSD1306的4线SPI通讯时序如下:

从这个时序图可以看出几个关键点:

- 在发送数据之前,要把CS引脚拉低。

- D/C一般是用来控制发送命令还是数据的。

- 数据在第二个SCLK跳变开始传输。

- 数据在SCLK上升沿的时候进行传输,每次发送一个Bit,高位在前。

所以,由这个时序图可以判断出来,用的是SPI模式3的通讯方式。

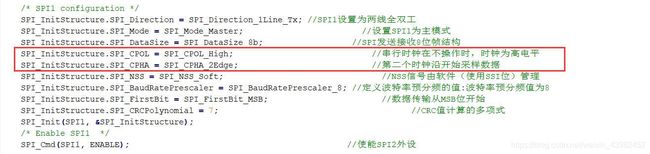

知道这个之后,你就知道单片机的硬件SPI模式要怎么配置了(下图以STM32为例)。

ok,今天时间关系,就先写到这里,如果赞多的话再回来更。