vivado报错信息学习过程更新

verilog调试过程

1.先进入tools进行window preference进行变量地址显示1——>2

2.从信号报错的先后/因果找

3.先找tb的错误到例化模块的错误,因为信号是从tb到模块中

3.例化模块中使用ctrl+f进行变量查找进行溯源,进行变量排查

eg:在2023年3月25日老师的指导中,我个人完成了tb文件的排查,在例化模块中对于rx_frame_in_p/n一半不定态的错误我个人顺流直下模式中疏忽了rx_frame_in本来是input而在IDDR_rx_frame_inst原语中做了output。老师通过从错误信号到rx_shift到rx——iddr追溯出错误是rx_frame_iddr_p写成rx_frame_in_p/n重复定义的错误。

1、 2022/10/19

根据报错信息的文件详细信息找到E:\Xilinx_FPGA\Project\led_plum07a1\led_plum07a1.sim\sim_1\behav\xsim\avlog.log日志文件查看详细信息,报错信息如下

INFO: [VRFC 10-2263] Analyzing Verilog file "E:/Xilinx_FPGA/Project/led_plum07a1/led_plum07a1.srcs/sources_1/new/led_07a3plum.v" into library xil_defaultlib

INFO: [VRFC 10-311] analyzing module led_07a3plum

WARNING: [VRFC 10-3248] data object 'Ledflag' is already declared [E:/Xilinx_FPGA/Project/led_plum07a1/led_plum07a1.srcs/sources_1/new/led_07a3plum.v:15]

ERROR: [VRFC 10-3703] second declaration of 'Ledflag' ignored [E:/Xilinx_FPGA/Project/led_plum07a1/led_plum07a1.srcs/sources_1/new/led_07a3plum.v:15]

ERROR: [VRFC 10-2865] module 'led_07a3plum' ignored due to previous errors [E:/Xilinx_FPGA/Project/led_plum07a1/led_plum07a1.srcs/sources_1/new/led_07a3plum以第一个错误ERROR为例

ERROR: [VRFC 10-3703] second declaration of 'Ledflag' ignored//错误原因 [E:/Xilinx_FPGA/Project/led_plum07a1/led_plum07a1.srcs/sources_1/new/led_07a3plum.v://错误文件位置15//错误地址]

从对应的仿真文件.v中对应文件看对应行数,一般这种报错是逻辑错误如这一次是reg [7:0]Ledflag;在仿真与tb文件中重复定义,语法错误vivado自带的语法检查器会下划线红色波浪提示修正。

2、2022/10/20

有关于冤种忘记三位二进制只能表示0~7而对于Led[]采用1~8导致找了昨天一天加今天一个上午为什么输入是10000110输出波形是10001000因为 8:Led <= Ledflag[7];counter2为8时溢出为0重新取了零位。

附上全部代码,注意错误是case语句中应该是0~7而我写成1~8!!!因为计数变量从0开始警钟长鸣!!!

在后续学习中在分段中多放一个中间态有助于逻辑攥写如加一个case10.

module led_07a4(

Clk,

Reset_n,

Ledflag,

Time,

Led

);

input Clk;

input Reset_n;

input [32:0]Time;

input wire [7:0]Ledflag;

output reg Led;

reg [32:0]counter;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

counter <= 0;

else if(counter == Time-1)

counter <= 0;

else

counter <= counter +1'd1;

reg [2:0]counter2;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

counter2<=0;

else if(counter == Time -1)

counter2 <=counter2 + 1'b1;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

Led<=0;

else case(counter2)

1:Led <= Ledflag[0];

2:Led <= Ledflag[1];

3:Led <= Ledflag[2];

4:Led <= Ledflag[3];

5:Led <= Ledflag[4];

6:Led <= Ledflag[5];

7:Led <= Ledflag[6];

8:Led <= Ledflag[7];

default:Led<=Led;

endcase

endmodule3、2022/11/24

(1)if(time_cnt ==1)与if(time_cnt )前者只等与为1,后者大于1,就不断执行语句!!!

(2)报错Module uart_plum1 doesn't have a timescale but at least one module in design has a timescale.前添加`timescale 1ns/1ns

4、2022年11月29日

(1)Verilog中无法计算小数每一步都会舍去数据最后造成较大误差

eg:Bps_DR = 1000000000/115200/16/20 - 1=27.126,但是Bps_DR在图中表示为26注意。

(2)对于正常一个周期完成下一个周期丢失,即只有一个周期要注意开始与结束信号,在逻辑没有问题的时候要注意数据的浮点丢失如上面第一个,照成可能开始信号在结束信号之前然后逻辑吃掉。

5、

malformed condutional expection

原因条件判断时First_wr_n == 0写成First_wr_n = 0,由判断语句变成赋值语句

6、2023年3月5日

vivado和modelsim联合仿真卡在启动modelsim

1.关闭当前工程,简单工程文件仿真成功证明两者互联成功

2.单独用vivado仿真查看代码报错信息。原来代码有错无法启动,特别是wire与reg在sublime语法提示不显示

3.procedural assignment to a non-register wr_data is not permitted, left-hand side should be reg/integer/time/genvar

已经提示了reg与wire变量的问题

6.2023年3月24日

要注意一个点就是分清楚tb模块的变量和例化里面模块的变量他们是同名但是在仿真图中弄混而不理解当不定阻态产生后到底是tb文件问题还是主模块问题

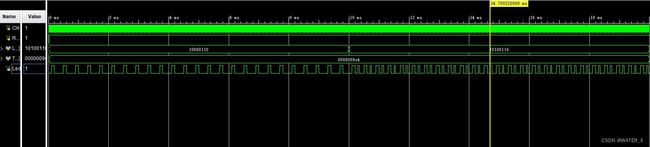

像该图两个rx_frame_in_p数据上面那个tb没有问题但是进入模块后产生不定态了。

6.2023年3月27日

[Place 30-378] Input pin of input buffer inst_ad936x_rxtx_wrapper/ad936x_rxtx_i/ad936x_dev_if_idelay_0/inst/IBUFDS_rx_frame_inst has an illegal connection to a logic constant value.

这个错误的意思是[位置30-378]输入缓冲器inst_add936x_rxtx_wrapper/ad936x_rxtx_i/ad936x_dev_if_idelay_0/inst/IBUFDS_rx_frame_inst的输入引脚与逻辑常数值存在非法连接。

发生在ad936x_dev_if_idelay_0的模块使用错误,在检查ad936x_dev_if_idelay_0模块的IBUFDS_rx_frame_inst没有问题后,寻找把该设计ip使用在diagram中,输入输出引脚是直接做成输入输出到top层,在demo顶层中发现是输入引脚书写错误导致没有输入造成的错误。

追溯原则加验证原则,下次直接先给demo一个tb文件验证错误在一点点排查,不然直接比特流文件速度太慢了。