Modelsim 使用教程(4)—— Working With Multiple Libraries

一、概述

在文中,我们将练习使用多个库。在实际的项目开发过程中,我们可能有多个库来组织设计,从第三方源代码访问IP,或者在仿真之间共享公共部分。我们将通过创建一个包含计数器设计单元的资源库来开始本文。接下来,我们将创建一个项目,并将测试台编译到其中。最后,我们将链接到包含计数器的库,然后运行模拟。

二、设计文件及tb

2.1 设计文件 counter.v

// Copyright 1991-2014 Mentor Graphics Corporation

//

// All Rights Reserved.

//

// THIS WORK CONTAINS TRADE SECRET AND PROPRIETARY INFORMATION WHICH IS THE PROPERTY OF

// MENTOR GRAPHICS CORPORATION OR ITS LICENSORS AND IS SUBJECT TO LICENSE TERMS.

//

`timescale 1ns / 1ns

module counter (count, clk, reset);

output [7:0] count;

input clk, reset;

reg [7:0] count;

parameter tpd_reset_to_count = 3;

parameter tpd_clk_to_count = 2;

function [7:0] increment;

input [7:0] val;

reg [3:0] i;

reg carry;

begin

increment = val;

carry = 1'b1;

/*

* Exit this loop when carry == zero, OR all bits processed

*/

for (i = 4'b0; ((carry == 4'b1) && (i <= 7)); i = i+ 4'b1)

begin

increment[i] = val[i] ^ carry;

carry = val[i] & carry;

end

end

endfunction

always @ (posedge clk or posedge reset)

if (reset)

count = #tpd_reset_to_count 8'h00;

else

count <= #tpd_clk_to_count increment(count);

/*****************************************************************

Use the following block to make the design synthesizable.

always @ (posedge clk or posedge reset)

if (reset)

count = 8'h00;

else

count <= count + 8'h01;

******************************************************************/

endmodule2.2 仿真文件 tcounter.v

//

// Copyright 1991-2014 Mentor Graphics Corporation

//

// All Rights Reserved.

//

// THIS WORK CONTAINS TRADE SECRET AND PROPRIETARY INFORMATION WHICH IS THE PROPERTY OF

// MENTOR GRAPHICS CORPORATION OR ITS LICENSORS AND IS SUBJECT TO LICENSE TERMS.

//

`timescale 1ns / 1ns

module test_counter;

reg clk, reset;

wire [7:0] count;

counter dut (count, clk, reset);

initial // Clock generator

begin

clk = 0;

forever #10 clk = !clk;

end

initial // Test stimulus

begin

reset = 0;

#5 reset = 1;

#4 reset = 0;

end

initial

$monitor($stime,, reset,, clk,,, count);

endmodule 三、创建资源库(Creating the Resource Library)

在创建资源库之前,请确保安装目录中的modelsim.ini是“只读”。这将防止将资源库永久映射到modelsim.ini文件中。

3.1 为资源库创建一个目录

创建一个名为 resource_library 的新目录,把counter.v文件复制到这个目录下。

3.2 为 test bench 创建一个目录

创建一个名为 testbench 的新目录,该目录用来保存test bench和项目文件。把 tcounter.v 复制到这个目录下。

在本文中我们创建了两个目录,以模拟从第三方接收资源库的情况。如前所述,我们将链接到第一个目录中的资源库。

3.3 打开modelsim 并把目录设置到 resource_library。

3.4 创建资源库

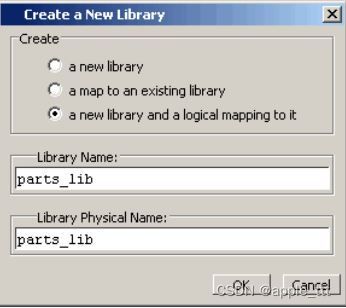

选择 File > New > Library ,设置如下:

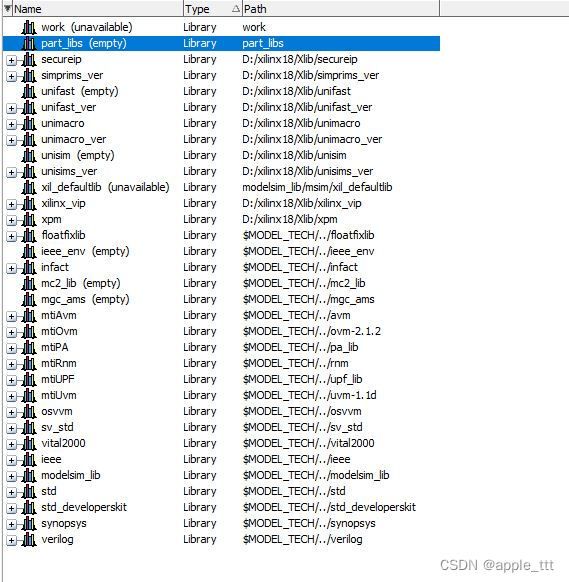

单击“确定”后,ModelSim将为库创建一个目录,在库窗口中列出它,并修改modelsim.ini文件以将来记录这个新库。

3.5 将 counter.v 编译到资源库中

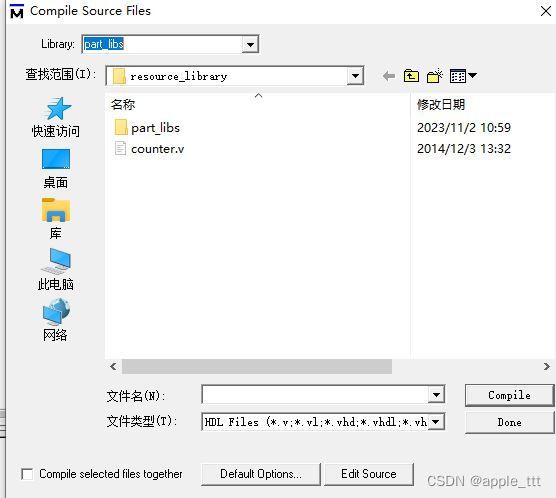

点击编译按键:

![]()

从库的列表中选择parts_lib库

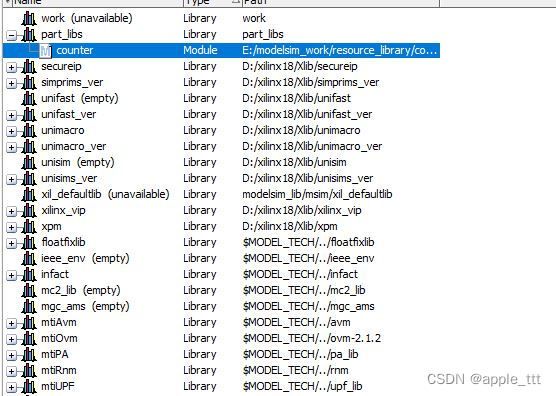

选择counter.v文件进行编译,选中后点击compile,完成后点击Done。

3.6 将目录切换到testcounter

四、创建项目(Creating the Project)

现在我们将创建一个包含有 tcounter.v 的项目

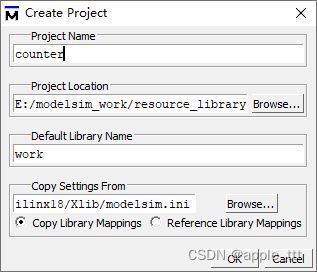

1、创建项目:File > New > Project,项目名称设置为counter,请确保选择了“Copy Library Mappings”。将使用默认的modelsim.ini文件,点击OK。

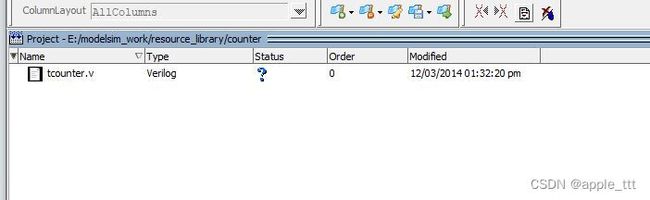

2、 把 test bench 加载到项目中,点击 Add Existing File ,添加后结果如下:

3、编译test bench

五、没有链接库的情况( Loading Without Linking Libraries)

要想实现本文的最终目标,我们需要链接到自己创建的资源库,我们会在后面的部分实现这一目标,但是现在我们先来试一下不链接到库的情况。这里我们以verilog的情况为例展开。

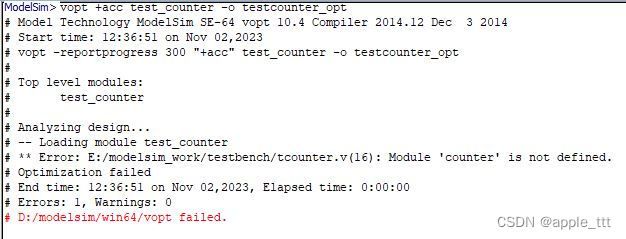

我们通过 vpot 命令进行优化:

vopt +acc test_counter -o testcounter_opt得到了如下的结果,显示counter模块未定义。

我们输入 quit -sim 以退出仿真。

六、链接到资源库(Linking to the Resource Library)

链接到资源库需要你在调用仿真器时指定一个“搜索库”。

1、在主界面点击仿真按键

![]()

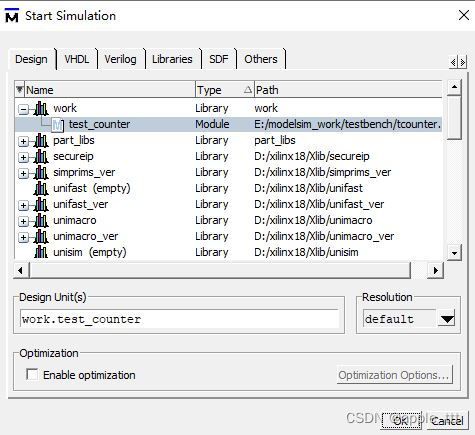

2、单击工作库旁边的“+”图标,选择test_cecter,选择不优化

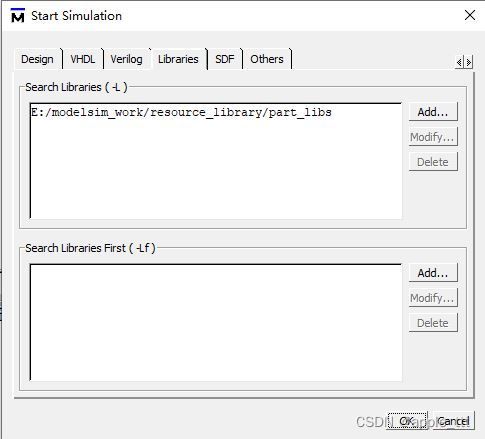

3、选择libraries,点击add > browse找到part_libs目录,进行添加,结果如下:

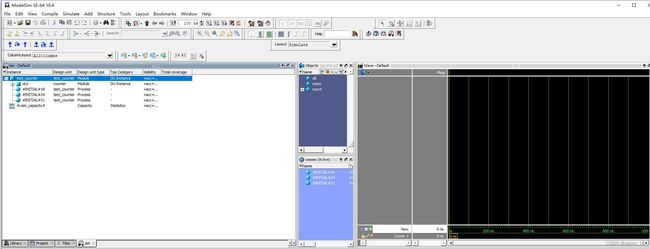

4、点击OK。最终结果如下:

至此我们就可以正常进行仿真分析了。