ZYNQ核心板设计和引脚关系

背景

无论是zynq,还是FPGA,它们的引脚映射都让人眼花缭乱。比如前期在学习zynq时,我硬是不理解EMIO与实际引脚的关系是什么,从而让我觉得苦恼。同时我个人在学习时,总是偏好于先理解低层硬件。如果最小系统板不清楚,总会在内心产生一种朦胧感。所以我决定至少能够基本了解zynq的最小系统板是怎么设计的。

最小系统板构成

首先好奇为啥最小系统板子都要有一个EMMC、QSPI FLAHS和DDR等。简单理解就是EMMC的存储空间比较大,一般核心板子为8G,可以用于存储操作系统和多媒体资源;毕竟几个文件和视频图像就可能几个G了。DDR主要就是运行程序了。QSPI FLASH则用于存储运行程序,所以256M的存储基本能够满足要求。

BANK500

为了更好理解ZYNQ的引脚特点,从BANK500入手,理解相关的应用。

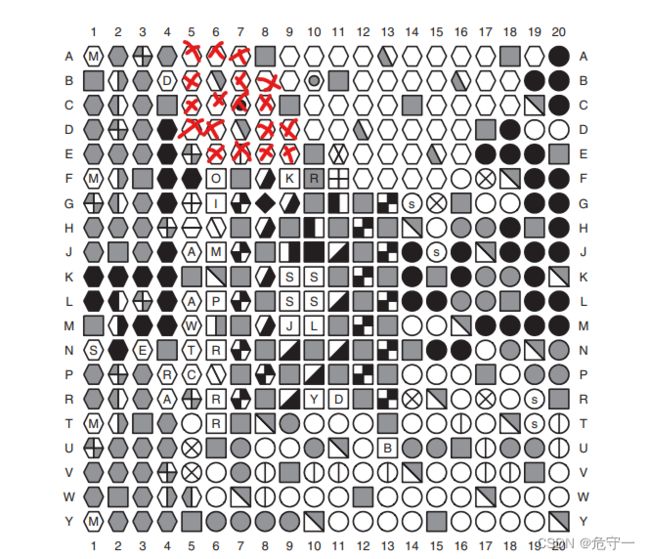

引脚输出图

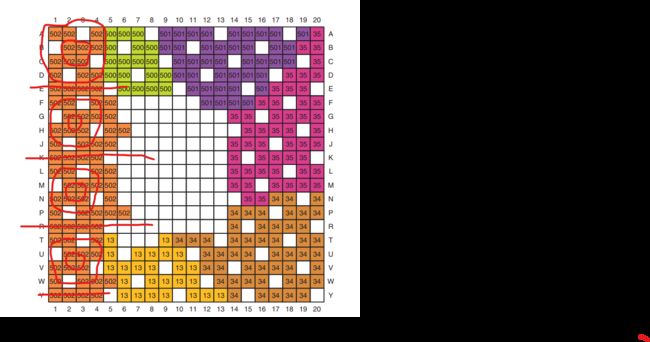

BANK分配图

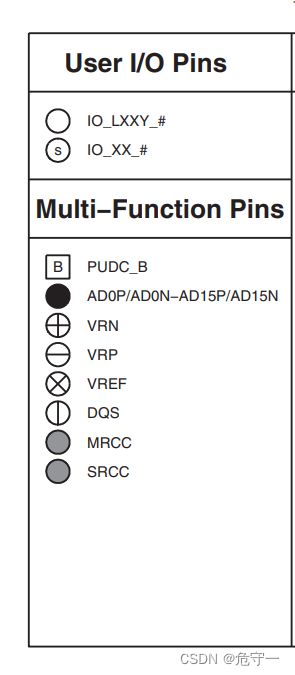

这是zynq的引脚输出图,引脚类型比较多,让人眼花缭乱。为了更好聚焦,我们看看BANK分配图。

引脚输出图标记BANK500

顿时感觉清晰多了。但是两个图的对象比较多,两者的重叠区域比较容易混淆,所以把两个图合并起来看。可以看出主要由16个纯色的六边形、一个黑色圆门边形和一个竖线六边形构成。

BANK500引脚分配表

从下表可以看出,18个引脚中16个为MIO引脚,一个为时钟引脚,一个为重置引脚。其中不包含包含在500BANK里面的两个斜切的半阴影六边形则是VCCO_MIO0。如此可以看出MIO作为PS嵌入式端的引脚,BANK时包含了其16个引脚,其中还有时钟、电源和重置相关的引脚。

PS_CLK_500 NA 500 NA NA MIO NA

C7 PS_POR_B_500 NA 500 NA NA MIO NA

C8 PS_MIO15_500 NA 500 NA NA MIO NA

C5 PS_MIO14_500 NA 500 NA NA MIO NA

E8 PS_MIO13_500 NA 500 NA NA MIO NA

D9 PS_MIO12_500 NA 500 NA NA MIO NA

C6 PS_MIO11_500 NA 500 NA NA MIO NA

E9 PS_MIO10_500 NA 500 NA NA MIO NA

B5 PS_MIO9_500 NA 500 NA NA MIO NA

D5 PS_MIO8_500 NA 500 NA NA MIO NA

D8 PS_MIO7_500 NA 500 NA NA MIO NA

A5 PS_MIO6_500 NA 500 NA NA MIO NA

A6 PS_MIO5_500 NA 500 NA NA MIO NA

B7 PS_MIO4_500 NA 500 NA NA MIO NA

D6 PS_MIO3_500 NA 500 NA NA MIO NA

B8 PS_MIO2_500 NA 500 NA NA MIO NA

A7 PS_MIO1_500 NA 500 NA NA MIO NA

E6 PS_MIO0_500 NA 500 NA NA MIO NA

正点原子BANK500设计图

从正点原子的ZYNQ核心板原理图可以看出,确实符合前面的理解。其引脚主要用于QSPI和和串口。

最小系统板PCB

为了更好理解这种引脚分配的特点,从PCB的元器件空间分配的角度来切入。我们看到QSPI、晶振、重置KEY等处于ZYNQ的上面,这正好是BANK500的物理地方。左边是DDR,是BANK 502的物理位置。前面的上下分别是BTB板对板接口,位置刚好是MIO的BANK500和USER IO PIN的BANK34所处物理位置。

BANK501

在BANK500基础上,我们再逐步理解BANK501的结构特点。基本识别的顺序一样。

引脚输出图+标记BANK501

引脚分配表

E14 PS_MIO17_501 NA 501 NA NA MIO NA

D10 PS_MIO19_501 NA 501 NA NA MIO NA

F14 PS_MIO21_501 NA 501 NA NA MIO NA

D11 PS_MIO23_501 NA 501 NA NA MIO NA

F15 PS_MIO25_501 NA 501 NA NA MIO NA

D13 PS_MIO27_501 NA 501 NA NA MIO NA

C13 PS_MIO29_501 NA 501 NA NA MIO NA

E16 PS_MIO31_501 NA 501 NA NA MIO NA

D15 PS_MIO33_501 NA 501 NA NA MIO NA

F12 PS_MIO35_501 NA 501 NA NA MIO NA

E13 PS_MIO38_501 NA 501 NA NA MIO NA

D14 PS_MIO40_501 NA 501 NA NA MIO NA

E12 PS_MIO42_501 NA 501 NA NA MIO NA

F13 PS_MIO44_501 NA 501 NA NA MIO NA

D16 PS_MIO46_501 NA 501 NA NA MIO NA

B12 PS_MIO48_501 NA 501 NA NA MIO NA

B13 PS_MIO50_501 NA 501 NA NA MIO NA

C10 PS_MIO52_501 NA 501 NA NA MIO NA

B10 PS_SRST_B_501 NA 501 NA NA MIO NA

A19 PS_MIO16_501 NA 501 NA NA MIO NA

B18 PS_MIO18_501 NA 501 NA NA MIO NA

A17 PS_MIO20_501 NA 501 NA NA MIO NA

B17 PS_MIO22_501 NA 501 NA NA MIO NA

A16 PS_MIO24_501 NA 501 NA NA MIO NA

A15 PS_MIO26_501 NA 501 NA NA MIO NA

C16 PS_MIO28_501 NA 501 NA NA MIO NA

C15 PS_MIO30_501 NA 501 NA NA MIO NA

A14 PS_MIO32_501 NA 501 NA NA MIO NA

A12 PS_MIO34_501 NA 501 NA NA MIO NA

A11 PS_MIO36_501 NA 501 NA NA MIO NA

A10 PS_MIO37_501 NA 501 NA NA MIO NA

C18 PS_MIO39_501 NA 501 NA NA MIO NA

C17 PS_MIO41_501 NA 501 NA NA MIO NA

A9 PS_MIO43_501 NA 501 NA NA MIO NA

B15 PS_MIO45_501 NA 501 NA NA MIO NA

B14 PS_MIO47_501 NA 501 NA NA MIO NA

C12 PS_MIO49_501 NA 501 NA NA MIO NA

B9 PS_MIO51_501 NA 501 NA NA MIO NA

C11 PS_MIO53_501 NA 501 NA NA MIO NA

此外可以在引脚分配表页面使用【ctrl+f】,可以获得BANK501有多少个引脚。

从正点原子的PCB原理图可以看出,BANK501主要用于以太网、OTG、SD、MMC等接口。其中ETH-PHY就处于最小系统板的右端,可以映证BANK501的位置信息。

电源-地放置图

新的发现是,可以结合电源-地的图和IO BANK图,比较快速知道这个区域的引脚分布。如图,就能知道,BANK500中,两个电源、两个地;BANK1中四个电源、四个地。

BANK503

BANK503主要是用于连接DDR,引脚分布具有明显的规律性。先看下图的PINOUT图。左边的橙色方块按照【风车】图案和四个连续橙色方块组成长条交替组合;除此之外,第二重复块包含侧边的【亠】形组合,第三重复块包含【L】形组合,第四重复块包含一个橙色方块。

电源分配也具有类似的规律,分配图如下。两个角度观察:1从斜向角度可知,颜色是按照紫黑-绿-紫黑-绿来排布的;2按照【风车】构型,对向角是同色,交替转换。

引脚分配表显示BANK502相关的引脚85个,考虑电源引脚10,以及BANK501显示的橙色方块75个【16*4+10+1】,所以是符合的。

| 引脚 | 功能 |

|---|---|

| DQ[0,31] | |

| DQS_P,DQS_N,DM | |

| BA,CS_B,CAS_B,RAS_B,WE_B | |

| A[0,14] | |

| CKE,CKP,CKN | |

| DRST_B,VRN,VRP,ODT |

BANK34

BANK34的褐色方块分布没有特定规律,于是通过之间的【风车】有意创造一种规律,增强记忆。56个引脚中,24组差分线+两个单端线+六个电源,一共56个相关引脚。

BANK34主要与ZYNQ的PL部分有关,引脚名主要为IO_LXXY_T#_#的形式。

| 代码 | 含义 |

|---|---|

| L | 差分线 |

| XX | 唯一的命名数字 |

| Y | 差分线的P和N |

| T | 内存字节组【有必要可查】 |

| # | BANK区域 |

BANK35

BANK35与BANK34的引脚数和引脚类型相似,不同之外在于BANK35中包含大量AD信号,BANK34中有比较多的MRCC和SRCC。

BANK31

从BANK31的引脚分配图可以看出,这部分引脚也采用BANK34和BANK35一样的命名模式,但是BANK31是从11开始的,而非1开始计数。从右边的【NO CONNECT】的7Z010可以看出这部分引脚是跟其它芯片有关联,可能是引脚相同。

BANK0

BANK分配图中并没有BANK0,但是引脚分配表中列举出了BANK0相关的引脚。一共二十个引脚,基本是PINOUT图中的delicate pin。但是内容太多,让人有些目不睱接。

Pin Pin Name Memory Byte Group Bank VCCAUX Group Super Logic Region I/O Type No-Connect

R11 DONE_0 NA 0 NA NA CONFIG NA

M9 DXP_0 NA 0 NA NA CONFIG NA

J10 GNDADC_0 NA 0 NA NA CONFIG NA

J9 VCCADC_0 NA 0 NA NA CONFIG NA

L9 VREFP_0 NA 0 NA NA CONFIG NA

L10 VN_0 NA 0 NA NA CONFIG NA

F11 VCCBATT_0 NA 0 NA NA CONFIG NA

F9 TCK_0 NA 0 NA NA CONFIG NA

M10 DXN_0 NA 0 NA NA CONFIG NA

K10 VREFN_0 NA 0 NA NA CONFIG NA

K9 VP_0 NA 0 NA NA CONFIG NA

F10 RSVDGND NA 0 NA NA CONFIG NA

N6 RSVDVCC3 NA 0 NA NA CONFIG NA

R6 RSVDVCC2 NA 0 NA NA CONFIG NA

R10 INIT_B_0 NA 0 NA NA CONFIG NA

G6 TDI_0 NA 0 NA NA CONFIG NA

F6 TDO_0 NA 0 NA NA CONFIG NA

T6 RSVDVCC1 NA 0 NA NA CONFIG NA

M6 CFGBVS_0 NA 0 NA NA CONFIG NA

L6 PROGRAM_B_0 NA 0 NA NA CONFIG NA

J6 TMS_0 NA 0 NA NA CONFIG NA

UG865

引脚映射文件