【csapp】Task 06:存储器层次结构

存储技术

存储器系统 memory system

是一个具有不同容量、成本和访问时间的存储设备的层次结构。

存储器的层次结构

| 寄存器 | CPU寄存器保存最常用的数据 | 快 | 0个周期 |

| 高速缓存存储器 cache memory |

作为主存储器中的数据和指令的缓冲区域 | 4-75个周期 | |

| 主存储器 main memory |

作为磁盘的缓冲区域 | 相对慢速 | 百+个周期 |

| 磁盘 | 作为通过网络中其他机器上数据的缓冲区域 | 容量大、速度慢 | 千万+周期 |

| 远程设备中的存储器 | 慢 |

计算机程序的一个基本而持久的思想:如果你理解了系统是如何将数据在存储器层次结构中上上下下移动的,那么你可以编写自己的程序,使它的数据项存储在层次结构中较高的地方,这样CPU可以快速访问到它们。

访问主存

数据流通过称为总线(bus)的共享电子电路在处理器和DRAM主存之间来来回回。

每次CPU和主存之间的数据传送都是通过一系列步骤来完成的,这些步骤称为总线事物(bus transaction)

- 读事物(read transaction)从主存传送数据到CPU

- 写事物(write transaction)从CPU传送数据到主存

总线是一组并行的导线,能携带地址、数据和控制信号。取决于总线的设计,数据和地址信号可以共享同一组导线,也可以使用不同的。同时,两个以上的设备也能共享同一个总线。

locality 局部性

具有良好局部性的程序倾向于一次又一次地访问相同的数据项集合,或是倾向于访问邻近的数据项集合。具有良好局部性的程序比局部性差的程序更多地倾向于从存储器层次结构中较高层次处访问数据项。

基本的存储技术

RAM 存储器(Random-Access Memory, RAM)

静态RAM(SRAM)更快,更贵,

- 常用来作为高速缓存存储器

- 一个桌面系统的SRAM不会超过几兆字节

- 可以在CPU芯片上,也可以在片外

- SRAM将每个位存储在一个双稳态的bistable存储器单元里。每个单元是用一个六晶体管电路来实现的。这个电路有一个属性:它可以无限期地保持在两个不同的电压配置configuration或状态state中。

- 由于SRAM存储器单元的双稳态特性,只要有电,它就会永远地保持它的值。即使有干扰(e.g. 电子噪音)来扰乱电压,当干扰消除时,电路就会恢复到稳定值

动态RAM(DRAM)

- 常用来作为主存以及图形系统的帧缓冲区

- 可以拥有几百-几千兆字节

- DRAM将每个位存储为对一个电容的充电。这个电容非常小,通常只有大约30毫微微法拉(femtofarad)

- DRAM存储器可以制造得非常密集-每个单元由一个电容和一个访问晶体管组成。

- DRAM对干扰非常敏感,当电容的电压被扰乱之后,它就永远不会恢复了。暴露在光线下会导致电容电压改变(实际上,数码照相机和摄影机中的传感器本质上就是DRAM单元的阵列)

ROM 存储器(Read-Only Memory)只读存储器

ROM是以它们能够被重编程(写)的次数和对它们进行重编程所用的机制来区分的

PROM(Programmable ROM)可编程ROM只能被编程一次

- 每个存储器单元有一种熔丝(fuse),只能用高电流熔断一次

可擦写可编程 EPROM(Erasable Programmable ROM)

- 有一个透明的石英窗口,允许光达到存储单元

- 紫外线光照射过窗口,EPROM单元就被清除为0

- 对EPROM编程是通过使用一种把1写入EPROM的特殊设备来完成的

- EPROM能够被擦除和重编程的1000次

电子可擦除 EEPROM(Electrically Erasable PROM)

- 类似EPROM,但它不需要一个物理上独立的编程设备,因此可以直接在印制电路卡上编程

- EEPROM 能够被编程 10**5次

闪存 Flask Memory

- 一类非易易失性存储器,基于RRPROM

- 位大量电子设备提供快速而持久的非易失性存储

- SSD就是基于闪存的磁盘驱动器

存储在ROM设备中的程序通常被称为固件(firmware)。当一个计算机系统通电以后,它会运行存储在ROM中的固件。一些系统在固件中提供了少量基本的输入和输出函数

旋转硬盘(rotating disk/disk drive)

从磁盘上读信息的时间为毫秒级,比从DRAM读慢10万倍,比SRAM读慢100万倍

磁盘构造

-

磁盘有盘片(platter)构成。每个盘片有两面或者称为表面(surface),表面覆盖着磁性记录材料。磁盘通常包含一个/多个这样的盘片,并封装在一个密封的容器中。

-

盘片中央有个可以旋转的主轴(spindler),它使盘片以固定的旋转速率(rotational rate)旋转,通常是5.4K-15K转每分钟(Revolution Per Minute, RPM)。

-

每个surface是由一组称为磁道(track)的同心圆组成的。每个track被划分为一组扇区(sector)

每个sector包含相等数量的数据位(通常是512bytes) -

sector之间由一些间隙(gap)分隔开,这些gap中不存储数据位。gap存储用来标识sector的格式化位

-

柱面(cylinder)用来描述多个盘片驱动器的构造,柱面是所有盘片表面上到主轴中心的距离相等的track的集合。

磁盘容量

磁盘容量是由这些技术因素决定的:

- 记录密度(recording density)位/英寸

- track一英寸的段中可以放入的位数

- 磁道密度(track density)道/英寸

- 从盘片(platter)中心出发半径上一英寸的端内可以有的track数

- 面密度(areal density)位/平方英寸

- 记录密度 * 磁道密度

磁盘容量公式:

磁盘容量=(字节数/扇区)*(平均扇区数/track)*(track数/surface)*(surface数/platter)*(platter数/磁盘)练习题6.2 计算这样一个磁盘的容量,它有2个盘片,10,000个柱面,每条track平均有400个sector,每个sector有512字节

磁盘操作

磁盘用读/写头(read/write head)来读写存储在磁性表面的位,而读写头连接到一个传动臂(actuator arm)一端。

寻道(seek):通过沿着半径轴前后移动这个传动臂,驱动器可以将读/写头定位在盘面上的任何track上。一旦读/写头定位到了期望的track上,那么当track上的每个位通过它的下面时,读/写头可以感知到这个位的值(读该位),也可以修改这个位的值(写该位)。

有多个盘片的磁盘针对每个盘面都有一个独立的读/写头。

- 读/写头

- 垂直排列,一致行动。在任何时刻,所有的读/写头都位于同一个柱面上。

- 盘面上一粒微小的灰尘都像一块巨石。如果读写头碰到了这样的一块巨石,读写头会停下来,撞到盘面–读/写头冲撞(head crush)

磁盘以扇区大小的块来读写数据,对扇区的访问时间(access time)有三个主要的部分

- 寻道时间(seek time)

- 为了读取某个目标扇区的内容,传动臂首先将读写头定位到包含目标扇区的track上。

- 移动传动臂所需时间叫 seek time

- 一次寻道的最大时间 T m a x s e e k Tmax seek Tmaxseek可以高达20ms

- 旋转时间(rotational latency)

- 一旦读写头定位到了期望的track,驱动器等待目标扇区的第一个位旋转到读写头下。

- 这个步骤的性能依赖于当读写头到达目标扇区时盘面的位置以及磁盘的旋转速度。

- 最快的情况:头刚刚错过目标扇区,又要重新转一整圈

- 传送时间(transfer time)

- 当目标扇区的第一个位位于读写头下时,驱动器就可以开始读或者写该扇区的内容了。

- 一个扇区的传送时间依赖于旋转速度和每条track的扇区数目

逻辑磁盘块

磁盘控制器 - 磁盘封装中一个小的硬件/固件设备,维护逻辑块号和实际(物理)磁盘扇区之间的映射关系。(一个B个山区大小的逻辑块的序列,编号为0…B-1)

当操作系统想要执行一个I/O操作时,操作系统会法送一个命令到磁盘控制器,让它读/写某个逻辑块号。

e.g. 读一个磁盘扇区的数据到主存

控制器上的固件执行一个快速表查找,将一个个逻辑块号翻译成一个[盘面、track、扇面]的三元组,这个三元组唯一地标识了对应的物理扇区。控制器上的硬件会解释这个三元组,将读/写头移动到适当的柱面,等待扇区移动到读写头下,将读写头感知到的位放到控制器上的一个小缓冲区中,

将位复制到主存中。

格式化的磁盘容量

磁盘控制器必须对磁盘进行格式化,然后才能在磁盘上存储数据。

格式化包括:

- 用标识扇区的信息填写扇区之间的间隙,

- 标识出表面有故障的柱面并且不使用它们

- 在每个区中预留出一组柱面作为备用(如果区中一个柱面在磁盘使用过程中坏掉,会用这些备用柱面)

因为存在备用柱面,所以磁盘制造商所说的格式化容量比最大容量要小。

连接I/O设备

输入/输出(I/O)设备,都是通过I/O总线,例如intel的外围设备互联(Peripheral Component Interconnect,PCI)总线连接到CPU和主存的。

PCIe

PCI模型中,系统中所有的设备共享总线,一个时刻只能有一台设备访问这些线路

PCIe(PCI express)- 一组高速串行、通过开关连接的点到点链路最大吞吐率:PCIe 16GB/s,PCI 533MB/s

系统总线和内存总线是和CPU有关的,但PCI这样的I/O总线是与底层CPU无关。

虽然I/O总线比系统总线&内存总线慢,但是它可以容纳种类繁多的第三方I/O设备,如:

- 通用串行总线(Universal Serial Bus,USB)

- 连接到USB总线的设备的中转机构

- 图形卡/适配器

- 包含硬件和软件逻辑,复制代表CPU在显示器上画像素

- 主机总线适配器

- 将一个/多个磁盘连接到I/O总线

- 使用的是一个特别的主机总线接口定义的通信协议

- 网络适配器

- 通过将适配器插入到主板上空的扩展槽中,从而连接到I/O总线。(扩展槽提供了到总线的直接电路连接)

访问磁盘

CPU从磁盘读取数据时发生的步骤

1、CPU通过将命令、逻辑块号、目的内存地址写到与磁盘相关联的内存映射地址,发起一个磁盘读

2、磁盘控制器读扇区,并执行到主存的DMA传送

3、当DMA传送完成后,磁盘控制器用中断的方式通知CPU

固态硬盘

Solid State Disk - 一种基于闪存的存储技术,用于处理来自CPU的读写逻辑磁盘块的请求。

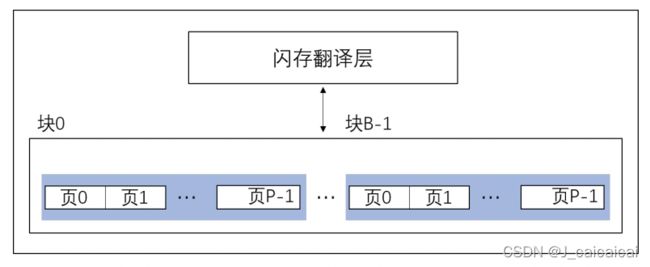

一个SSD封装由一个/多个闪存芯片和闪存翻译层(flash translation layer)组成:

- 闪存芯片替代传统旋转磁盘中的机械驱动器

- 闪存翻译层是一个硬件/固件设备,~磁盘控制器的角色,对逻辑块的请求翻译成对底层物理设备的访问。

举个栗子

一个闪存由B个块的序列组成

每个块由P页组成

----/-----

数据以页为单位读写

只有在一页所属的块整个被擦除之后,才能写这一页(通常指这块中所有位都被设置为1)

一旦一个块被擦除,块中每个页都可以不需要再进行擦除就写一次。

在进行~100,000次重复写之后,块就会磨损坏。

一旦一个快磨损,就不能再使用了。

随机写慢,原因:

1、擦除块需要相对较长时间,1ms级

2、如果写操作试图修改一个包含已有数据的页p,那么这个块中所有带有数据的页都必须被复制到一个新块,然后才能对对页p进行写。(制造商有做过优化了,但总的来说还是不可能像随机读一样快)