lv11 嵌入式开发 ARM体系结构理论基础2

目录

1 ARM概述

1.1 处理器分类

1.2 SOC概念

2 ARM指令集概述

2.1 ARM指令集

2.2 编译原理

3 ARM存储模型

3.1 ARM数据类型

3.2 字节序

3.3 ARM指令存储

4 ARM工作模式

4.1 ARM工作模式分类

1 ARM概述

ARM的含义

ARM(Advanced RISC Machines)有三种含义 一个公司的名称、一类处理器的通称、一种技术

ARM公司

- > 成立于1990年11月,前身为Acorn计算机公司

- > 主要设计ARM系列RISC处理器内核

- > 授权ARM内核给生产和销售半导体的合作伙伴,ARM公司并不生产芯片

- > 提供基于ARM架构的开发设计技术软件工具、评估板、调试工具、应用软件 总线架构、外围设备单元等

ARM产品系列

先经典处理器 包括ARM7、ARM9、ARM11家族

Cortex-A系列

针对开放式操作系统的高性能处理器 应用于智能手机、数字电视、智能本等高端运用

Cortex-R系列

针对实时系统、满足实时性的控制需求 应于汽车制动系统、动力系统等

Cortex-M系列

为单片机驱动的系统提供了低成本优化方案 应用于传统的微控制器市场、智能传感器、汽车周边等

1.1 处理器分类

RISC处理器

只保留常用的的简单指令,硬件结构简单,复杂操作一般通过简单指令的组合实现,一般指令长度固定,且多为单周期指令(只保留简单电路)

RISC处理器在功耗、体积、价格等方面有很大优势,所以在嵌入式移动终端领域应用极为广泛

CISC处理器

不仅包含了常用指令,还包含了很多不常用的特殊指令,硬件结构复杂,指令条数较多,一般指令长度和周期都不固定

CISC处理器在性能上有很大优势,多用于PC及服务器等领域

1.2 SOC概念

soc arm基础上增加很多外围电路,如wifi、usb、ram、rom

SOC(System on Chip) 即片上系统,将一个系统中所需要的全部部件集成在一个芯片中在体积、功耗、价格上有很大优势

2 ARM指令集概述

指令

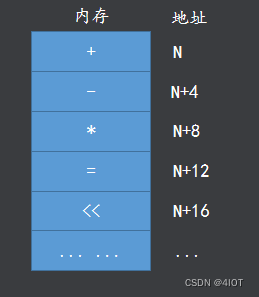

能够指示处理器执行某种运算的命令称为指令(如加、减、乘 ...)

指令在内存中以机器码(二进制)的方式存在

每一条指令都对应一条汇编 (1条C语言对应n条指令3*3 3+3+3)

程序是指令的有序集合

指令集

处理器能识别的指令的集合称为指令集

不同架构的处理器指令集不同

指令集是处理器对开发者提供的接口

2.1 ARM指令集

大多数ARM处理器都支持两种指令集:

ARM指令集

所有指令(机器码)都占用32bit存储空间

代码灵活度高、简化了解码复杂度

执行ARM指令集时PC值每次自增4

Thumb指令集

所有指令(机器码)都占用16bit存储空间

代码密度高、节省存储空间

执行Thumb指令集时PC值每次自增2

Thumb指令16位,有很多限制,光Thumb无法满足,所以用得比较少。

2.2 编译原理

机器码(二进制)是处理器能直接识别的语言,不同的机器码代表不同的运算指令,处理器能够识别哪些机器码是由处理器的硬件设计所决定的,不同的处理器机器码不同,所以机器码不可移植.二进制机器码查错很困难,不可读

汇编语言是机器码的符号化,即汇编就是用一个符号来代替一条机器码,所以不同的处理器汇编也不一样,即汇编语言也不可移植

C语言在编译时我们可以使用不同的编译器将C源码编译成不同架构处理器的汇编,所以C语言可以移植

3 ARM存储模型

3.1 ARM数据类型

ARM采用32位架构,基本数据类型有以下三种

Byte 8bits

Halfword 16bits

Word 32bits

数据存储

Word型数据在内存的起始地址必须是4的整数倍

Halfword型数据在内存的起始地址必须是2的整数倍

注:即数据本身是多少位在内存存储时就应该多少位对齐,如不按要求存储会出问题

3.2 字节序

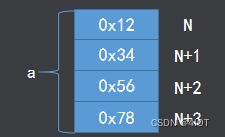

大端对齐

低地址存放高位,高地址存放低位 a = 0x12345678;

小端对齐

低地址存放低位,高地址存放高位 a = 0x12345678;

注:ARM一般使用小端对齐

一个错误理解:

大端对齐即数组a[0]存低地址,小端对齐即数组a[0]存高地址

正确理解:

实际数组a[0]不管大端还是小端模式,都是存在低地址,单字节不存在大端小端,永远存在低地址。只有4字节int,需要注意低地址是存放高位还是地位。

ubuntu是小端,可以写一个小程序测试

uint32_t val32 = 0x11223344;

uint8_t val8 = *( (uint8_t *)&val32 );

if(val8 == 0x44)

printf("本机是小端字节序\n");

else

printf("本机是大端字节序\n");3.3 ARM指令存储

处理器处于ARM状态时

所有指令在内存的起始地址必须是4的整数倍 PC值由其[31:2]决定,[1:0]位未定义

地址必须是4的整数倍

处理器处于Thumb状态时

所有指令在内存的起始地址必须是2的整数倍 PC值由其[31:1]决定,[0]位未定义

注:即指令本身时多少位在内存存储时就应该多少位对齐。

原因:

例:地址必须是4个整数倍时

100U 4

1000U 8

1100U 12

最后两位永远是0,PC值也必须是4的整数倍,最低两位一定是0

但是PC值可以改,如果改为7 111,[1:0]会强制转换为0 变为100

4 ARM工作模式

ARM有8个基本的工作模式

- User 非特权模式,一般在执行上层的应用程序时ARM处于该模式

- FIQ 当一个高优先级中断产生后ARM将进入这种模式

- IRQ 当一个低优先级中断产生后ARM将进入这种模式

- SVC 当复位或执行软中断指令后ARM将进入这种模式 (软中断)

- Abort 当产生存取异常时ARM将进入这种模式

- Undef 当执行未定义的指令时ARM将进入这种模式

- System 使用和User模式相同寄存器集的特权模式

- Monitor 为了安全而扩展出的用于执行安全监控代码的模式

工作模式的理解

- 不同模式拥有不同权限

- 不同模式执行不同代码

- 不同模式完成不同的功能

4.1 ARM工作模式分类

按照权限

User为非特权模式(权限较低),其余模式均为特权模式(权限较高)

按照状态

FIQ、IRQ、SVC、Abort、Undef属于异常模式,即当处理器遇到异常后 会进入对应的模式

注意理解:

操作系统有自己的模式

用户态:如应用程序一般都在用户态运行

内核态:如kernal,调用线程等

ARM也有自己的工作模式区分开

User为非特权模式(权限较低),其余模式均为特权模式

FIQ、IRQ、SVC、Abort、Undef属于异常模式,即当处理器遇到异常后 会进入对应的模式