计算机组成原理习题-4

前言:

本文首先回答了几个计算机基础知识问题,包括CDRAM和猝发式读取、总线仲裁方式、机器指令与微指令的关系以及CPU的基本功能等。然后给出了一道关于CPU地址总线设计的题,需要计算存储芯片数量、画出连接图、给出地址范围。最后又回答了两个关于中断、快表的题目,涉及中断屏蔽位设置、快表地址转换过程等,答案来自网络搜集和ChatGPT,可能不完全正确

一、回答下列问题

1.什么是CDRAM?什么是猝发式读取?

CDRAM是一种存储器技术,全称为"Cache Dynamic Random Access Memory",即缓存动态随机访问存储器。它是一种速度非常快且集成度较高的存储器,常用作高速缓存(Cache)。

猝发式读取(Burst Read)是CDRAM的一种读取方式。在猝发式读取模式下,CDRAM能够在一次访问周期内连续读取多个连续地址的数据,并将这些数据存储到内部缓冲区中。这种方式可以提高读取数据的连续性,减少访问延迟,提高数据的传输效率。

2.何为“总线仲裁”?他有几种方式?集中式总线仲裁方式有哪些?各有哪些特点?

总线仲裁(Bus Arbitration)是指多个设备同时请求使用总线进行数据传输时,需要通过某种机制来协调、决定哪个设备可以优先访问总线进行数据传输。

总线仲裁的方式有两种:集中式和分布式。

集中式总线仲裁方式是指有一个专门的仲裁器或者控制器来负责协调总线的访问权限。常见的集中式总线仲裁方式有以下几种:

集中式仲裁使用优先级编码:每个设备被分配一个唯一的优先级编码,仲裁器按照设备的优先级确定总线的访问顺序。设备的优先级可以是固定的,也可以根据设备的特定要求进行设置。

集中式仲裁使用轮询方式:仲裁器按照事先确定的轮询顺序循环地询问每个设备是否需要访问总线。每个设备在轮到它的时候可以请求总线进行数据传输。

集中式仲裁使用请求-确认方式:每个设备通过发送请求信号来请求总线进行数据传输,仲裁器接收到请求信号后发送确认信号给获得访问权的设备,同时阻止其他设备访问总线。获得访问权的设备可以进行数据传输,其他设备则需要等待下一轮的请求。

每种集中式总线仲裁方式都有各自的特点和适用场景。优先级编码适用于设备间有一定的优先级关系,并且优先级需要固定或者可变的情况。轮询方式适用于所有设备的优先级相同,并且希望每个设备都有机会访问总线的情况。请求-确认方式在一定程度上可以提高总线的利用率,但会增加仲裁器的复杂性。

3.说明机器指令和微指令的关系。

答:抽象级别不同。机器指令是由一组二进制代码组成的。微指令是具有微地址的控制字。一系列微指令的有序集合构成微程序。在微程序控制逻辑法中,机器指令由微程序实现。格式不同。机器指令包括操作码和操作数地址码字段,微指令根据编译法的不同有多种情况,一般包括微操作信息和下地址字段.

4.中央处理器的基本功能有哪些?并给以简要说明。

中央处理器(Central Processing Unit,CPU)是计算机系统中的核心部件,主要负责执行计算机程序中的指令,进行各种计算和数据处理操作。它的基本功能包括以下几个方面:

指令解码和执行:CPU根据程序计数器(Program Counter,PC)中的指令地址,逐条获取指令并解码,然后执行相应的操作,包括算术运算、逻辑运算、数据传输等等。

数据存储和管理:CPU通过访问主存储器(Memory)来读取和写入数据。它能够将数据加载到寄存器(Register)中进行操作,并将结果存储回主存储器。

流水线处理:为了提高运算速度,现代CPU通常采用流水线技术。它将指令的执行过程分成多个步骤,在同一时刻可以并行处理多条指令,从而提高吞吐量。

中断处理与异常处理:当发生外部事件(如硬件中断)或内部事件(如除法错误)时,CPU需要暂停当前任务的执行,并对中断或异常进行处理,以确保计算机系统的稳定性和可靠性。

控制和管理系统资源:CPU通过控制总线、地址线和数据线等系统资源,对其他硬件部件进行操作和控制,使计算机系统完成各种任务。

总之,中央处理器的基本功能包括指令解码和执行、数据存储和管理、流水线处理、中断处理与异常处理,以及控制和管理系统资源等。这些功能使得CPU成为计算机系统中的核心,负责执行程序并进行各种计算和数据处理操作。

二、某机的CPU地址总线20根(A19-A0为低位),双向数据总线8根(D7-D0),控制线一条(WE)。目前使用的存储空间为48KB,其中16KB为ROM,拟用8K×8的ROM芯片,32KB为RAM,拟用16K×4位的RAM芯片。

1.需要两种芯片各多少片?

2.画出CPU与主存储器的连线图,其中译码器自定。

3.写出ROM和RAM的地址范围。

解:

(1)依题意

ROM为 16KB,拟采用 8K8 位的 ROM芯片,则需 ROM芯片为 2 片,

进行位扩展。

RAM为 32KB,拟采用 16K4 位的 RAM芯片,则需 RAM芯片为 4 片,进行字位同时扩展。

( 2)画出 CPU与存储器之间的连接图。

CPU — Address Bus (A19-A0) — Decoder — ROM Chip

|

|

Data Bus (D7-D0) — RAM Chip

|

|

Control Line (WE) — RAM Chip

3)写出 ROM和 RAM的地址范围

ROM的地址范围为: 0000H–3FFFH

RAM的地址范围为: 4000H–BFFFH

三、中断屏蔽的作用是什么?若中断屏蔽位“1”表示开放中断,用“0”表示屏蔽断开源,设有4个中断源,其硬件已排定中断响应的次序为P1,P2,P3,P4。问:

1.若中断处理的优先级从高到低依次为P1,P2,P3,P4,则这4个中断屏蔽位应如何设置?

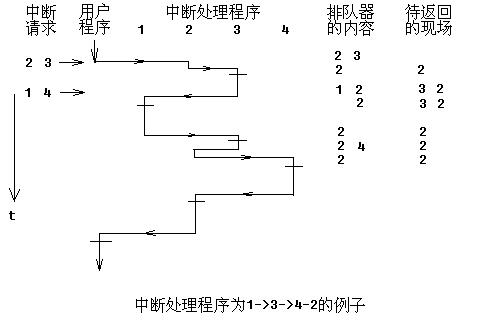

2.要使中断屏蔽处理次序改为P1,P4,P3,P2,则中断屏蔽位应如何设置?如果所有的中断处理器各需3个单位时间,中断响应和返回的时间可忽略,中断屏蔽位的设置和第二问相同。当程序运行主程序时,同时发生第2,3级中断请求,经过2个时间单位后,又同时发生1,4级中断请求,请画出程序运行示意图。

答案

答:

(1)当中断响应优先次序为1→2→3→4时,其中断处理次序为1→3→4→2。

(2)

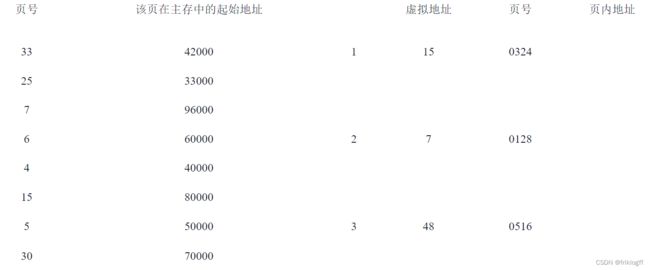

四、右图表示用快表(页表)的虚实地址转换条件,快表放在相连存储器中,其容量为8个存储单元,问:

(1)当CPU按虛地址1去访问主存时主存的实地址是多少?

(2)当CPU按虚地址2去访问主存时主存的实地址是多少?

(3)当CPU按虚地址3去访问主存时主存的实地址是多少?

答案

解:(1)用虚拟地址为1的页号15作为快表检索项,查得页号为15的页在主存中的起始地址为80000,故将80000与虚拟地址中的页内地址码0324相加,求得主存实地址码为80324。

(2)主存实地址码 = 96000 + 0128 = 96128

(3)虚拟地址3的页号为48,当用48作检索项在快表中检索时,没有检索到页号为48的页面,此时操作系统暂停用户作业程序的执行,转去执行查页表程序。如该页面在主存中,则将该页号及该页在主存中的起始地址写入主存;如该页面不存在,则操作系统要将该页面从外存调入主存,然后将页号及其在主存中的起始地址写入快表。

总结

通过回答这些计算机基础知识题目,巩固了CDRAM、总线仲裁、中断处理、虚拟存储等概念,练习了地址转换、中断优先级设置、存储器地址分配等问题解决能力。这对进一步深入学习计算机原理与体系结构提供了基础。