Verilog学习笔记1——关键词、运算符、数据类型、function/task、initial/always、generate、抽象级别

文章目录

- 前言

- 一、关键词

- 二、运算符

-

- 1、算术运算符* / % + -

- 2、移位运算符<< <<< >> >>>

- 3、关系运算符<= < >= >

- 4、相等运算符== === !== !=

- 5、位运算符& |

- 6、逻辑运算符&& || !

- 7、拼接运算符

- 总结——举例计算

- 三、数据类型

-

- 1、基本类型:reg、wire、integer、parameter

- 2、位宽扩展

- 四、条件语句

- 五、循环语句

-

- 1、for

- 2、generate

- 六、function和task

- 七、initial和always

-

- 1、initial和always相同点和区别

- 2、always和assign语句区别

- 八、模块例化

- 九、verilog抽象级别

前言

2023.4.4

2023.4.7 补充综合和不可综合的关键词

2023.8.13 更新运算符内容

一、关键词

module/endmodule

input/output/inout

parameter

wire/reg

always/assign

begin/end

posedge/negedge

case/default/endcase

if/esle

for

二、运算符

位运算符和缩位运算符区别:缩位运算符结果为1bit,位运算符结果位数和操作数位数相同

1、算术运算符* / % + -

%:取模,求余数

2、移位运算符<< <<< >> >>>

移位运算符:分为逻辑移位和算术移位(很重要!!!)

- 逻辑运算<< >>:右移补0,左移补0

- 算术运算<<< >>>:左移补0,右移补最高位(补0或者1由左操作数的有无符号决定)

reg类型变量默认情况下是无符号类型的

表达式中只要有一个无符号数,所有的数都被当做无符号数进行计算;只有全部为有符号数时才按照有符号数计算。

因此移位的时候要特别关注每个变量是否有无符号,不仅是看左操作数的有无符号。

3、关系运算符<= < >= >

关系运算符<=:每一个关系运算符优先级相同,且如果包含x或z,那么结果为1’bx

4、相等运算符== === !== !=

在使用==的时候如果只要包含x或z,那么等于的比较结果肯定为x

===:必须每一bit都完全相等

5、位运算符& |

6、逻辑运算符&& || !

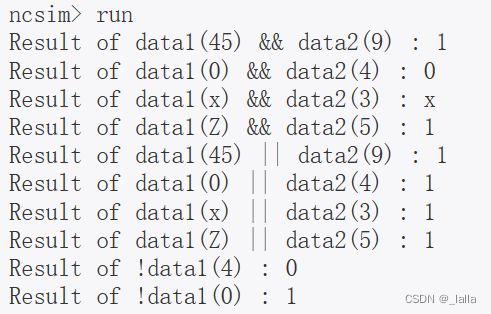

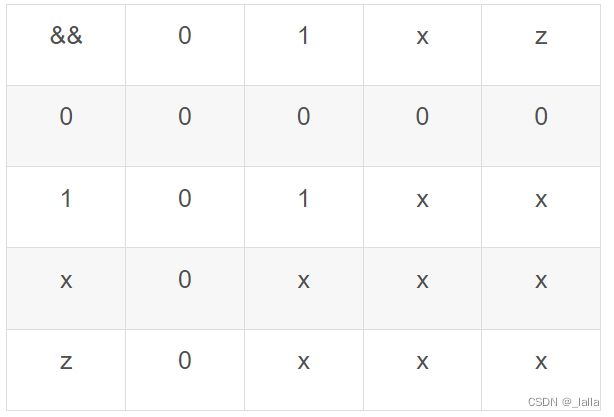

逻辑运算符&&:左右两边均不为0,&&输出为1’b1,~是把1变0,0变1。如果有x和z,输出仍有x

逻辑运算符||:只要有一边操作数为1,输出为1

7、拼接运算符

{ }:没有指明位宽的时候默认为32位

{0, 1} = 64'h0000_0001_0000_0000

总结——举例计算

1、区分按位与和逻辑与的结果个数,按位与的结果位数和操作数相同,逻辑与的结果位数为1bit

2、只要操作数中包含1,那么逻辑与的时候该操作数会判断为真(下面的A和B为真,C为假)

3、按位运算分为双目和单目操作,单目操作的话结果为1bit

4、逻辑操作和按位操作的输出结果中只有0、1、x,没有z

5、~是按位操作符,!是逻辑操作符

a = 4'b1100 b = 4'bx110

a&b = 4'bx100

a&&b = 1'b1

A = 4'b0x1z B = 4'b01xx C = 4'00xz D = 4'b11xz

A&&B = 1'b1

A&&C = 1'b0

A&B = 4'b0xxx

A&C = 4'b0xxx

&A = 0 //只要该操作数中包含0,那么按位相与的结果一定为0

&C = x

|C = x

|D = 1

三、数据类型

总共:19种

1、基本类型:reg、wire、integer、parameter

当信号没有定义类型时,缺省类型为wire,缺省值为高阻Z。

wire:常和assign用来描述组合逻辑,verilog中输入输出缺省类型为wire。

reg:寄存器数据类型,缺省值是未知的,无符号数,但reg可以是负数也可以是正数。

在表达式的操作数中被当作是无符号数,假如是4bit的-1,则在实际运算时是-1的补码,也就是+15。

在always块内的每一个信号都必须是reg类型。

integer:寄存器数据类型,有符号数,最小为32位,与宿主机的字的位数。

parameter:定义常量,用来提高代码的可读性和可维护性

- reg 型和 wire 型的区别:reg 型保持最后一次的赋值,而 wire 型则需要持续的驱动。

- reg, integer, real,time 都是寄存器数据类型,定义在 Verilog 中用来保存数值的变量,和实际的硬件电路中的寄存器有区别。

- reg、integer是可综合的,

time(64位)不可综合,real(32位)由仿真器决定。

2、位宽扩展

-4 = 1100

扩展为8bit数:1111_1100,有符号数位宽小的扩展为位宽大的,最高位补的根据符号数来添加

四、条件语句

1、条件语句必须在过程块中使用,其他地方不可以。

2、0、z、X都是假,只有1条件才为真

3、出现锁存器的情况:

- if else没有写完整

- always里面,如果给定条件下变量没有被赋值,这个变量将一直保持原来的值,就会生成锁存器

- 有else不一定没有锁存器,没有else也不一定有锁存器。

4、case语句如果情况完备,可以不写default

五、循环语句

1、for

for:for循环几次,就会把电路复制几次,循环次数越多,面积越大,综合越慢

2、generate

generate:生成可配置的、可综合的RTL设计结构。在elaboration阶段、仿真之前执行,必须保证generate的所有表达式都是常量

应用场景:

- 多次实例化某个模块

- 条件generate,if-generate或者case-generate

- 断言

module n_bit_xor

#(parameter SIZE = 16)

(

input [SIZE-1:0] a,

input [SIZE-1:0] b,

output [SIZE-1:0] y

);

genvar i;

generate

for(i=0;i<SIZE;i=i+1)begin:label //这里一定要写模块名称,否则会报错

xor u_xor(y[i], a[i], b[i]);

//会实例化生成label[0].u_xor、label[1].u_xor、label[2].u_xor

//实例化后的层次路径为n_bit_xor.label[0].u_xor

end

endgenerate

endmodule

六、function和task

| function | task |

|---|---|

| 只能用于组合逻辑 | 组合逻辑和时序逻辑都可以,但只有组合逻辑才能综合 |

| 可以有/无返回值,缺失则返回一位寄存器类型数据 | 无返回值 |

| 只能出现在过程块内,不能出现initial和always | |

| 至少有一个输入 | 多个输入/输出/双向端口 |

| 只能调用函数 | 可以调用函数/任务 |

| 不包含时间控制语句 | 可包含时延控制语句(不可综合) |

七、initial和always

1、initial和always相同点和区别

之前在SV语法的这篇文章里面有:传送门

initial:初始化仿真变量,作为电路的仿真信号来生成激励

always:边沿触发和电平触发,可综合成寄存器或者锁存器

2、always和assign语句区别

- assign语句赋值的信号类型为wire,always块里面是reg类型,但是不是真的寄存器,只有当always的触发条件为时钟上升沿,才会被综合为触发器

- 当仿真时,a=0,但是b是不定态。因为b的触发条件是always内的所有输入信号发生改变,才会变化,而1‘b0始终是不变的

assign a = 1'b0;

always@(*)

b = 1'b0;

八、模块例化

在verilog 中,模块实例化子模块的关联方式是端口关联。

信号端口可以通过位置或名称关联,但是这两种关联方式不能够混合使用。

九、verilog抽象级别

-

系统级(System Level):该层次主要描述系统的高层次抽象,例如输入输出接口、处理器、内存等。在该层次下,主要是通过函数调用等方式描述系统的功能和数据流,并且常常使用高级编程语言进行描述,例如C++、Python等。

-

行为级(Behavioral Level):该层次主要描述模块的行为,例如模块如何响应输入、产生输出以及模块之间的数据传输等。在该层次下,主要是使用语句和操作符等方式描述模块的行为,例如if-else、for、assign等。

-

功能级(Functional Level):该层次主要描述模块的功能,例如模块的输入输出接口、操作和算法等。在该层次下,主要是使用模块实例化和信号连接等方式描述模块的功能,例如module、input、output等。

-

寄存器传输级(Register Transfer Level,RTL):该层次主要描述模块的数据流和状态转移,例如模块内部的寄存器、时序逻辑等。在该层次下,主要是使用寄存器和时序逻辑描述模块的状态转移,例如always @(posedge clk)、reg、wire、assign等。

-

门级(Gate Level):该层次主要描述模块的硬件实现方式,例如使用哪些逻辑门、多路器等。在该层次下,主要是使用逻辑门和时钟触发器等基本电路组件描述模块的硬件实现,例如and、or、not、dff等。