紫光同创 FPGA 开发跳坑指南(五)—— DDR3 控制器 IP 的仿真

这段时间一直忙着工作项目的事情,今天终于抽出时间,分享一下紫光同创 DDR3 IP 的仿真经验 ~

目录

1 搭建仿真环境

1.1 编写激励文件

1.2 自动化仿真

2 DDR3 写操作仿真

3 DDR3 读操作仿真

1 搭建仿真环境

1.1 编写激励文件

仿真激励文件需要包含以下四个部分:

(1)时钟定义

DDR3 IP 需要一个 50MHz 的参考时钟,这个时钟频率与前面 DDR3 IP 配置阶段的设定值是一致的。如果系统 PLL 的输入时钟频率也是 50MHz,那么这两个时钟可以是同一个。

(2) 顶层实体

顶层实体其实就是你设计的顶层模块,没什么特殊的。

(3)DDR3 仿真模型

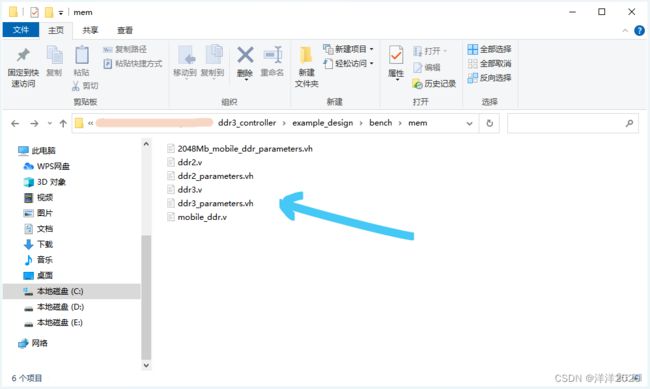

DDR3 仿真模型存放在 IP 核的 example_design/bench/mem 文件夹下,仿真模型用于模拟 DDR3 单元,在仿真过程中与顶层实体进行数据交换。

这里只需要 ddr3_parameters.vh 和 ddr3.v 这两个文件,注意仿真模型需要用 SystemVerilog 编译。

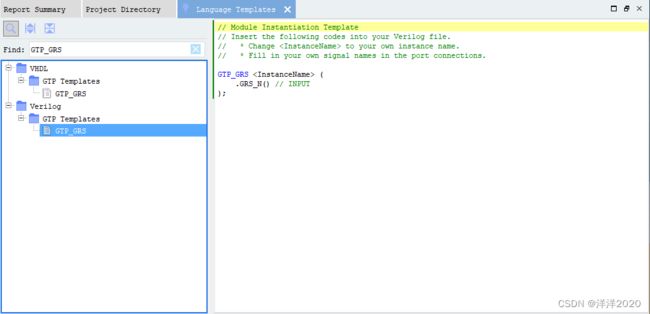

(4)全局复位网络

这个全局复位网络是紫光同创的仿真要求,全局复位网络的推荐写法可以在 Language Templates 工具中找到。

如果激励文件没有例化 GTP_GRS,后续 Modelsim 仿真阶段会报错。

1.2 自动化仿真

通常 DDR3 IP 的设计文件较为繁多,对于经常烧脑的 FPGA 工程师来说,使用 Python 文本自动化处理不失为一种好方法。

紫光 DDR3 IP 的设计文件存放在 IP 核的 rtl 文件夹下,使用 Python os 库遍历该文件夹,根据后缀名筛选出 .v 文件和 .vp 文件,并写入 file_list.f 文件,此为自动化仿真的第一步。

import os

if __name__ == "__main__":

file_list = []

for root, directory, files in os.walk('./ddr3_controller/rtl'):

for file in files:

if file[-2:] == ".v" or file[-3:] == ".vp":

file_list.append(root.replace('\\', '/')+'/'+file)

with open('./file_list.f', 'w') as f:

for file in file_list:

f.write("{:s}\n".format(file))在生成的 file_list.f 文件后面加上 DDR3 仿真模型路径和仿真参数。

./ddr3_controller/example_design/bench/mem/ddr3_parameters.vh

./ddr3_controller/example_design/bench/mem/ddr3.v

+define+SIMULATION

+define+den4096Mb

+define+sg25E

+define+x16

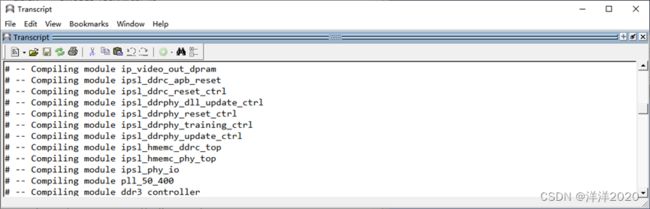

自动化仿真的第二步是编写 tcl 脚本,指定 SystemVerilog 语言编译设计文件。

# 创建工作库

if [file exists work] {

file delete -force work

}

vlib work

vmap work ./work

# 使用SystemVerilog编译IP文件

vlog -sv -f ./file_list.f -work work

# 此处编译用户设计文件

# vlog -incr top.v top_tb.v -work work

# 启动仿真

vsim -voptargs=+acc work.top_tb -Lf pango -Lf ddrc -Lf ddrphy -t 1fs

# 运行2ms

run 2 ms自动化仿真的第三步是编写 bat 脚本。

powershell -command vsim -do ddr3_sim.tcl此处需要确保 Modelsim 安装路径添加到系统环境变量中。

最后,双击运行 bat 脚本,就可以自动打开 Modelsim,编译并启动仿真。

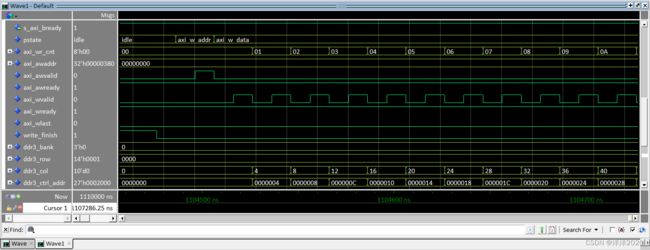

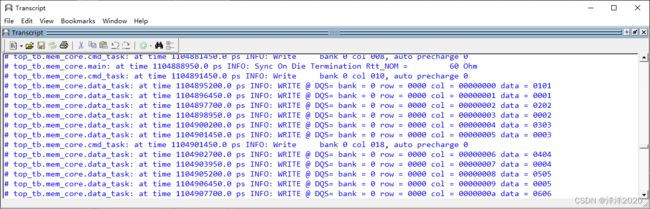

2 DDR3 写操作仿真

要进行 DDR3 的读写操作,需要等待 ddr_init_done 拉高。当 write_finish 信号拉低之后,就进入了 DDR3 的写操作周期。

数据端口在波形窗口中不便观察,可以结合命令行窗口查看。

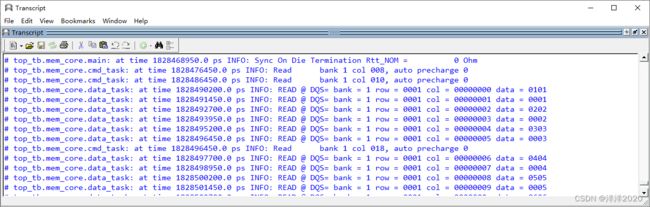

3 DDR3 读操作仿真

新建一个波形窗口,观察 DDR3 读操作的过程。当 read_finish 信号拉低之后,进入 DDR3 的读操作周期。

同样可以在命令行窗口查看读取得到的数据。