DFT学习笔记 -ijtag下的mbist电路

目录

MBIST Basic Process

Tessent IJTAG structure

TMB & Mem Interface

SIB

BAP

之前过了一遍mbist的脚本,介绍了脚本的行为和功能。这里从mbist的原理出发,看看tessent插了哪些电路,功能是什么。

MBIST Basic Process

先简单介绍一下mbist的基本流程,为后面的细节学习做个指导:

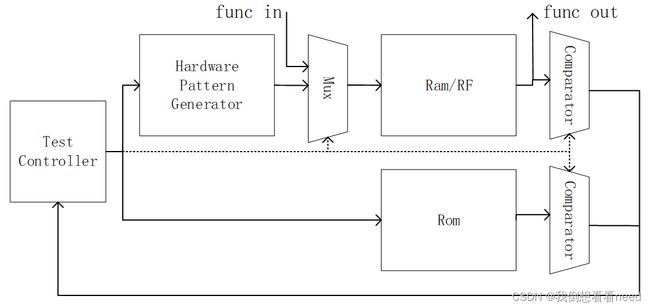

当测试控制模块接收到开始测试的指令后,首先会切换存储器的输入输出到测试模式(Memory有自己的Test Mode),同时启动硬件向量生成模块开始产生和给出测试激励,同时计算存储器的输出期待值。存储器接收到测试向量之后,会间隔执行写/读/使能的操作,遍历测试所有地址下每个bit单元的写/读功能。最后,通过Q端输出的读取值,会与测试控制模块计算的期待值进行比较,是否正确的结果反馈到测试控制模块。

Tessent IJTAG structure

这是tessent基于ijtag产生的mbist电路结构,左侧是高层看下来的情况,最左侧的深蓝模块是TAP,它的端口为测试电路最外围的port,用于获取外部给予的测试指令(一般是ATE通过Pad灌进来的),所有block的测试指令都来自TAP。block内部左侧的深蓝模块是sib,它的作用相当于一个开关,用来决定是否开启它下方连着的ijtag扫描链。与它相连的是tessent生成的instrument,包括mbist测试接口和测试电路(tessent将自己插入的逻辑都叫做instrument),并且tessent会生成相应的icl和pdl文件对其进行描述。

这里解释一下icl和pdl文件:

ICL(Instrument Connectivity Language):描述instrument之间的硬件电路连接关系。

PDL(Procedural Description Language):描述给定level下(通过指定current_design)instrument的用法,比如如何测试或操作。有了ICL及PDL文件,工具就可以很方便的得到这个 IP 测试相关的信息,非常有利于系统的集成。

右侧描述了block内部的mbist电路结构,可以看到sib下提着的instrument包括BAP,TMB,MemInterface,还有可能挂着更下一极的sib。

名词解释:

TAP:Test Access Port. 由JTAG五组端口获取外部给予的测试指令,并转换到IJTAG扫描链上,移位到其后的模块内;

SIB:Segment Insertion Bit. SIB可以开启或关闭其下对应的IJTAG扫描链,进入测试状态; BAP:BIST Access Port. BAP起到SIB下发到MBIST Controller的接口作用;

TMB:Tessent Memory BIST Controller. 内含对Memory测试控制的状态机逻辑(FSM)、生成向量的逻辑(Pattern Gen)及比较逻辑(Comp);

Mem Interface:TMB与mem之间的接口,每一颗mem都会例化相应的mem interface。

根据mem的分组,一个BAP可以挂若干个controller,一个controller控制一组mem Interface。可以简单的理解mbist的指令通路为:

TAB->SIB->BAP->BIST电路(Mbist controller->interface)->memory。我们一开始介绍的mbist基本流程就是描述的Mbist controller、interface和memory三者之间的交互,大家可以跟上面对应一下。

TMB & Mem Interface

下面介绍一下具体的交互过程。

上图是MbistController的结构图,包括FSM(有限状态机),Signal Gen,COM

- TMB中的FSM,由MBIST_EN控制开启,BIST_SETUP进行配置。 FSM控制SIGNAL GEN信号,一个是送入到mem interface中的mux中非func的一端口,另一个是数据送入到COMP和经过RAM的数据进行对比。同时,SIGNAL_GEN会反馈信号控制FSM进行下一步操作。

- test数据送入到interface中,然后经过SRAM输出之后,送回到TMB中的COMP中进行和原始数据比较,如果数据比对正确,则MBIST_GO拉高,否则如果数据对比错误,则MBIST_GO变低。同时在比对初期,COMP会送出CMP_STAT信号。

- 这个FMS控制相应的MEM比对完成,则输出MBIST_DONE信号。

- TMB中的MBIST_GO和MBIST_DONE信号,是可以在仿真过程中进行观测的。从而用于debug。

需要注意的是

在图中可以看到COMP在mem interface中和TMB中都存在,这是因为两者存在都是合理的,只不过都有优缺点。具体的design中到底怎么放置,需要结合设计进行具体分析。

在MEM interface中时候: 虽然增加了gate count ,但是反馈给TMB中的信号只有一位GO信号,减小PR effort

在TMB中的时候: COMP被shared,减少了gate count。COMP的大小取决于控制所有的mem中的最大宽度,且增大PR effort。

————————————————

版权声明:本文为CSDN博主「提着脑袋去学习」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/sinat_27691203/article/details/126332996

Test flow:

- Standby: MBIST_EN拉高指示测试clock开始

- Initialize: 初始化完成的标识为 MBIST_EN=1&&BIST_SETUP=01

- Test in progres: MBIST_GO=0 when error occurs, otherwise MBIST_GO keeps as 1

- Finish: MBIST_DONE=1

Test results:

- DONE=1&&GO=1: test finished and pass

- DONE=1&&GO=0: test finished and at least 1 mem fail

- DONE=0&&GO=1: test unfinished and no error occurred

- DONE=0&&GO=0: test unfinished and at least 1 mem fail

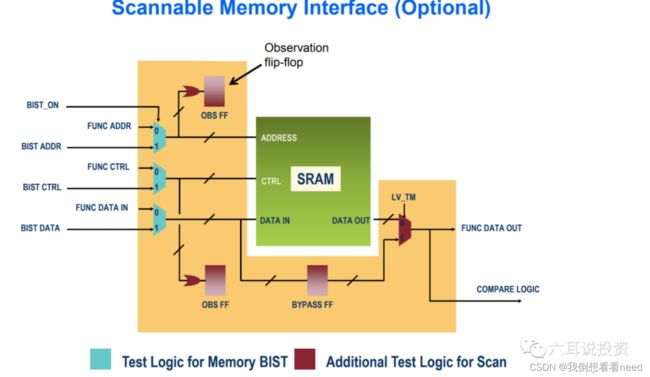

上图是MemInterface的结构,红色块是插入的scan logic。

我们知道ijtag主要用于design pad口的test,mbist 主要用于mem的test,而scan主要用于func logic的test。为何非要在mem interface 插入scan logic呢?

当scan不包含mem时候,此时mem为blackbox,也就是scan mode下的mem bypass 模式:

1)此时BYPASSFF正常工作,把mem bypass掉,给到LV_TM这个mux并传送出去进行观察。

2)此时需要OBSFF也就是observation flip-flop,因为FUNC ADDR的尽头是一个被认为black box的SRAM,这个数据不可观测,会导致scan mode时候,FUNC ADDR这一路观察不到最终结果,会降低coverage,因此增加OBSFF。

当scan 包含mem时候,此时会吃专门的mem 的lib,也就是scan mode下的mem no bypass模式:

1)此时就不需要BYPASS逻辑了,数据正常读入data in,然后正常读出data out,最后经过LV_TM会选择0端口,此时相当于对mem进行了scan test。此时读入的mem lib为特殊专门用于dft的mem lib。

2)这个当然会增加scan 测试时间,但是同时也会提高coverage

————————————————

版权声明:本文为CSDN博主「提着脑袋去学习」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/sinat_27691203/article/details/126332996

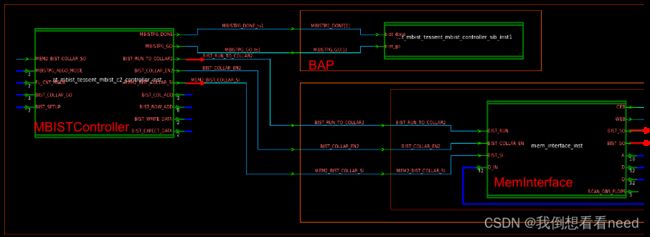

这是tessent生成的BAP、controller、MemInterface、Mem的部分连接。controller通过BIST_RUN信号指示进入测试状态,并且输入测试信号进来,interface把信号传给mem,并且Q_IN接收mem输出的结果,输出给controller,并且给出BIST_GO信号。最后controller把GO/DONE信号传递给BAP。

SIB

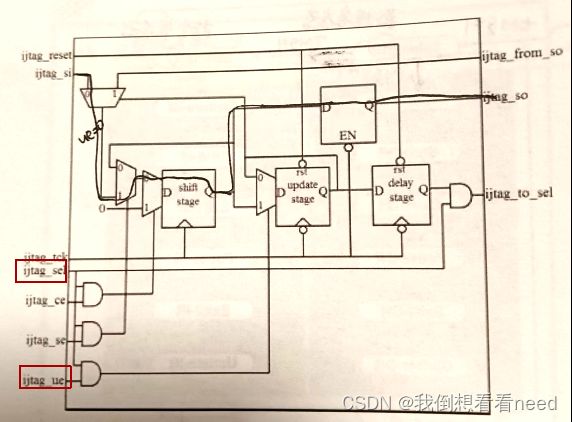

看完MBIST电路,这里来看看ijtag的结构。ijtag又叫IEEE1687协议,SIB是ijtag(ieee 1687)协议中的一个重要组件,在ijtag之前的1149.1协议中,TAP Controller 会发送一大堆信号去控制每一个专属的 TDR,比较冗杂,还会带来一些时序问题。而ijtag引入了SIB结构,它相当于一个开关,会产生一个select信号,只有当select拉高时,信号才会输入进SIB后面的子电路中。这样所有的 ShiftDR, CaptureDR,UpdateDR 都变成了全局信号,我们只需要将全局控制信号广播给每个 TDR,然后通过 local 的 Select 进行选择,被选中的TDRs才会被传入信号。

这是tessent中SIB的结构图,有三个使能端口:se(shift enalble),ce(capture enable),ue(update enable),分别控制shift,read,write三个功能。输入sel端口判断当前SIB是否被选中,只有当sel=1,才能成功使能相应的功能。其中,write功能可以控制数据是否能流入子网络,SIB会生成一个新的sel信号给它的子网络。如果ue=0的话,SIB的子网络会被bypass掉。当数据shift到某个时刻,这个值是我们想要给出去的值,那么我们会把 shift 停下来,trigger 一下 UpdateDR,数据就写出去了。

这是tessent生成的sib结构,这里选中显示了sel_pin的连接。可以看到,block的ijtag_sel port同时选择sib_sti和sib_tdrCmn;sib_sti下面接续挂载了sib_mbist和bap,sib_tdrCmn下面挂载了tdr_Cmn。

BAP

说完了bist电路和ijtag网络,最后看看BAP和controller是怎么连接的。BAP就是BIST Access Port,是BIST电路的接口,一方面负责给出的信号到BIST,实现对MbistController的初始化、配置和启动,另一方面收集BIST完成后的测试结果传递出去。

BAP提供两种访问方式,一种通过IJTAGNetwork接口进行访问,一种通过BAP直接访问接口进行访问。BAP通过接收到的信息对下面挂载的controller进行初始化、配置和启动操作。

这是BAP上挂着两个controller的情况,可以对照着看看。