Xilinx 差分信号 LVDS传输实战

目录

1.LVDS的概念

2.XILINX FPGA 差分信号解决方案

(1)IBUFDS

(2)OBUFDS

(3)IOBUFDS(三态差分输入输出)

3.LVDS中的终端电阻

4.LVDS 电气特性

(1)LVDS25

(2)LVDS25

5.LVDS 自环测试

1.LVDS的概念

LVDS ( Low Voltage Differential Signalin )是一种低振幅差分信号技术。它使用幅度非常低的信号(约 350mV ) 通过一对差分 PCB 走线或平衡电缆传输数据。大部分高速数据传输中,都会用到 LVDS 传输。

目前 FPGA LVDS 实际上有大量的应用,特别是在高速 ADC, 高分辨率摄像头,液晶屏显示技术等应用领域。所以掌握 LVDS 通信也是我们 FPGA 开发者的必备基本技能。本文首先简要介绍一些 XILINX FPGA 的 LVDS 解决方案。

2.XILINX FPGA 差分信号解决方案

(1)IBUFDS

(2)OBUFDS

(3)IOBUFDS(三态差分输入输出)

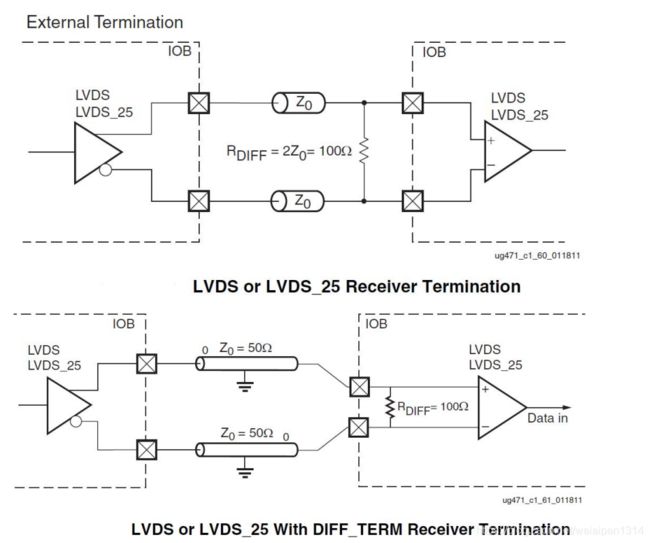

3.LVDS中的终端电阻

注:如果要使用内部的终端电阻,对于 HP 的 LVDS 信号 BANK 电压必须是 1.8V,而对于 HR 的 LVDS25 BANK 信号必须是 2.5V,否则可以使用外部终端电阻。

4.LVDS 电气特性

(1)LVDS25

VCCO 是 2.5V

VOH 是高电平最大 1.675V

VOL 低电平最小 0.7V

VODIFF 差模电压最大 600mv , 最小 247mv, 典型值 350mv

VOCM 输出共模电压,最小 1V 最大 1.425V ,典型值 1.25V

VIDIFF 输入差模电压,最大 600mv, 最小 100mv, 典型 350mv

VICM 输入共模电压,最大 1.5V ,最小 0.3V ,典型 1.2V

(2)LVDS25

VCCO 是 1.8V

VOH 是高电平最大 1.675V

VOL 低电平最小 0.825V

VODIFF 差模电压最大 600mv , 最小 247mv, 典型值 350mv

VOCM 输出共模电压,最小 1V 最大 1.425V ,典型值 1.25V

VIDIFF 输入差模电压,最大 600mv, 最小 100mv, 典型 350mv

VICM 输入共模电压,最大 1.5V ,最小 0.3V ,典型 1.2V

LVDS 器件电气特性是否兼容主要看, VODIF , VOCM , VIDIFF , VICM ,可以看到, LVDS25 和 LVDS 的差分电 气特性是兼容的。

5.LVDS 自环测试

module lvds_loop(

// sysclk input 系统时钟

input clk_i_p ,

input clk_i_n ,

// TTL输入输出

input rx_i ,

output tx_o ,

//lvds loop input 输入的LVDS时钟

input dclki_p ,

input dclki_n ,

input din_p ,

input din_n ,

//lvds loop output 输出的LVDS时钟

output dclko_p ,

output dclko_n ,

output dout_p ,

output dout_n

);

wire clk50m,dclki,din;

reg rx_lvds = 1'b0;

wire clk_i;

// 得到单端系统时钟,对差分时钟采用 IBUFGDS IP 核去转换

IBUFGDS CLK_U(

.I ( clk_i_p ),

.IB ( clk_i_n ),

.O ( clk_i )

);

//clk_wiz_0 uclk(.clk_out1(clk50m),.clk_out2(clk5m), .clk_in1_p(clk_i_p),.clk_in1_n(clk_i_n));

clk_wiz_0 uclk(.clk_out1(clk50m),.clk_in1(clk_i));

// lvds out, 把 rx 接收到的数据,通过LVDS发送出去

// 输出50M的差分时钟

OBUFDS #(

.IOSTANDARD ( "DEFAULT" ), // Specify the output I/O standard

.SLEW ( "SLOW" )

)

dclko_OBUFDS

(

.O ( dclko_p ),

.OB ( dclko_n ),

.I ( clk50m )

);

// 输出接收到的数据

OBUFDS #(

.IOSTANDARD ( "DEFAULT" ), // Specify the output I/O standard

.SLEW ( "SLOW" )

)

dout_OBUFDS

(

.O ( dout_p ),

.OB ( dout_n ),

.I ( rx_i )

);

//lvds in

// 还原单端时钟

IBUFDS

#(

.DIFF_TERM ( "TRUE" ), // Differential Termination

.IBUF_LOW_PWR ( "TRUE" ), // Low power="TRUE", Highest performance="FALSE"

.IOSTANDARD ( "DEFAULT" ) // Specify the input I/O standard

)

dclki_IBUFDS

(

.O ( dclki ), // 1-bit output: Buffer output

.I ( dclki_p ), // 1-bit input: Diff_p buffer input (connect directly to top-level port)

.IB ( dclki_n ) // 1-bit input: Diff_n buffer input (connect directly to top-level port)

);

// 还原单端数据

IBUFDS

#(

.DIFF_TERM ( "TRUE" ), // Differential Termination

.IBUF_LOW_PWR ( "TRUE" ), // Low power="TRUE", Highest performance="FALSE"

.IOSTANDARD ( "DEFAULT" ) // Specify the input I/O standard

)

ddatai_IBUFDS

(

.O ( din ), // 1-bit output: Buffer output

.I ( din_p ), // 1-bit input: Diff_p buffer input (connect directly to top-level port)

.IB ( din_n ) // 1-bit input: Diff_n buffer input (connect directly to top-level port)

);

always @(posedge dclki)begin

rx_lvds <= din;

end

assign tx_o = rx_lvds;

endmodule