tb文件 vivado_Vivado IDDR与ODDR原语的使用

在数据的传输过程中,我们经常可以碰见双沿传输数据到FPGA,或者FPGA传输双沿数据给外部芯片,最常见的例子就是DDR芯片。这里说明一下,FPGA内部处理的数据都是单沿数据,那么双沿数据的变换只能发生在FPGA的IOB上面,这里有特定的硬件结构可以实验上面单沿变双沿的方法,也就是使用原语进行一些列的操作。本次实验的主要内容如下:

以千兆网RGMII为例实现单沿变双沿、双沿变单沿的操作。经过之前博客的理解,我们可以知道RGMII的协议是双沿传输,那么我们将以此为例实现双沿4bit数据变单沿8bit数据——FPGA接收,单沿8bit数据变双沿4bit数据——FPGA发送。

IDDR与ODDR的简述

这里的表述,我们主要依靠技术手册来给大家进行讲解。

其中IDDR的原语如下:

IDDR #(

.DDR_CLK_EDGE ("OPPOSITE_EDGE" ), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1 (1'b0 ), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2 (1'b0 ), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE ("SYNC" ) // Set/Reset type: "SYNC" or "ASYNC"

) IDDR_ctrl (

.Q1 (data_en ), // 1-bit output for positive edge of clock

.Q2 (data_err ), // 1-bit output for negative edge of clock

.C (rx_clk ), // 1-bit clock input

.CE (1'b1 ), // 1-bit clock enable input

.D (rx_ctrl ), // 1-bit DDR data input

.R (~rst_n ), // 1-bit reset

.S (1'b0 ) // 1-bit set

);

其中IDDR主要有三种工作模式,分别是:“OPPOSITE_EDGE”, “SAME_EDGE”,“SAME_EDGE_PIPELINED” 。上面每一位的介绍在原语的注释中都得到了比较详细的解释,这里不再赘述。这三种工作模式的不同其实就是时序的不同,下面分别进行介绍:

这里主要注意,一个时钟的上升沿与下降沿数据正好可以在下一个时钟上升沿的Q1、Q2输出,这也是最常见的使用方式。我们千兆网的接收信号使用的就是该模式。

这里特别注意,一个时钟的上升沿和下降沿的两个数据在Q1、Q2的表示分别在下一个时钟与下下一个时钟体现出来,原来的两个数据被分裂成两个时钟表示。

其中这种模式与第一种的模式是Q1、Q2是同步的,前者是异步的,这种模式数据的读取比第一种模式晚了一个节拍。当然千兆网的数据接收也可以使用该模式,以为控制端也是使用该模式进行解码。

其中ODDR的原语如下:

ODDR #(

.DDR_CLK_EDGE ("SAME_EDGE" ), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT (1'b0 ), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE ("SYNC" ) // Set/Reset type: "SYNC" or "ASYNC"

) ODDR_ctrl (

.Q (tx_data_ctrl ), // 1-bit DDR output

.C (gb_tx_clk ), // 1-bit clock input

.CE (1'b1 ), // 1-bit clock enable input

.D1 (gb_tx_data_en ), // 1-bit data input (positive edge)

.D2 (gb_tx_data_err ), // 1-bit data input (negative edge)

.R (~rst_n ), // 1-bit reset

.S (1'b0 ) // 1-bit set

);

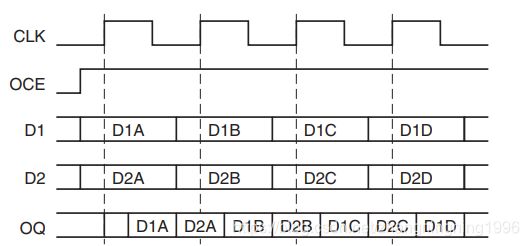

同样,上面每一位的介绍在原语的注释中都得到了比较详细的解释,这里不再赘述。其中ODDR有两种不同的工作模式。我们将进行如下介绍:

从上面我们可以看出,该模式是将两个时钟的D1、D2拼成了一个时钟的上升沿与下降沿对应的数据。我们本次千兆网的输出项目中不会使用该模式,因为D1与D2会错开一个时钟。

从上面的时序图中我们可以看出,同一个时钟的D1、D2转换成了同一个时钟的上升沿与下降沿。我们本次项目中使用的就是这个模式。

RGMII时序简述

前面已经讲解了常见的以太网物理层协议接口,其中RGMII是双沿数据,需要使用原语进行相应单双沿变化的操作。其中,RGMII协议的具体时序图如下:

这里有几点注意整理如下:

1、TXD的0位上升沿与下降沿分别对应8位数据的0位与4位,TXD其他的位数以此相互递增。

2、RXD的0位上升沿与下降沿分别对应8位数据的0位与4位,RXD其他的位数以此相互递增。

3、TX_CLK是输入时钟,RX_CLK是输出时钟。

4、XX_CTL线上升沿对应的是数据使能位,下降沿对应的是数据错误位。

千兆网输入与输出模块的设计

gbit_top模块:

`timescale 1ns / 1ps

// *************************