Altera SOPC Builder 指南(SOPC)(DE2)

这篇向导介绍altera的sopc builder软件,它用来实现在altera的FPGA器件上使用Nios II处理器的系统。通过配合Quartus II使用sopc builder实现一个简单的系统来一步一步的详细描述系统的开发流程。

在设计的最后一步包含在一个实际的FPGA器件上配置设计电路,并运行一个应用程序。前提是,一台安装quartus II和Nios II软件的电脑,并连接DE2开发板。

屏幕截图是使用的quartus II 9.1 版;如果使用其他版本,可能略有不同。

目录:

Nios II 系统

Altera的SOPC Builder

在Quartus II的项目里集成Nios II系统

运行应用程序

Altera的Nios II是一个用硬件描述语言定义的软处理器,通过Quartus II CAD套件可在Altera的FPGA器件上实现。要实现一个有用的系统,有必要添加其他功能单元,比如内存、输入/出接口、计时器和通信接口。为了方便的实现这样一个系统,使用CAD工具来实现SOPC很有效。Altera的SOPC Builder就是这种软件。

这篇指南提供Altera的SOPC Builder的简介,以使读者快速的在DE2开发板上实现一个简单的Nios II系统。关于SOPC Builder的更多介绍,可参考Nios II Hardware Development Tutorial。SOPC Builder完整的描述可参考Quartus II Handbook Voulume 4:SOPC Builder。这些文档可在Altera网站获得。

1 Nios II系统

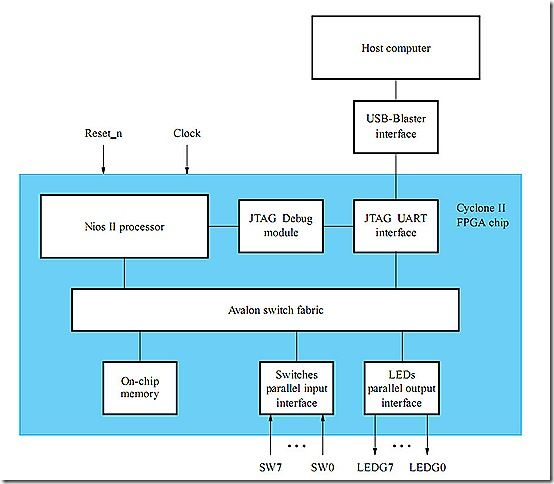

在DE2开发板上可实现一个Nios II系统如图1.

NIOS II处理器和连接DE2上其他芯片的接口都在Cyclone II FPGA片内实现。这些组件的相互连接通过Avalon 交互网络实现。Cyclone II的内存块可为NIOS II处理器提供片上内存。DE2上的SRAM、SDRAM和Flash存储芯片通过适当的接口访问。并行和串行输入/出接口提供计算机系统典型的I/O接口。一个特殊的JTAG UART接口用来连接提供DE2和主机之间的usb连接的电路。这个电路和相关的软件叫做USB-Blaster。另一个模块叫做JTAG调试模块,用来许可主机控制NIOS II系统。它使能下载程序到内存,开始和停止操作,设置断点和收集实时跟踪数据。

既然是用硬件描述语言在FPGA芯片上实现NIOS II 系统的每个部分,有经验的用户可以书写实现系统的每个代码。这是一个费时且困难的任务。更简单的方法是在sopc builder里通过选择要求的组件和指定参数来适配整个系统的需求以实现想要的系统。这篇指南通过设计一个非常简单的系统来描述sopc builder的功能。也适用于大系统。

图2

图2给出了我们的例子系统。这个系统实现一个很小的任务。de2上的8个双稳态开关SW7-0用来控制8个绿色的LED,LEDG7-0的亮灭。开关通过配置为输入的并行I/O连接到NIOS II系统。led被配置为输出的并行I/O的信号驱动。要实现要求的操作,开关的8位的状态将发送到输出端口驱动led。这将通过NIOS II处理器执行存在片上内存的程序实现。要求连续操作,好像灯的状态根据开关的状态相应变化。

我们将用sopc builder设计图2描述的硬件。接着指定输入、出的管脚连接。然后,配置fpga实现系统。最后用NIOS II Debug Client这个软件工具汇编,下载和执行一个NIOS II程序实现任务。

依照本指南,读者将学会:

- 使用sopc builder设计一个基于NIOS II的系统

- 集成设计的NIOS II系统到quartus II项目

- 在de2上实现设计的系统

- 运行关于NIOS II处理器的一个应用程序

2 altera的sopc builder

sopc builder是配合quartus II使用的一个工具。它使得用户通过简单的选择需要的功能单元和指定参数就可以轻松的创建一个基于nios II处理器的系统。要实现图2的系统,我们必须例化下述功能单元:

- Nios II处理器,作为中央处理器(CPU)

- 片上内存,有Cyclone II的片上内存块组成;我们将指定一个按32位字的4kB的内存

- 2个并行I/O

- 和主机通信的JTAG UART接口

要定义目标系统,启动quartus II,执行下述步骤:

- 为你的系统创建一个新的quartus II项目。如图3所示,我们将项目存在sopc_builder_tutorial文件夹,顶层文件和项目名都命名为lights,你也可以选择不同的项目名和文件夹,注意文件夹不可以包含空格,选择EP2C35F672C6芯片,因为DE2上用的这个。

- 选择Tools > SOPC Builder,在弹出的窗口输入nios_system作为系统名;这也是SOPC Builder将生成的系统的名字。选择Verilog作为目标HDL,系统模块将用这种语言指定。单击OK确认。

- 图5显示了SOPC Builder里的系统组件的标签,用来添加组件到系统和配置选择的组件符合设计需求。可用的组件在窗口的左边列出。指定器件类型为Cyclone II。

- 添加时钟50MHz。

- 添加 Nios II处理器,选择Nios ii/e

- 添加片上内存,选择on-chip Memory(RAM or ROM).32bits,4KB。

- 添加并行I/O,PIO(Parallel I/O),8bits。

- 添加JTAG UART接口。

- 完整的系统如上图所示,这里可对组件重命名,将PIO_0改为Switches,PIO_1改为LEDs。

- 用户可以指定设计系统里组件变量的地址,也可以由SOPC Builder自动分配。选择Systems > Auto-Assign Base Addresses.

- 指定所有需要的组件后,就可以生成系统了。选择System Generation标签,取消Simulation-Create simulation project files,因为本文不用硬件仿真。单击Generate.

任何时候都可以打开SOPC Builder修改设计的系统。添加、删除组件,重新生成系统。

3 将Nios II系统集成到Quatus II工程

要完成硬件设计,必须执行下述步骤:

- 实例化SOPC Builder生成的模块到Quartus II工程

- 引脚指定

- 编译设计电路

- 下载

3.1 实例化SOPC Builder生成的模块

实例化生成的模块取决于整个Quartus II工程设计输入方法的选择。我们选择用Verilog HDL,其它如VHDL和原理图输入的用类似方法。

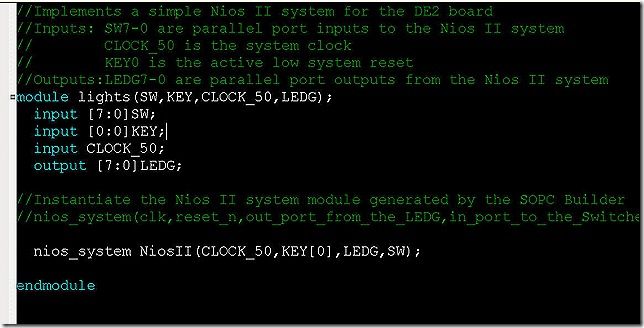

通常,Nios II模块作为较大型设计的一部分。但是,在我们这个简单的例子里不需要其它电路。我们只需要在顶层Verilog文件例化Nios II系统,并连接输入/出端口、时钟,复位,到Cyclone II器件的适当的引脚。

SOPC Builder生成的模块在工程文件夹下的nios_system.v文件。注意这个文件名和我们第一使用SOPC Builder时指定的系统名相同。这个Verilog代码很长。下图描述了nios_system的输入、输出端口信号。

注意那个复位信号是SOPC Builder自动添加的,因为其低电平有效,所以命名为reset_n。

在顶层文件里例化Nios II系统如下图所示。这个模块命名为lights,因为这是我们指定的Quartus II工程的顶层设计实体的名字。注意模块的输入和输出端口名用的是板上的标注名,50-MHz时钟,CLOCK_50,按键开关,KEY,双稳态开关,SW,和绿色LED,LEDG,在DE2手册里都有定义。在名为lights.v的文件输入这些代码。添加这个文件和其他所有SOPC Builder产生的*.v文件到你的Quartus II工程。当然,需要引脚分配文件。引脚分配的步骤可在Quartus II Introduction Using Verilog Design找到。注意这里有个简单的分配引脚的方法,当我们使用和DE2手册里的引脚名一样时,就可直接导入向导文件里给的引脚分配文件DE2_pin_assignments.csv,它在DE2_tutorial\design_files目录下。

既然我们设计的系统要用50-MHz的时钟,工程里要添加必要的时序指定。向导文档Timing Considerations with Verilog-Based Designs讲述了如何做。

当完成必要的设置编译后,你可能发现有些与Nios II系统相关的警告信息,比如某些信号未使用或变量的长度不对,这些警告可忽略。

3.2 下载

将lights.sof下载到FPGA器件。

4 运行应用程序

在FPGA器件配置完要求的硬件后,接下来就需要创建和执行实现期望操作的应用程序。这个可以用Nios II汇编语言或高级语言如C来书写要求的程序实现。我们将描述2中方式。

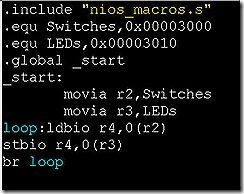

SOPC Builder产生的并行输入/出接口通过接口的寄存器访问。依赖于并行输入/出接口的配置方式,可能有4个寄存器。其中一个叫做数据寄存器。在一个作为输入的并行接口,从数据寄存器读取当前的输入数据。在输出接口,数据寄存器写入驱动输出接口的数据。如果是双向接口,输入/出使用同样的物理路径。这种情况下包含一个数据方向寄存器,用来决定输入/出的方向。在我们的单向并行接口,只需要数据寄存器。在Switches口SOPC Builder分配给数据寄存器的地址是0X000030000,LEDs口的是0X00003010.

4.1 使用Nios II汇编语言程序

下图给出的汇编语言程序实现了我们的任务。这个程序加载2个并口的数据寄存器的地址到处理器的寄存器r2和r3.然后无限循环,用于从输入口到输出口传送数据。

关于Nios II汇编语言的指令参看向导文档 Introduction to the Altera Nios II Soft Processor.

输入上述代码,保存为lights.s并存放在工作目录下。我们将这个文件保存在sopc_builder_tutorial\app_software.这个程序将被汇编和转换成一个S-Record文件,lights.srec,适用于下载到Nios II 系统。

Altera提供Monitor软件,叫做Altera debug client,配合DE2实验板使用。这个程序提供一种简单的编译、汇编和下载的功能。也可以调试程序。(ps,用光盘里的这个程序,编译报错,换Monitor可成功编译和加载应用程序)。

Altera Monitor的使用见其自带的帮助。