Xilinx Zynq UltraScale系列高端FPGA解码MIPI视频,基于MIPI CSI-2 RX Subsystem架构实现,提供5套工程源码和技术支持

目录

- 1、前言

-

- 免责声明

- 2、我这里已有的 MIPI 编解码方案

- 3、本 MIPI CSI2 模块性能及其优缺点

- 4、详细设计方案

-

- 设计原理框图

- OV5640及其配置

- 权电阻硬件方案

- MIPI CSI-2 RX Subsystem

- Sensor Demosaic图像格式转换

- Gammer LUT伽马校正

- AXI4-Stream Subset Converter

- VDMA图像缓存

- DP输出

- 5、vivado工程1:Xczu4ev版本

-

- FPGA逻辑设计

- Vitis SDK软件设计

- Vitis HLS补丁

- 6、vivado工程2:Xczu2cg版本

- 7、vivado工程3:Xczu7ev版本

- 8、vivado工程4:Xczu3eg版本

- 9、vivado工程5:Xczu9eg版本

- 10、工程移植说明

-

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 11、上板调试验证

- 12、福利:工程代码的获取

Xilinx Zynq UltraScale系列高端FPGA解码MIPI视频,基于MIPI CSI-2 RX Subsystem架构实现,提供5套工程源码和技术支持

1、前言

FPGA图像采集领域目前协议最复杂、技术难度最高的应该就是MIPI协议了,MIPI解码难度之高,令无数英雄竞折腰,以至于Xilinx官方不得不推出专用的IP核供开发者使用,不然太高端的操作直接吓退一大批FPGA开发者,就没人玩儿了。

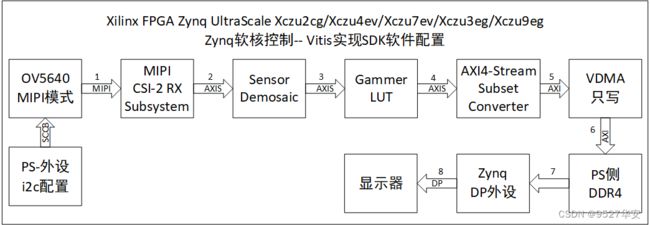

本设计基于Xilinx的 zynq UltraScale系列高端FPGA开发板,采集OV5640摄像头的2Line MIPI视频,OV5640摄像头配置为MIPI模式,引脚经过权电阻方案后接入FPGA的HP BANK的LVDS差分IO;调用Xilinx的MIPI CSI-2 RX Subsystem IP实现MIPI的D-PHY功能,该IP由Xilinx免费提供,将MIPI视频解码后以AXIS视频流格式输出;再调用Xilinx的Sensor Demosaic IP实现RAM转RGB功能; 再调用Xilinx的Gammer LUT IP实现伽马校正功能;再调用Xilinx的AXI4-Stream Subset Converter IP实现RGB顺序调整功能;再调用Xilinx的VDMA IP实现图像三帧缓存功能,将视频写入PS侧的DDR4;最后用Zynq自带的DP外设将视频以DP接口形式输出显示器显示;整个工程调用Zynq软核做IP的配置,Zynq的配置在Vitis SDK里以C语言软件代码的形式运行,所以整个工程包括FPGA逻辑设计和Vitis SDK软件设计两部分,需要具备FPGA和嵌入式C语言的综合能力,不适合初学者或者小白;

本方案提供5套工程源码,5套工程源码的区别在于使用的zynq主控芯片不同,分别是Zynq UltraScale Xczu2cg、Xczu4ev、Xczu7ev、Xczu3eg、Xczu9eg;5套工程源码详情如下:

______________________________________________________________________________

|vivado工程 | 第一套工程 | 第二套工程 | 第三套工程| 第四套工程 | 第五套工程|

|vivado版本 | 2021.1 | 2021.1 | 2021.1 | 2021.1 | 2021.1 |

|输入视频 |OV5640-MIPI|OV5640-MIPI|OV5640-MIPI|OV5640-MIPI|OV5640-MIPI|

|输出视频 | DP | DP | DP | DP | DP |

|Zynq芯片 | Xczu4ev | Xczu2cg | Xczu7ev | Xczu3eg | Xczu9eg |

_______________________________________________________________________________

本文详细描述了Xilinx UltraScale系列高端FPGA解码MIPI视频的设计方案,工程代码编译通过后上板调试验证,可直接项目移植,适用于在校学生做毕业设计、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字成像和图像传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

关于MIPI协议,请自行搜索,csdn就有很多大佬讲得很详细,我就不多写这块了;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、我这里已有的 MIPI 编解码方案

我这里目前已有丰富的基于FPGA的MIPI编解码方案,主要是MIPI解码的,既有纯vhdl实现的MIPI解码,也有调用Xilinx官方IP实现的MIPI解码,既有2line的MIPI解码,也有4line的MIPI解码,既有4K分辨率的MIPI解码,也有小到720P分辨率的MIPI解码,既有基于Xilinx平台FPGA的MIPI解码也有基于Altera平台FPGA的MIPI解码,还有基于Lattice平台FPGA的MIPI解码,后续还将继续推出更过国产FPGA的MIPI解码方案,毕竟目前国产化方案才是未来主流,后续也将推出更多MIPI编码的DSI方案,努力将FPGA的MIPI编解码方案做成白菜价。。。

基于此,我专门建了一个MIPI编解码的专栏,并将MIPI编解码的博客都放到了专栏里整理,对FPGA编解码MIPI有项目需求或学习兴趣的兄弟可以去我的专栏看看,专栏地址如下:

点击直接前往专栏

3、本 MIPI CSI2 模块性能及其优缺点

由于调用了Xilinx的MIPI CSI-2 RX Subsystem IP核,所以性能上就取决于你的FPGA型号,理论上FPGA越高端,支持的IO线速率或者GT高速接口线速率就越高,就能跑速率更高的MIPI视频;

该IP适应性极强,支持的MIPI相机性能参数如下:

![]()

![]()

并且,在越高端的FPGA型号上,该IP支持的高端性能也越多;

由于调用了Xilinx的MIPI CSI-2 RX Subsystem IP核,NIPI视频解码的稳定性很好,且使用及其简单,缺点是看不到源码,出了问题后不好排查,只能在输入输出接口添加ila进行逐级追踪;

本方案使用的FPGA型号为Xilinx Zynq UltraScale系列,属于高端FPGA的MIPI解码应用,再小型的Artix7-35T或者Spartan7、Spartan6等就已经不能使用MIPI CSI-2 RX Subsystem了;

4、详细设计方案

本设计基于Xilinx的 zynq UltraScale系列高端FPGA开发板,采集OV5640摄像头的2Line MIPI视频,OV5640摄像头配置为MIPI模式,引脚经过权电阻方案后接入FPGA的HP BANK的LVDS差分IO;调用Xilinx的MIPI CSI-2 RX Subsystem IP实现MIPI的D-PHY功能,该IP由Xilinx免费提供,将MIPI视频解码后以AXIS视频流格式输出;再调用Xilinx的Sensor Demosaic IP实现RAM转RGB功能; 再调用Xilinx的Gammer LUT IP实现伽马校正功能;再调用Xilinx的AXI4-Stream Subset Converter IP实现RGB顺序调整功能;再调用Xilinx的VDMA IP实现图像三帧缓存功能,将视频写入PS侧的DDR4;最后用Zynq自带的DP外设将视频以DP接口形式输出显示器显示;

本方案提供5套工程源码,5套工程源码的区别在于使用的zynq主控芯片不同,分别是Zynq UltraScale Xczu2cg、Xczu4ev、Xczu7ev、Xczu3eg、Xczu9eg;

设计原理框图

OV5640及其配置

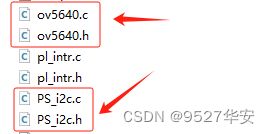

输入视频采用廉价的OV5640摄像头模组,配置为MIPI模式,2 Line,数据格式为RAW10,线速率为1000Mbps,视频分辨率为1280*720,一个时钟一个像素,OV5640需要SCCB总线配置才能运行,该总线等价于I2C总线,使用Zynq自带的i2c片内外设实现配置,SCCB软件配置代码截图如下:

权电阻硬件方案

使用Xilinx官方推荐的权电阻硬件方案将输入的差分MIPI对恢复HS和PL,原理图部分截图如下:

![]()

注意:权电阻方案只在低速率的MIPI模式下可用,高速率的MIPI请用专用芯片实现,比如MC20001,MC系列这种方案可以支持到2Gbps/Lane速率以上,只要FPGA的IO速率够用;

MIPI CSI-2 RX Subsystem

调用Xilinx的MIPI CSI-2 RX Subsystem IP实现MIPI的D-PHY功能,该IP由Xilinx免费提供,将MIPI视频解码后以AXIS视频流格式输出;调用和配置如下:

![]()

![]()

Sensor Demosaic图像格式转换

调用Xilinx的Sensor Demosaic IP实现RAM转RGB功能,该IP通过Vitis的C代码软件配置,Sensor Demosaic调用和C代码软件配置代码截图如下:

![]()

![]()

Gammer LUT伽马校正

调用Xilinx的Gammer LUT IP实现伽马校正功能,该IP通过Vitis的C代码软件配置,Gammer LUT调用和C代码软件配置代码截图如下:

![]()

![]()

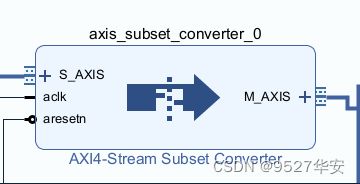

AXI4-Stream Subset Converter

再调用Xilinx的AXI4-Stream Subset Converter IP实现RGB顺序调整功能;因为经过实际操作发现,图像的 RGB 数据顺序需要调整;此IP不需要软件配置;AXI4-Stream Subset Convertert调用截图如下:

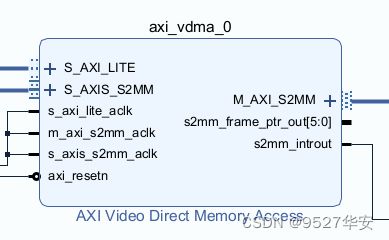

VDMA图像缓存

调用Xilinx的VDMA IP实现图像三帧缓存功能,将视频写入PS侧的DDR4,此处只需要配置器写通道即可,该IP通过Vitis的C代码软件配置;VDMA调用和C代码软件配置代码截图如下:

![]()

DP输出

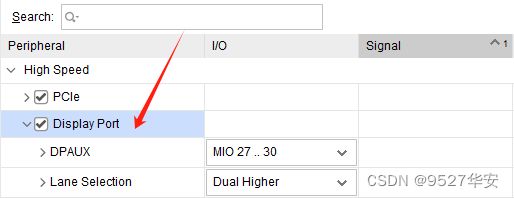

Zynq自带的DP外设,将视频以DP接口形式输出显示器显示;需要在Zynq中使能DP才行,如下:

DP配置c软件代码如下:

5、vivado工程1:Xczu4ev版本

FPGA逻辑设计

开发板FPGA型号:Xilinx–Zynq UltraScale Xczu4ev–sfvc784-2-i;

开发环境:Vivado2021.1;

输入:OV5640摄像头–MIPI–2 Line–RAW10-1280*720;

输出:DP ,分辨率720P;

应用:Xilinx Zynq UltraScale系列高端FPGA解码MIPI视频;

工程Block Design如下:

由于调用IP较多,分散开来很不好看,也不利于阅读,我们将MIPI解码和缓存的核心IP进行了再封装,如上图中红框标记部分,该封装只是形式上的好看而已,没有特殊功能,可以通过如下方法将其展开,查看里面的详细组成和结构,如下:

![]()

展开后如下:

![]()

工程代码架构如下:

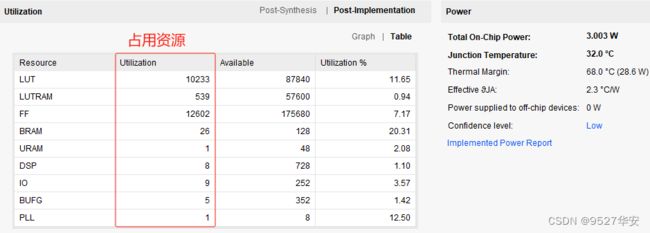

工程的资源消耗和功耗如下:

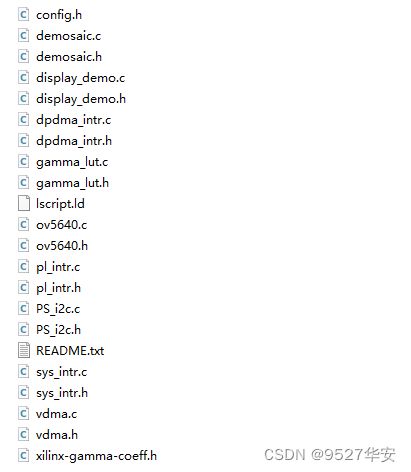

Vitis SDK软件设计

Vitis SDK C语言软件是为了配置FPGA调用的IP,用VItis打开即可查看,代码内容如下:

Vitis HLS补丁

由于工程中用到了HLS生成的IP,Sensor Demosaic和Gammer LUT,可能会出现综合编译失败,或者警告后在Vitis SDK里找不到设备ID等情况,此时需要更改电脑系统时间或者打上官方补丁解决这件事情,具体方法参考这位大佬博文:直接点击前往

6、vivado工程2:Xczu2cg版本

开发板FPGA型号:Xilinx–Zynq UltraScale Xczu2cg;

开发环境:Vivado2021.1;

输入:OV5640摄像头–MIPI–2 Line–RAW10-1280*720;

输出:DP,分辨率720P;

应用:Xilinx Zynq UltraScale系列高端FPGA解码MIPI视频

工程Block Design、工程代码架构、工程的资源消耗、Vitis SDK软件设计和第5章节的“vivado工程1:Xczu4ev版本”大同小异;

7、vivado工程3:Xczu7ev版本

开发板FPGA型号:Xilinx–Zynq UltraScale Xczu7ev–ffvc1156-2-i;

开发环境:Vivado2021.1;

输入:OV5640摄像头–MIPI–2 Line–RAW10-1280*720;

输出:DP,分辨率720P;

应用:Xilinx Zynq UltraScale系列高端FPGA解码MIPI视频

工程Block Design、工程代码架构、工程的资源消耗、Vitis SDK软件设计和第5章节的“vivado工程1:Xczu4ev版本”大同小异;

8、vivado工程4:Xczu3eg版本

开发板FPGA型号:Xilinx–Zynq UltraScale Xczu3eg–sfvc784-2-i;

开发环境:Vivado2021.1;

输入:OV5640摄像头–MIPI–2 Line–RAW10-1280*720;

输出:DP,分辨率720P;

应用:Xilinx Zynq UltraScale系列高端FPGA解码MIPI视频

工程Block Design、工程代码架构、工程的资源消耗、Vitis SDK软件设计和第5章节的“vivado工程1:Xczu4ev版本”大同小异;

9、vivado工程5:Xczu9eg版本

开发板FPGA型号:Xilinx–Zynq UltraScale Xczu9eg–ffvb1156-2-i;

开发环境:Vivado2021.1;

输入:OV5640摄像头–MIPI–2 Line–RAW10-1280*720;

输出:DP,分辨率720P;

应用:Xilinx Zynq UltraScale系列高端FPGA解码MIPI视频

工程Block Design、工程代码架构、工程的资源消耗、Vitis SDK软件设计和第5章节的“vivado工程1:Xczu4ev版本”大同小异;

10、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

![]()

打开工程后会发现IP都被锁住了,如下:

![]()

此时需要升级IP,操作如下:

![]()

![]()

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

![]()

![]()

![]()

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

11、上板调试验证

需要准备的器材如下:

FPHA开发板;

OV5640摄像头;

HDMI显示器;

输出如下:

![]()

12、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下: