Coresight(一)coresight简介

coresight是ARM公司提出的,用于对复杂的SOC,实现debug和trace的架构。该架构,包含了多个coresight组件。众多的coresight组件,构成了一个coresight系统。我们也可以根据coresight架构,实现自己的coresight组件。每个coresight的组件(component),都要遵循coresight架构的要求。

1、 典型的一个coresight的环境

以下是一个典型的coresight环境,包含了两个ARM core,一个DSP,和众多的coresight组件。这个coresight组件,实现对core,DSP的debug和trace功能。

环境中,总共包括3个通路

- trace通路: 将core和DSP内部信息输出到外部

- debug通路:对core和DSP实现debug

- trigger通路: 用于core和core之间,core和DSP之间,传输trigger信号

1.1、trace通路

trace通路,实现对master组件的数据追踪功能,使用ETM来追踪。

ETM负责追踪处理器和DSP的信息,将信息打包,通过ATB总线发送到trace bus上。trace bus上有trace funnel,funnel接收多个ATB总线数据,然后合并成一个ATB总线数据,发送给replicator。

replicator接收到ATB数据,根据配置,将ATB数据发送给ETB和TPIU。

1.2、debug的通路

debug通路,用于外部的debugger,对ARM core和DSP进行调试功能。

上图中,只考虑了JTAG的port。其实还有SW的port。

DAP接收外部端口的JTAG数据,然后转化成对DAP内部的AP的访问,然后AP再转化为memory-mapped的总线访问,去访问soc内部的资源。

上图中,DAP输出两个memory-mapped总线,一个是debug apb总线,连接到debug APB互联上,用于访问debug组件的寄存器,一个是system bus,连接到bus matrix,用于访问soc的内部的资源。

debug APB互联,连接了有CTI,ETM,HTM,ITM,ETB,TPIU等coresight组件,因此外部的debugger可以通过JTAG port,对这些coresight组件进行访问。

bus matrix一般是连接soc的一些外设,如memory,串口等,因此外部的debugger可以通过JTAG port对这些外设设备进行访问。

1.3、trigger通路

trigger通路,用于给指定的组件发送trigger信号,或者接收指定的组件的trigger信号。这个功能由CTI和CTM来实现。

每个core和DSP都有一个CTI组件相连,CTI可以给处理器(DSP)发送trigger信号,也可以接收处理器(DSP)的trigger信号。

所有的CTI和CTM相连,因此可以实现多个CTI之间的trigger信号的相互发送与接收。

2、coresight组件的种类

2.1、control component

trigger的coresight组件

- ECT(embedded cross trigger)

- CTI(cross trigger interface):接收和发送trigger信号

- CTM(cross trigger matrix):CTI之间的trigger信号传递

2.2、trace sources

trace的coresight组件:

- ETM(embedded trace macrocells):追踪指定设备(处理器,DSP)的trace信息,每个设备(处理器,DSP)均有自己的ETM。

- AMBA trace macrocells:追踪AMBA总线的trace信息。

- PTM(program flow trace macrocells):

- STM(system trace macrocells):追踪总线互联上的trace信息

2.3、trace links

trace信息传递过程中所需要的中间coresight组件:

- trace funnel : 将接收的多个ATB总线数据合并成一个ATB总线数据

- replicator: 将一个ATB总线数据,分发成多个ATB总线数据发送

- ATB bridge: ATB 桥,用于两个不同的ATB域之间数据传输

2.4、trace sinks

最终接收trace信息的coresight组件

- TPIU(trace port interface units):将ATB数据通过trace port发送给外界

- ETB(embedded trace buffers): 存储ATB数据的buffer

- TMC(trace memory controller):

每个trace sink可以有一个trace formatter。

2.5、debug access port

DAP不属于coresight的组件,但是我们会通过DAP来对coresight的组件进行访问。

DAP包括以下:

- APB access port(APB-AP)

- AHB access port(AHB-AP)

- AXI access port(AXI-AP)

- JTAG access port(JTAG-AP)

- serial wire JTAG debug port(SWJ-DP)

- JTAG debug port(JTAG-DP)

- ROM table

DAP主要是由DP和AP组件。DP负责接收外部的JTAG或SW数据,然后转化为对AP的访问,而对AP的访问,是可以发起memory-mapped的访问。因此就可以对内部的资源进行访问。

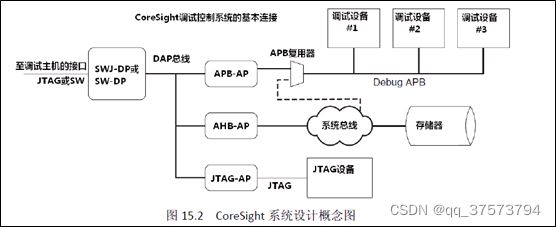

如上图,DAP包括了三个AP

- APB-AP: 对挂接到debug APB总线上的内部调试设备的访问

- AHB-AP: 对挂载在AHB系统总线上的设备的访问

- JTAG-AP: 对JTAG设备的访问。这个是兼容以前较早的ARM处理器,如ARM9。这些较早的处理器内部是用JTAG来调试的。但是现在的ARM处理器,已经不用这种方式,统一用memory-mapped方式进行调试。

目前的ARM soc中,一般至少会包括一个DAP。而一个DAP可以包括1-256个AP(access port),AP受DP的控制。只有对AP的访问,才可以转化成memory-mapped总线,对soc的内部资源进行访问。

DP中有一个SELECT寄存器,该寄存器用来选择,DP对AP的访问,是针对于哪一个AP进行访问。

DAP中,是可以有多个AP的,而每次,只能对一个AP进行访问。因为需要对AP进行编号,编号的值就在APSEL位域中。因为这个位域有8位,因此DAP中可以最多有256个AP。

DAP的内部结构如下图:

包括了一个DP,和3个AP,依次是AHB-AP,APB-AP,JTAG-AP。

DP通过JTAG或者SW管脚,连接外部的debugger,和外部debugger进行通信。

DP接收到外部debugger发送的JTAG或SW数据,转化为对内部AP的访问。经过decoder模块,判断是对哪一个AP进行访问,然后将访问信息发送给对应的AP。AP接收到DP的访问后,转化为对应的总线访问,去访问内部资源。然后将访问的信息,才回送给DP,DP再通过JTAG或SW,将访问信息返回给外部的debugger。