Verilog刷题HDLBits——Exams/2014 q4b

Verilog刷题HDLBits——Exams/2014 q4b

- 题目描述

- 代码

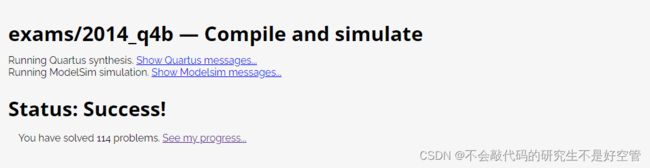

- 结果

题目描述

Consider the n-bit shift register circuit shown below:

Write a top-level Verilog module (named top_module) for the shift register, assuming that n = 4. Instantiate four copies of your MUXDFF subcircuit in your top-level module. Assume that you are going to implement the circuit on the DE2 board.

- Connect the R inputs to the SW switches,

- clk to KEY[0],

- E to KEY[1],

- L to KEY[2], and

- w to KEY[3].

- Connect the outputs to the red lights LEDR[3:0].

(Reuse your MUXDFF from exams/2014_q4a.)

代码

module top_module (

input [3:0] SW,

input [3:0] KEY,

output [3:0] LEDR

); //

reg[3:0] q,R;

reg clk,E,L,w;

assign R = SW;

assign clk = KEY[0];

assign E = KEY[1];

assign L = KEY[2];

assign w = KEY[3];

MUXDFF md1(clk,E,L,w,R[3],q[3]);

MUXDFF md2(clk,E,L,q[3],R[2],q[2]);

MUXDFF md3(clk,E,L,q[2],R[1],q[1]);

MUXDFF md4(clk,E,L,q[1],R[0],q[0]);

assign LEDR = q;

endmodule

module MUXDFF (input clk,E,L,w,R,output q);

always@(posedge clk)

q<=L?R:(E?w:q);

endmodule