SAR ADC系列19:上机实践XXX(2023.8.1更新版——比较器完整版new)

- 在电流和负载电容一定的情况下,如何做到2个不同增益的单级OP的GBW相等?

GBW = gm/CL,CL一定,设置gm一样。 - Lewis-Gray Latch比较器改进型在VOS的性能提升主要体现在哪里?

Latch开始比较时,输入管处于饱和状态,增益较高,可以将第二级对Offset的影响压的很低 - IOS的优缺点

运放输出不会饱和,但是Pre-AMP的失调电压不能完全消除,残存失调为Vos/(A+1) - OOS的优缺点

Pre-AMP的失调电压可以完全消除 ,容易使输出饱和,产生非线性的失真 - OOS结构中,电容上下极板该如何区分?(假设下极板对GND有20%寄生电容)

不知道,上级板接下一级吧?

上机实践1:

电流和负载电容自己随意定

上机实践2:Lewis-Gray Latch和改进型VOS对l比

上机实践3:Latch比较器噪声特性

tran-option,calculator写offset表达式,跑蒙特卡洛。

上机实践4:Latch比较器的工作速度

上G。

(以下是2023.8.1更新内容)

比较器需要考虑的因素:

常见的精度(失调、噪声、判决电压)、建立时间(带宽、再生速度)、灵敏度(增益)就不说了

特色的:

亚稳态:信号较小的时候,比较出结果的时间过长,可能到hold结束都没有判决出结果,这在异步逻辑里是很致命的,any decision is better than no decision!

过驱动恢复时间:比较器工作在大信号,非线性状态,不同于工作在小信号,线性状态的放大器,其复位时间相对较长。

输入电容非线性:比较器的输入电容随输入信号的共模电压的变化而变化,带来信号相关非线性。

回踢噪声:比较器的输出是个在0-1之间翻转的大电压,输入是个很小的电压,输出电压翻转的时候,会通过栅极寄生电容耦合到输入,引起输入信号的改变(向相反方向),输入信号很小,很可能受影响导致比较器判决出错。

CMRR和功耗就不说了。

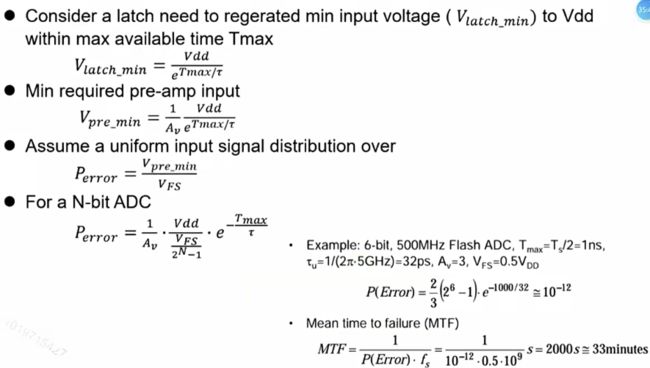

由ADC指标得到比较器对Gain 和 Speed 的要求:

可以看到,需要一个:3db-BW=200MHz,Gain = 93dB @200MHz 的运放,这是很困难的了。

可能的解决方法:单级运放(X),多级放大器级联(√),Latch-正反馈(√)

●精确的增益和线性通常是不必要的,取而代之的是简单、低增益、开环、宽带锁存器(正反馈)

●通过级联多个增益级可以获得更多增益

●带Latch的比较器,内置采样功能

多级运放级联

运放级联,大概就是 增益A 和 N成正比例,带宽ω 和 N成反比例。自然存在一个最佳级数N。

下图,级数N在2~4之间可以获得较小的延时,性价比高。

各种比较器延迟对比,看到最快的 还是latch,放大器级联越多并不是越快。

上图具有一定的欺骗性,图中横坐标是log底数,所以看起来latch曲线成线性。实际上,latch是正反馈,类似e指数曲线,上凹的。

Pre-AMP-Latch

即latch对大信号快,小信号放大慢,pre-amp相反对小信号快,大信号慢,pre-amp-latch,小信号被Pre-AMP放大后交由latch,可以节省时间。

亚稳态问题(右上图):提高Pre-AMP的增益;latch后接反相器整形。

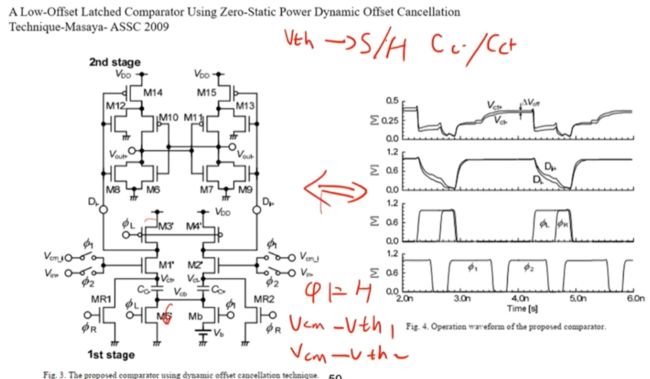

Offset 消除(前文有更具体的分析)

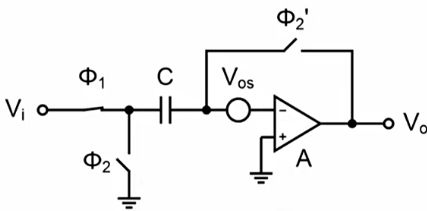

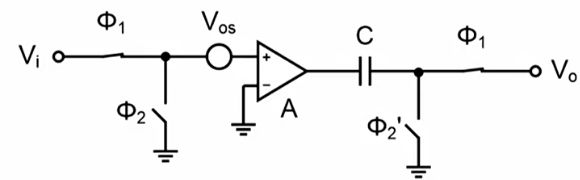

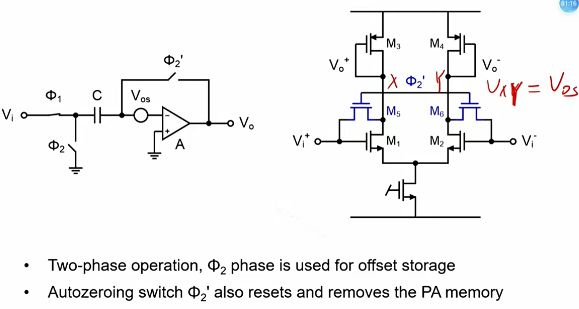

IOS:Input Offset Storage

注意:IOS工作在单位增益负反馈状态,需要考虑放大器的闭环稳定性。

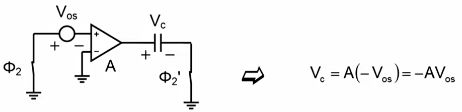

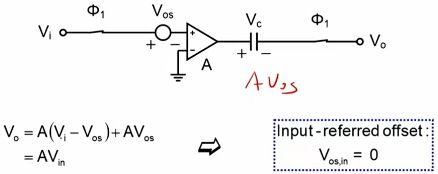

φ2相位用作存储Vos。 φ1相位用作放大信号。

缺点一:IOS并不能完全消除Vos,只能将Vos衰减(1+A)倍,好处是可以把放大器增益A做大,不用考虑饱和问题。还有一个缺点是:Vin通过AC耦合过来的,相对来讲有一点失真。

IOS本质上也是个采样电路,故采样电路的缺点它都有,CI&CF。可以通过改进开关,加dummy,改进关断顺序,等进行一定的消。

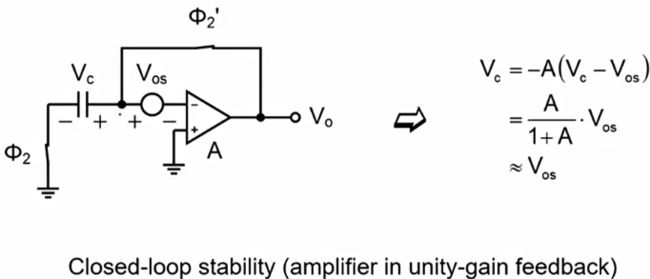

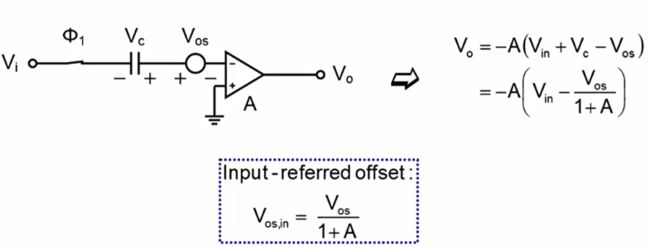

OOS:Output Offset Storage

失调存储在输出电容上面,易饱和,运放增益不能太大,并且要可控。

φ2相位用作存储Vos。 φ1相位用作放大信号。

优势一:开环工作模式,不要求闭环稳定性;优势二:也是一个采样电路,存在 CF&CI ,但是影响的是输出电容,折算到输入到除以增益A;优势三:理论上可以完全消除 offset。劣势:增益不能特别大。

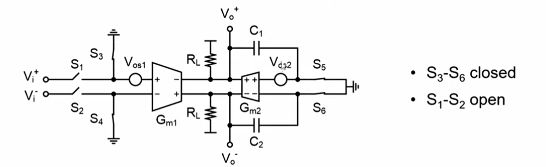

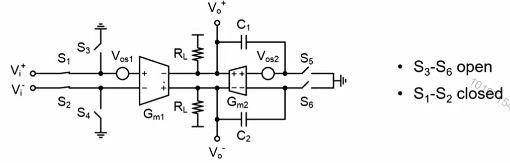

Offset Cancellation with Auxiliary Input (带辅助运放的失效消除)

将Latch的offset也考虑进来了,并把latch的offset消除掉

φ2相位用作存储Vos。 φ1相位用作比较信号。

存储Vos相位:S5&S6和S3&S4闭合,打断latch正反馈,并且输入接ac_gnd,对Pre-amp和latch来说,都是OOS,Vos1*Gm1 & Vos2*Gm2,都存储在电容C1&C2上面。

比较相位:先断谁?S5&S6先断开。S5&S6是将C1&C2接地的开关,连到ac_0上,跟输入信号没关,对应电容下级板;并且,开关产生的CI&CF会被Gm2调制一下,折算到输入要除以一个A增益。

问题:

①电路稍复杂,正反馈回路有电容,也在运放输出节点上,拖慢速度,slow speed。

②C1&C2 寄生电容加载在输出端。

③要求S5&S6阻抗非常低,否则断不开正反馈(PFB),有可能还存在PFB,容易饱和

④S5&S6断开时的CF&CI需要匹配,因为在正反馈回路,S5&S6的注入不匹配的话,而Pre-AMP输出又较慢的话,会引起latch正反馈,cover掉Pre-AMP的输出,引起错误。

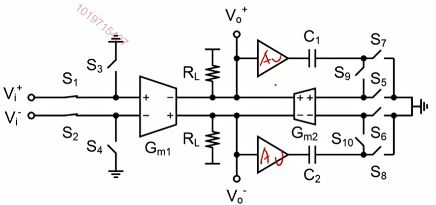

改进:

正反馈回路插入了一个放大器隔离开latch的输入和输出。①C1&C2不是加载在latch的输入(Pre-AMP的输出)节点,该节点看到的电容知识放大器的栅电容,很小。②S5&S6的CF&CI经过放大器的衰减之后在加到latch输入端,相对来说不那么容易触发正反馈了。(放大器要快)

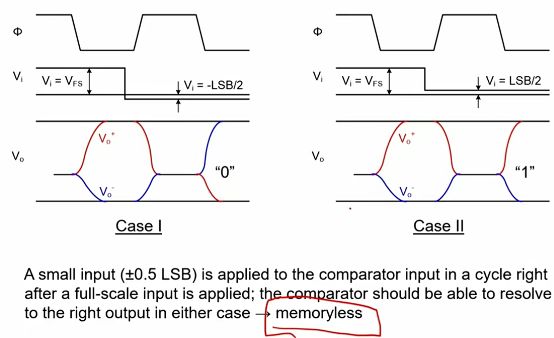

Overdrive Recovery Test(过驱动恢复)

想要比较器memoryless,不要记忆前一次比较的结果,使得前一次比较结果对下一次没有影响。

改进:每次比较之后进行复位reset。

具体电路实现——Pre-AMP:

上图Pre-AMP-latch结合在一起,很快,本质还是Pre-AMP。因此需要M3&4的尺寸大于M5&6的尺寸,保证是负反馈。并且这种结构存在迟滞线下(类似迟滞比较器)。

注意:分析 CMRR 是不考虑 offset 的,但是要考虑 mismatch。

电阻负载的好处就快,非常快,缺点就是增益不稳定,受RL控制,受PVT影响更大。

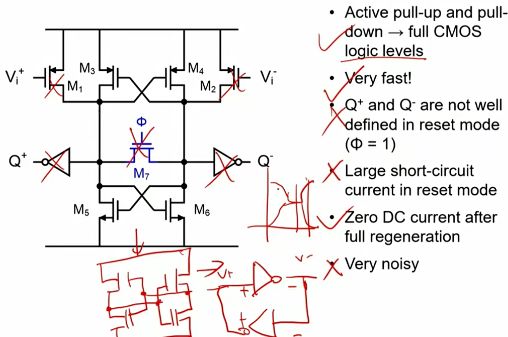

具体电路实现——Latch(背靠背的反相器):

原始电路——静态latch,存在DC功耗:

影响offset:①输出管子的尺寸,Vth,mismatch;②输出节点寄生电容mismatch;③反相器尺寸。

改进版1——reset后没有DC电流:

缺点:复位到gnd,进来的比较信号较小时,建立速度较慢。

改进版2——应用较少:

低噪声,高增益,速度快,但是不能 rail-torail 输出(full logic levels)

改进版3——Dynamic Latch 动态锁存器(常用):

好处:没有DC电流,输出rail-to-rail,复位到0。建立速度取决于Vin信号的大小。

原理:

φ =0:reset,M7&8导通,M9&10关断,P&Y上拉到Vdd,Q+&Q-复位到0,Vin复位到Vcm上。

φ =1:comp,M7&8关断,M9&10导通,P&Y点受 Vi+&Vi- 的变化,正反馈迅速拉倒Vdd和0。

注意:P&Y 在比较阶段一开始是在VDD,当M9&10导通一瞬间,P&Y同时要往下掉,有掉到X&Y点相同电压的趋势,但是由于Vi+&Vi-大小不一样,导致P&Y点下降速度不同,此时正反馈还没形成,因此一开始P&Y电压是以不同的速度一块下降的。当某一点的电压率先下降超过 Vth,此时M5&6有一个导通,反相器开始工作,正反馈形成,迅速将P&Y点电压分开,一个回到Vdd,一个下拉到 gnd。

缺点:XY一开始在一个较低的电压上,没有明确的值,开始比较时,建立速度可能会较慢。

改进版4:

所有节点都有一个明确的reset电平,开始比较时,对Vin提供一个Pre-AMP的能力,提高速度。

原理:

φ=0:reset:M7&8导通,M9&10关断,将 P&Q = Vdd;即M3&4的 gate=Vdd,M3&4也是导通的,X&Y电压 = X'&Y' 电压,接近Vdd。

φ=1:comp:P&Q = X&Y = X'&Y' = Vdd ;M1&2偏置在饱和区,M1&2相当于一个CS放大器,对Vin提供一定的预放大能力,比较结果能够快速建立。同时饱和区的mos抗噪能力也较好一点。

Offset来源:①各个节点的寄生电阻;②输入对管的失配。

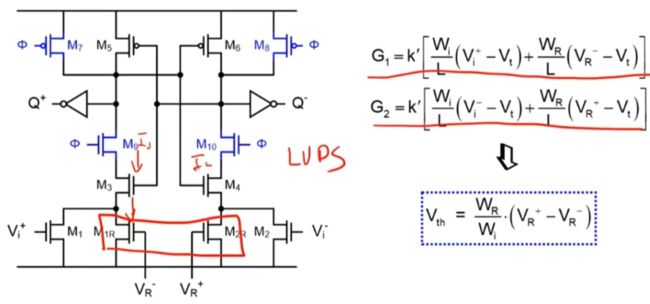

改进版5——阈值电压调整版:

正常情况是 Vi+ 比 Vi- 多&少一点点,立马比较判定。M1R&M2R的作用是调节翻转的阈值电压。还有一个作用是:可以用作Offset Calibration(失调校正)。我们知道,这种结构Latch的主要Offset来源是M1&2的Vth失配,使得I1&2的电流下降速度不一样,导致Offset。

解决Offset的方法:①在下降速度快的路径上加CL,校准&tramming。缺点是:拖慢速度。

②就是这种结构,M1&2的Vth失配,使得I1&2的电流下降速度不一样,I1&2的大小不一样,加上M1R&M2R调节I1&2的电流。

改进版6——Double Tail(双尾式):

工作原理:

clk=0:reset,M5-close,M1&2-Q-source-follow,M3&4-open,X&Y=Vdd,M8&9-open,CMPout+&-=gnd,M6&7-close and M10&11-open,P=gnd,M12-closed,not dc-current。每个点都有确定的电平。并且M1&2的漏极为Vdd,工作在饱和状态,Pre-AMP预防大。

clk=1:M3&4-close,M5-open,M1&2的漏极为Vdd,工作在饱和状态,Pre-AMP预防大。Vin+&-控制M1&2导通,将X&Y电流泄放掉(速度不一样),M6&7&8&9&10&11-typical-Latch。M12-open,tail-source。

好处:①工作在低电源电压。②full logic level。③fast,比较一开始M1&2的漏极为Vdd,工作在饱和状态,Pre-AMP预防大。④low kick back noise。不同于前面的结构,output 能直接耦合到 input;本结构,output kick back X&Y,then kick back input。X&Y 对 input 的回踢噪声是个共模的。

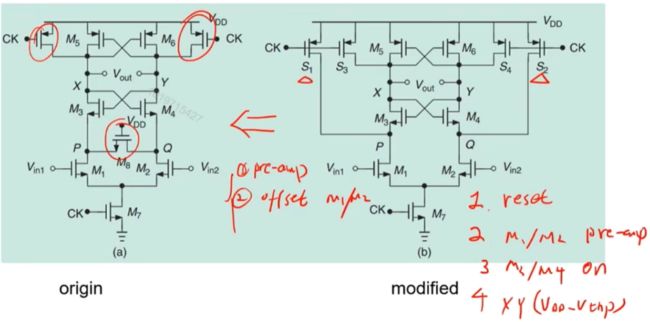

改进版7——Strong ARM Latch

Origin:画圈的三个管子进行reset,P&Q没有reset到Vdd,慢。

Modified:S3&4将X&Y=Vdd,S1&2将P&Q=Vdd,M1&2是有预防大能力pre-amp,更快。同时offset主要有M1&2的失配提供。

该电路明确有四种状态:①reset,②M1&2 pre-amp,③M3&4 on weak PFB,④X&Y Self-Calibrated 校准Offset,两种方法:①调节CL,②调节IL zero static ---------------------理论结束接下来写仿真相关的------------------------- 差分环路增益和带宽stb仿真可以用diffstbprobe这个器件。 仿真蒙卡的时候,mismatch 和 corner 一般是独立的,可以单独仿一个然后相加就行。仿真蒙卡的时候,先设置:option - Run options - 改成parallel;然后option - Job Policy Setup - max jobs 改多一点10个。做出柱状图。 mismatch主要来源是输入管Vth的失配。σth = A / sqrt(W*L)。Vth ± ΔVth。其中ΔVth和corner无关。通过仿真得到A,就可以通过Excel得到σth

找Vos:

输入加Vcm,叠加差分±Vdiff,DC扫描Vdiff(-20mV~20mV)对应的Vin_diff(-40mV~40mV),看输出Vout_diff,通过cross函数,找过零点,然后Vin_diff中用value函数找过零点处的值,计时Vos。后面可以对Vos进行蒙卡仿真,找σ。