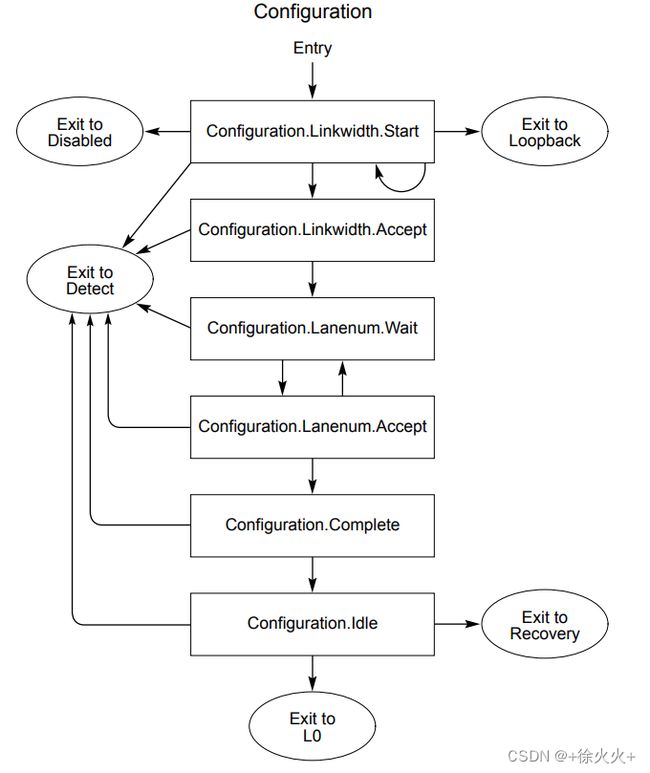

PCIE链路训练-状态机描述3

Configuration.Idle

1.当使用8b/10b编码时,non-flit模式下,在所用配置的lane上发送s Idle data Symbols,在flit mode下发送IDLE flit。

2.linkup = 0 + link两端的component均支持64.0GT/s的速率,根据进入此状态之前发送的8个TS2或收到的连续的8个Modified TS2 Ordered Sets进行如下判断:

(1)

a:收到的8个连续的Modified TS2 Ordered Sets及所有configure的lane中发送的Modified TS2 Ordered Set中的No Equalization Needed bit (bit 1 of Symbol 5)为1

b:收到的8个连续的TS2 Ordered Sets及发送的TS2 Ordered Sets中的Enhanced Link Behavior Control field (bits 7:6 of Symbol 5)为No Equalization Needed value (10b)

满足a、b两种条件之一,那么The equalization_done_8GT_data_rate, equalization_done_16GT_data_rate,equalization_done_32GT_data_rate,equalization_done_64GT_data_rate variables 设为1,64.0 GT/s Status Register中的No Equalization Needed Received bit设为1;

(2)

a:收到的8个连续的Modified TS2 Ordered Sets及所有configure的lane中发送的Modified TS2 Ordered Set中的Bypass to Highest NRZ Rate位 (bit 0 of Symbol 5)为1

b:收到的8个连续的TS2 Ordered Sets及发送的TS2 Ordered Sets中的Enhanced Link Behavior Control field (bits 7:6 of Symbol 5)为No Equalization Needed value (10b)或Equalization Bypass to Highest NRZ Rate值 (01b or 10b)

满足a、b条件之一,equalization_done_8GT_data_rate和equalization_done_16GT_data_rate variables设为1

(3)如果进入此状态是由于收到了8个连续且相同的Modified TS2 Ordered Sets,并且Linkup为0,

a:并且收到的8个连续的Modified TS2 Ordered Sets及所有configure的lane中发送的Modified TS2 Ordered Set中的Modified TS Usage field位 (bit 0 of Symbol 5)为010b (Alternate Protocols)

b:在所有配置的lane上发送和接收的Modified TS2 Ordered Sets中的Modified TS Information 1和Alternate Protocol Vendor ID fields相同

同时满足a和b条件,32.0 GT/s Status Register中的Modified TS Received bit设为1(具体的协商过程根据收到的8个连续的Modified TS2 Ordered Sets记录在Received Modified TS Data 1Register 和 Received Modified TS Data 2 Register)

3.linkup = 0 + link两端的component均支持32.0GT/s的速率,根据进入此状态之前发送的8个TS2或收到的连续的8个Modified TS2 Ordered Sets进行如下判断:

(1)

a:收到的8个连续的Modified TS2 Ordered Sets及所有configure的lane中发送的Modified TS2 Ordered Set中的No Equalization Needed bit (bit 1 of Symbol 5)为1

b:收到的8个连续的TS2 Ordered Sets及发送的TS2 Ordered Sets中的Enhanced Link Behavior Control field (bits 7:6 of Symbol 5)为No Equalization Needed value (10b)

满足a、b两种条件之一,那么The equalization_done_8GT_data_rate, equalization_done_16GT_data_rate, equalization_done_32GT_data_rate variables设为1,32.0 GT/s Status Register中的No Equalization Needed Received bit设为1;

(2)

a:收到的8个连续的Modified TS2 Ordered Sets及所有configure的lane中发送的Modified TS2 Ordered Set中的Bypass to Highest NRZ Rate位 (bit 0 of Symbol 5)为1

b:收到的8个连续的TS2 Ordered Sets及发送的TS2 Ordered Sets中的Enhanced Link Behavior Control field (bits 7:6 of Symbol 5)为No Equalization Needed value 或Equalization Bypass to Highest NRZ Rate值 (01b or 10b)

满足a、b条件之一,equalization_done_8GT_data_rate和equalization_done_16GT_data_rate variables设为1

(3)如果进入此状态是由于收到了8个连续且相同的Modified TS2 Ordered Sets,并且Linkup为0,

a:并且收到的8个连续的Modified TS2 Ordered Sets及所有configure的lane中发送的Modified TS2 Ordered Set中的Modified TS Usage field位 (bit 0 of Symbol 5)为010b (Alternate Protocols)

b:在所有配置的lane上发送和接收的Modified TS2 Ordered Sets中的Modified TS Information 1和Alternate Protocol Vendor ID fields相同

同时满足a和b条件,32.0 GT/s Status Register中的Modified TS Received bit设为1(具体的协商过程根据收到的8个连续的Modified TS2 Ordered Sets记录在Received Modified TS Data 1Register 和 Received Modified TS Data 2 Register)

4.当在Non-flit模式下使用128b/130b编码时,

(1)当前数据速率时8.0GT/s时,tx在所有配置的lane上发送SDS ordered set来开启data stream,随后发送idle data symbol在所有配置的lane上。在lane0上第一个发送的idle data symbol就是data stream的第一个symbol

(2)当前速率时16.0GT/s时,在所有配置的lane上发送SDS ordered set来开启data stream之后tx立刻发送control skp ordered set。在lane0上第一个发送的idle data symbol就是data stream的第一个symbol。

5.rx在non-flit模式下等待idle data,在flit模式下等待IDLE flit。

6.Linkup为1;

7.当在non-flit模式下使用8b/10b编码的时候,那么在全部已配置通道上接收到 8 个连续的idle data,并且在收到一个空闲符号后已经发送了 16 个idle data symbol,进入 L0 状态。注意,如果自从最后一次从Recovery状态或configuration状态进入L0时软件写了Link control寄存器中的retrain link比特,那么dsp必须将link status中的link bandwidth management status设为1;当状态转变为L0时,use_modified_TS1_TS2_Ordered_Set设为0。

8.当在non-flit模式下采用 128b/130b 编码方式,那么在全部已配置通道上接收到 8 个连续idle data symbol,并且在收到一个idle data symbol后已经发送了 16 个idle data symbol,并且不是在 Configuration.Complete 状态超时后下进入的本状态,那么跳转至 L0 状态(所谓idle data其实就是数值零经过加扰和编码之后的数值)。注意,在rx的data blocks中必须收到idle data symbol;在data stream开始处理之前lane之前的de-skew必须完成;如果自从最后一次从Recovery状态或configuration状态进入L0时软件写了Link control寄存器中的retrain link比特,那么dsp必须将link status中的link bandwidth management status设为1;当状态转变为L0时,idle_to_rlock_transitioned设为0。

9.在flit 模式下,如果收到了两个连续的IDLE flit,并且在收到一个IDLE flit之后发送了最少要求的数目的idle flit,并且进入当前状态不是从configuration.complete状态超时导致的,那么随后进入L0。(注意这里指的最少要求的数目的idle flit针对8b/10b或者128b/130b来说是4个,针对1b/1b编码是8个)。需要注意的是在data stream开始处理之前lane之前的de-skew必须完成;如果自从最后一次从Recovery状态或configuration状态进入L0时软件写了Link control寄存器中的retrain link比特,那么dsp必须将link status中的link bandwidth management status设为1;当状态转变为L0时,idle_to_rlock_transitioned设为0。

10.

未满足上述条件,2ms 超时后:

如果变量 “idle_to_rlock_transitioned” 小于FFh,那么下一个跳转状态是 Recovery(Recovery.Rcvrlock)。跳转后:

(a)8.0 GT/s 时,变量 idle_to_rlock_transitioned 自增 1。

(b)2.5 或者 5.0 GT/s 时,变量 idle_to_rlock_transitioned 设置为 FFh。

注意:该变量记录了因为配置过程没有起作用,从而导致状态机从 Configuration.Idle 状态跳转到 Recovery 状态的次数。这可能是因为均衡设置不合适,或者当前选择的速率无法正常工作导致的,Recovery 状态内会采取措施尝试解决这些问题。该变量限制了从本状态跳转至 Recovery 状态的尝试次数,从而避免了永久的无限循环。如果链路在 256 次尝试后(变量计数至 FFh)仍然没法正常工作,那么跳转回 Detect 状态重新开始,并希望这次能有更好的结果。

否则,即 idle_to_rlock_transitioned 为 FFh 时,跳转至 Detect 状态。