计算机系统结构课后题目答案

文章目录

- 第一章 计算机系统结构的基础知识

-

-

-

- 题目1.10

- 题目1.7

- 题目1.11

-

-

- 第二章 指令系统的设计

-

-

-

- 题目2.11

- 题目2.12

- 题目2.13

-

-

- 第三章 流水线技术

-

-

-

- 题目3.8

-

-

- 第七章 存储系统

-

-

-

- 题目7.9

- 题目7.10

- 题目7.11

- 题目7.14

-

-

- 第八章 输入输出系统

-

-

-

- 题目8.6

- 题目8.7

- 题目8.8

- 题目8.9

-

-

链接: https://pan.baidu.com/s/1WyftXZzso0_ePWaMDDCUPw

提取码:hu2b

第一章 计算机系统结构的基础知识

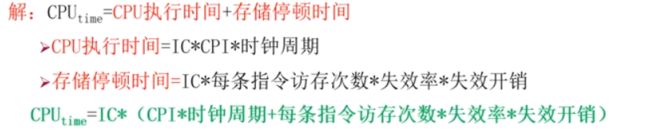

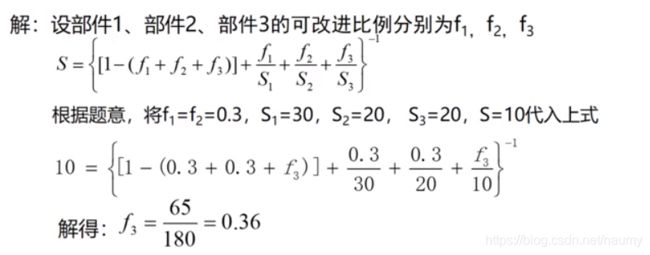

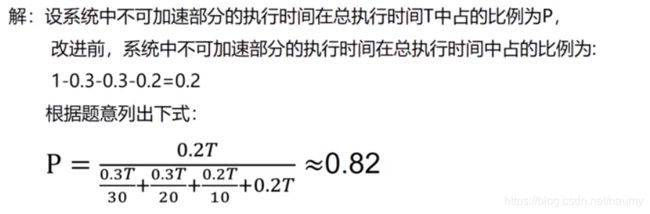

题目1.10

计算机系统有三个部件可以改进,这三个部件的加速比如下。

部件加速比S1=30,部件加速比S2=20,部件加速比S3=10。

(1)如果部件1和部件2的可改进比例都为30%,那么当部件3的可改进比例为多少时,系统的加速比才可以达到10?

(2)如果三个部件的可改进比例分别为30%,30%和20%,三个部件同时改进,那么系统中不可改进部分的执行时间在总执行时间中占的比例是多少?

题目1.7

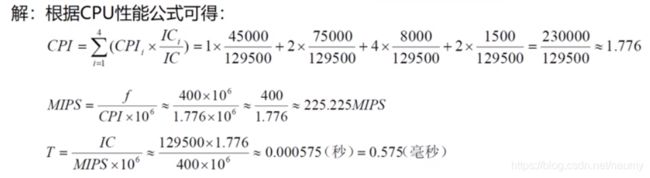

某台主频为400MHz的计算机执行标准测试程序,程序中指令类型,执行数量和平均时钟周期数如下。

| 指令类型 | 指令执行数量 | 平均时钟周期数 |

|---|---|---|

| 整数 | 45000 | 1 |

| 数据传送 | 75000 | 2 |

| 浮点 | 8000 | 4 |

| 分支 | 1500 | 2 |

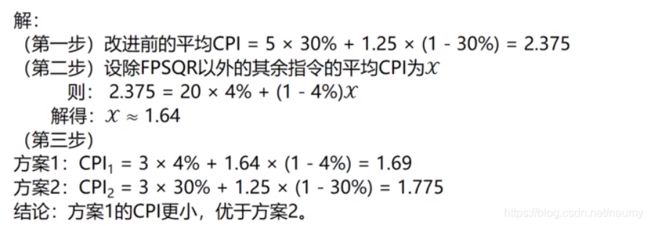

题目1.11

假设浮点数指令(FP指令)的比例为30%,其中浮点数平方根(FPSQR)占全部指令的比例为4%,FP操作的CPI为5,FPSQR操作的CPI为20,其它指令的平均CPI为1.25。现有两种改进方案,第一种是把FPSQR操作的CPI减至3,第二种是把所有的FP操作的CPI减至3,试比较两种方案对系统性能的提升程度。

第二章 指令系统的设计

题目2.11

某台处理器的各条指令的使用频度如下:

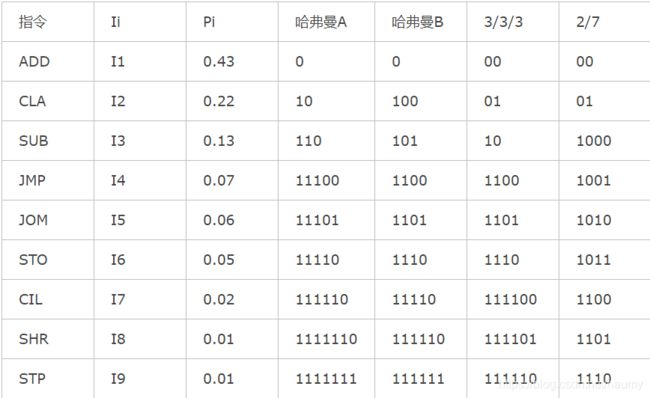

请分别设计这9条指令的操作码的哈夫曼编码,3/3/3扩展编码,2/7扩展编码,并计算这三种编码的平均码长。

解:

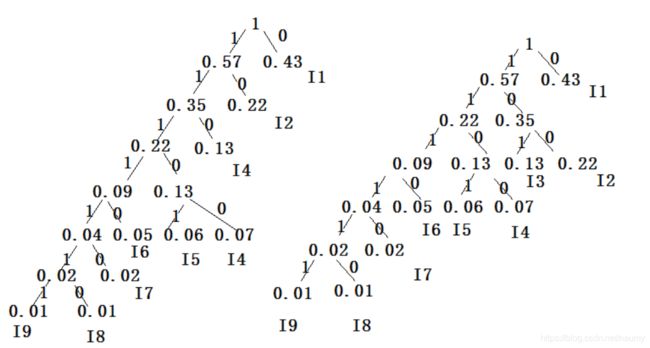

根据给出的九条指令的使用频度和哈弗曼生成算法的结构的不用构造了两种不同的哈夫曼树。

(左边为A,右边为B)

各编码如下:

由表可知,三种编码的平均码长为:(公式:L=∑Pi*Li)

哈弗曼编码:2.42位

3/3/3编码:2.52位

2/7编码:2.70位

题目2.12

某机指令字长16位。设有单地址指令和双地址指令两类。若每个地址字段为6位.且双地址指令有X条。问单地址指令最多可以有多少条?

解:

双地址指令结构为:(4位操作码)(6位地址码)(6位地址码)

单地址指令结构为:(10位操作码)(6位地址码)

因此,每少一条双地址指令,则多2^6条单地址指令,

双地址指令最多是2^ (16-6-6)=2^4=16条 ,

所以单地址指令最多有(16-X)*2^ 6条。

题目2.13

若某机要求:三地址指令4条,单地址指令255条,零地址指令16条。设指令字长为12位.每个地址码长为3位。问能否以扩展操作码为其编码?如果其中单地址指令为254条呢?说明其理由。

解:

(1)不能用扩展码为其编码。

指令字长12位,每个地址码占3位,三地址指令最多是2^(12-3-3-3)=8条, 现三地址指令需4条,

所以可有4条编码作为扩展码,而单地址指令最多为4×2^ 3×2^ 3=2^8=256条,现要求单地址指令255条,

所以可有一条编码作扩展码

因此零地址指令最多为1×2^3=8条

不满足题目要求,故不可能以扩展码为其编码。

(2)若单地址指令254条,可以用扩展码为其编码。

依据(1)中推导,单地址指令中可用2条编码作为扩展码,零地址指令为2×2^3=16条,满足题目要求

第三章 流水线技术

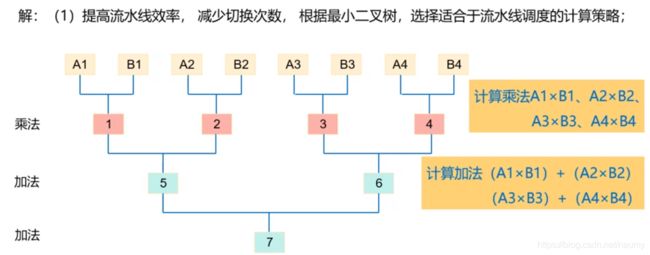

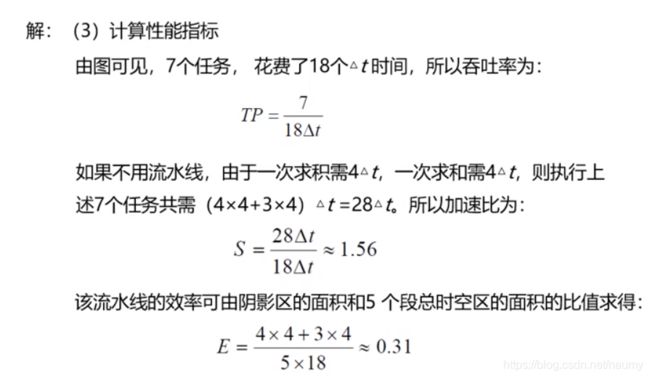

题目3.8

有一条动态多功能流水线由5段组成,加法用1、3、4、5段,乘法用1、2、5段,第2段的时间为2△t,其余各段的时间均为△t,而且流水线的输出可以自接迟回输入端或暂存于相应的流水寄存器中。现要在该流水线上计算它

,画出其时空图,并计算其吞吐率、加速比和效率。

第七章 存储系统

题目7.9

假设在3000次访存中,第一级cache不命中110次,第二级cache不命中55次。

问:该cache系统的局部不命中率和全局不命中率各多少?

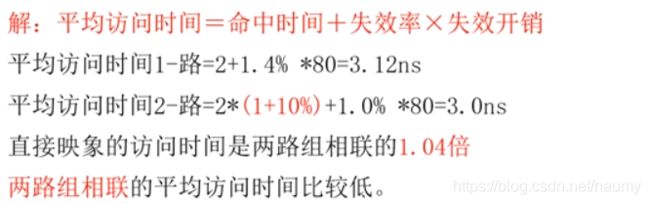

题目7.10

计算直接映象Cache和两路组相联Cache的平均访问时间以及CPU的性能。

(1)理想Cache的CPI为2.0,时钟周期为2ns,平均每条指令访存1.2次;

(2)两者Cache容量均为64KB,块大小都是32字节;

(3)组相联Cache中的时钟周期增加了10%;

(4)这两种Cache的失效开销都是80ns;

(5)命中时间为1个时钟周期;

(6)直接映象的失效率为1.4%,两路组相联的失效率为1.0%。

题目7.11

伪相联中,假设在直接映象位置没有发现匹配,而在另一个位置才找到数据(伪命中)时,需要1个额外的周期,失效开销为50个时钟周期。

假设2KB直接映象Cache的总失效率为0.098,2路相联的总失效率为0.076;

128KB直接映象Cache的总失效率为0.010,2路相联的总失效率为0.007。

试求:

(1)推导出平均访存的时间公式。

(2)利用(1)中得到的公式,对于2KB Cache和128KB Cache,重

新计算伪相联的平均访存时间。请问哪一种伪相联更快?

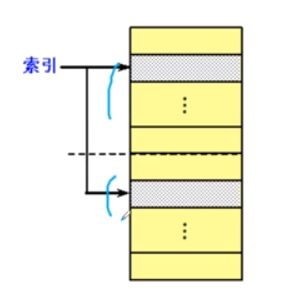

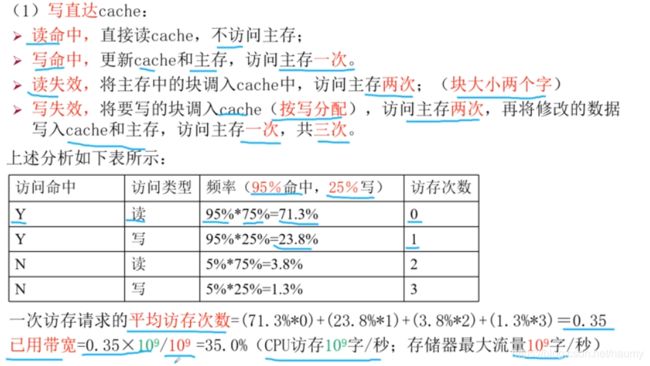

题目7.14

假设一台计算机具有以下特性:

(1) 95%的访存在Cache中命中;

(2) 25%的访存为写访问;

(3)在任何时候,Cache中有30%的块被修改过;

(4)写不命中时,Cache采用写分配法。

(5)块大小为两个字,且失效时整个块被调入;

(6)主存每次只能读或写一个字;

(7)CPU发出访存请求的速率为10°字/秒;

(8)存储器的最大流量为10°字/秒(包括读和写)

试对于以下两种情况计算主存频带的平均使用比例。

(1)写直达Cache;

(2)写团法Cache。

第八章 输入输出系统

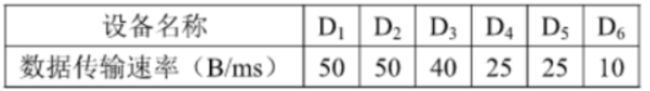

题目8.6

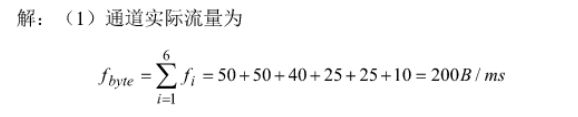

一个字节多路通道连接有6台设备,它们的数据传输率如下表所示。

(1)计算该通道的实际工作流量。

(2)若通道的最大流量等于实际工作流量,求通道的工作周期Ts+Td

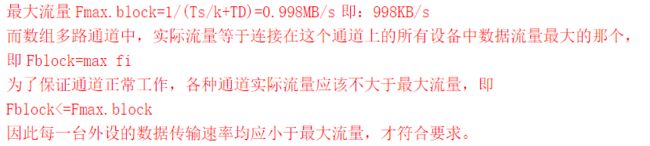

题目8.7

设某个数组多路通道设备选择时间Tg=1us,传送1个字节数据的传送时间Tp=1uls,次传送定长数据块的大小k=512B。现有8台外设的数据传输速率分别为如下表所示:

![]()

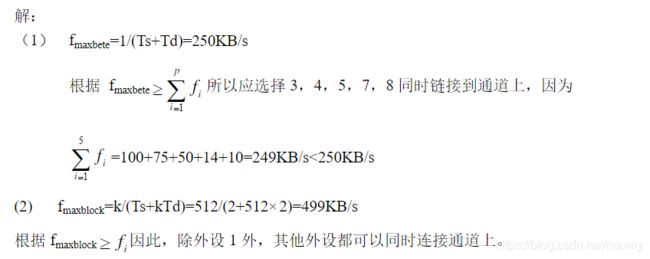

题目8.8

有8台外设的数据传输率如表所示,设计一种通道,Ts=2us,Td=2us.

(1)如果按字节多路通道设计,通道的最大流量是多少?若希望从8台外设中至少选择4台外设同时连接到该通道上,而且尽量多连接传输速率高的外设,那么,应选择哪些外设连接到该通道上?

(2)如果按数组多路通道设计,且通道一次传送定长数据块的大小k=512B,该通道的最大流量是多少?从8台外设中能选择哪些外设连接到该通道上?

题目8.9

设某个字节多路通道的设备选择时间Ts为9.8μs,传送一个字节的数据所需的时间TD为0.2μs。若某种低速外设每隔500μs发出一次传送请求,那么,该通道最多可连接多少台这种外设?