1530_AURIX_TriCore内核架构_通用寄存器以及系统寄存器

全部学习汇总: GreyZhang/g_tricore_architecture: some learning note about tricore architecture. (github.com)

继续看一下内核手册,这次了解一下通用寄存器以及系统寄存器。最近一段时间最复位以及trap困扰了许久,看看这里面是否能够获取到什么信息。

1. 寄存器从功能类别等角度的划分,之前已经在其他的地方看到了。

2. 内核特殊功能寄存器仅在初始化状态种可以修改,受到ENDINIT的保护。

3. ENDINIT机制还有一个专门的安全版本的。

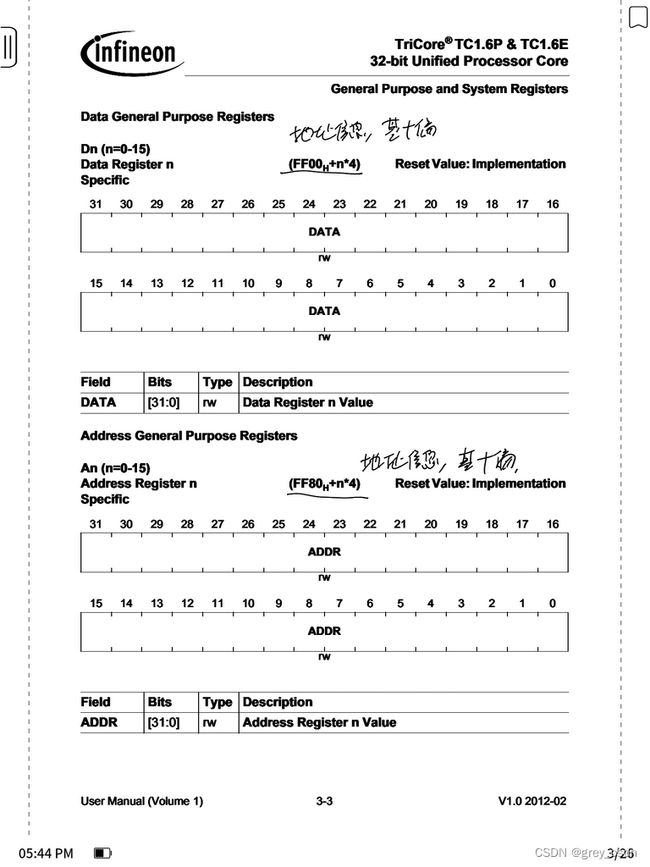

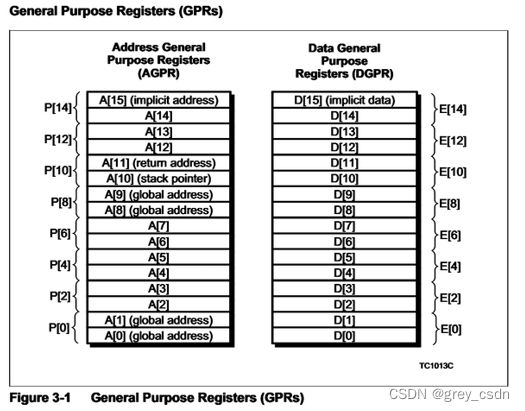

1. 寄存器从功能上来看是分为地址寄存器以及数据寄存器的。

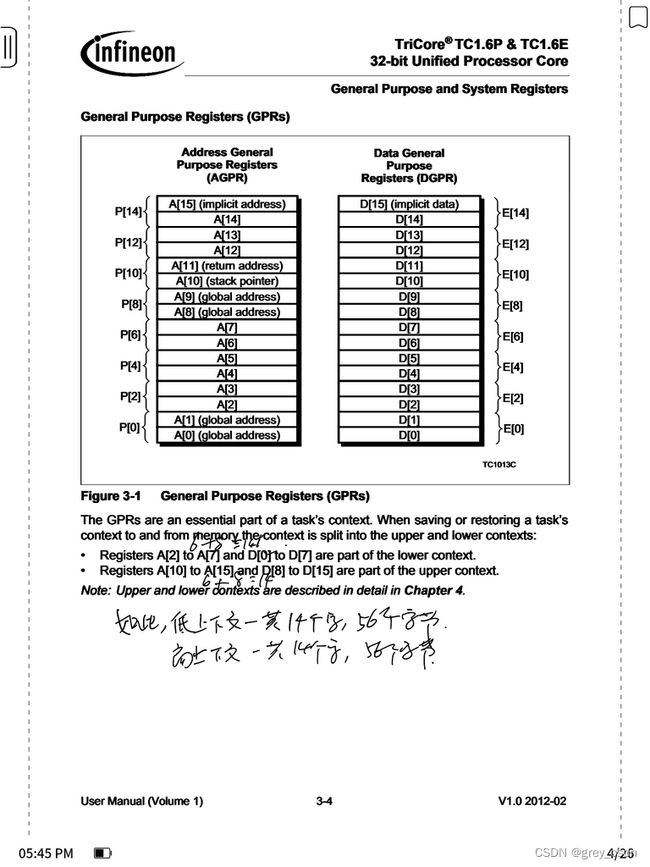

2. 寄存器A11是调用返回地址的寄存器,有点之前看到的PPC种的链接跳转寄存器的意思。

3. 16bit的执行一般会使用A15和D15两个寄存器,32bit的指令一般是没有专门的限制的。

4. 对于浮点的功能是没有单独的浮点寄存器的。

这里能够看得到这个内核手册系列中的地址表述习惯,基本上全都是基地址加偏移的方式来实现的。

看到过上下文需要64字节对齐的要求,本来想看看这里面的信息是否是64个字节。但是根据这个信息算下来,上下都是56个字节,缺一个SP的信息?

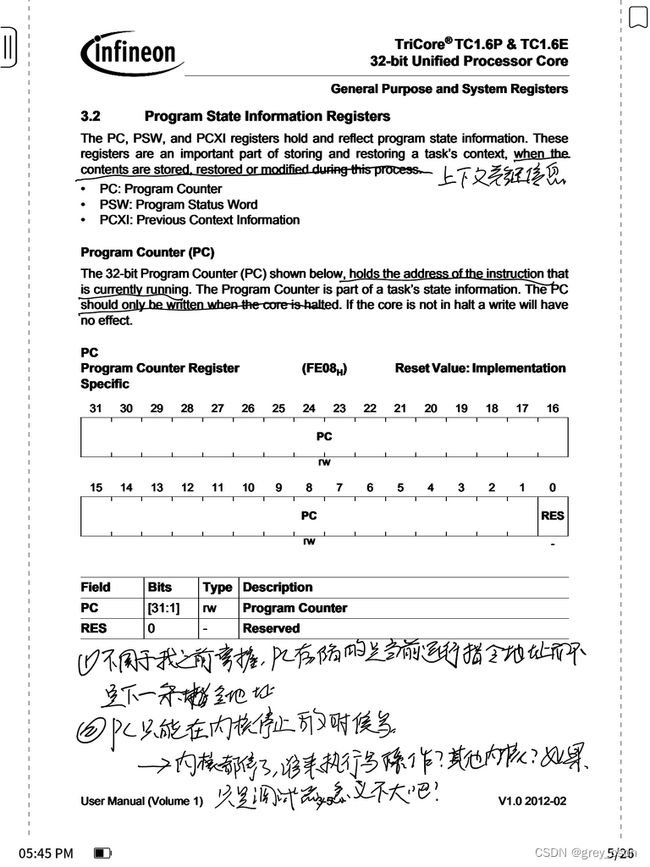

1. PC寄存器、程序状态字、前上下文信息,这些都是上下文切换的时候的一些关键信息。

2. 关于PC寄存器,我之前的理解是下一条运行指令的地址,但是从这里的描述看是当前的。

3. 如果尝试去修改PC寄存器,只能够实在内核停止的时候去修改。不过,这就有一点有趣了,如果内核都已经停了,软件还有修改它的可能性吗?

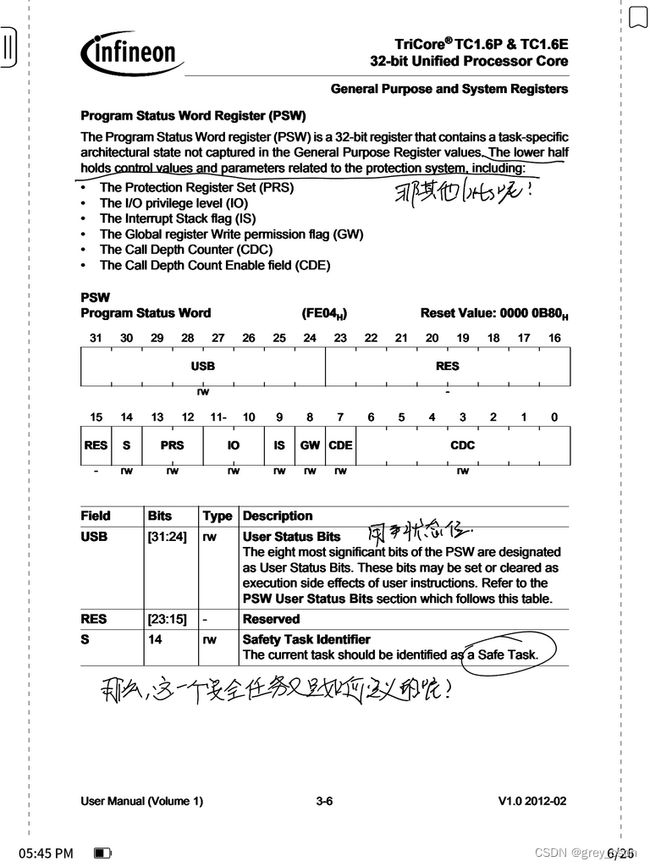

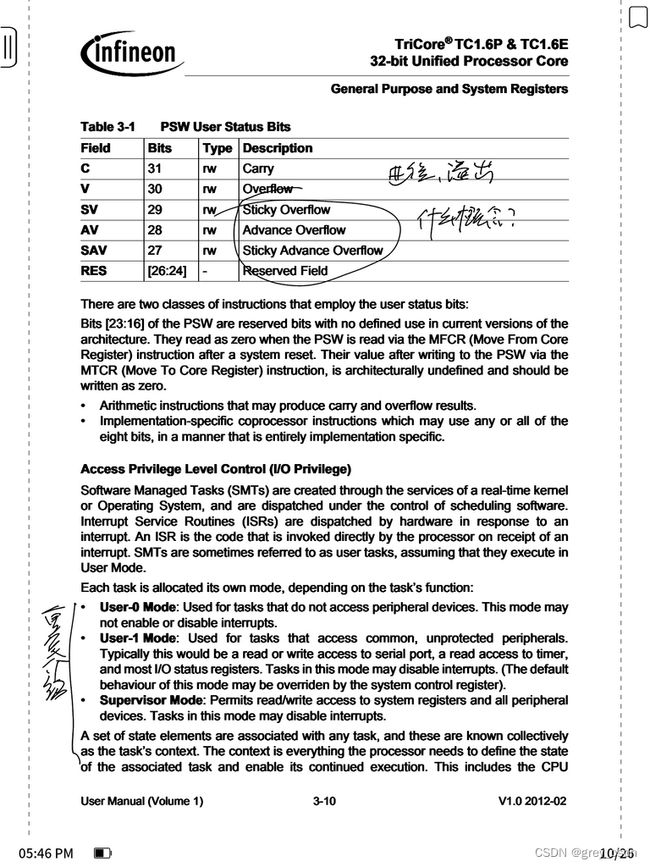

程序状态字寄存器,这个在上下文切换中还是很有意义的,尤其是IS,涉及到中断的一些条件判断。这里面还有一个信息是安全任务ID,这个又是如何处理的呢?有一些看不通。

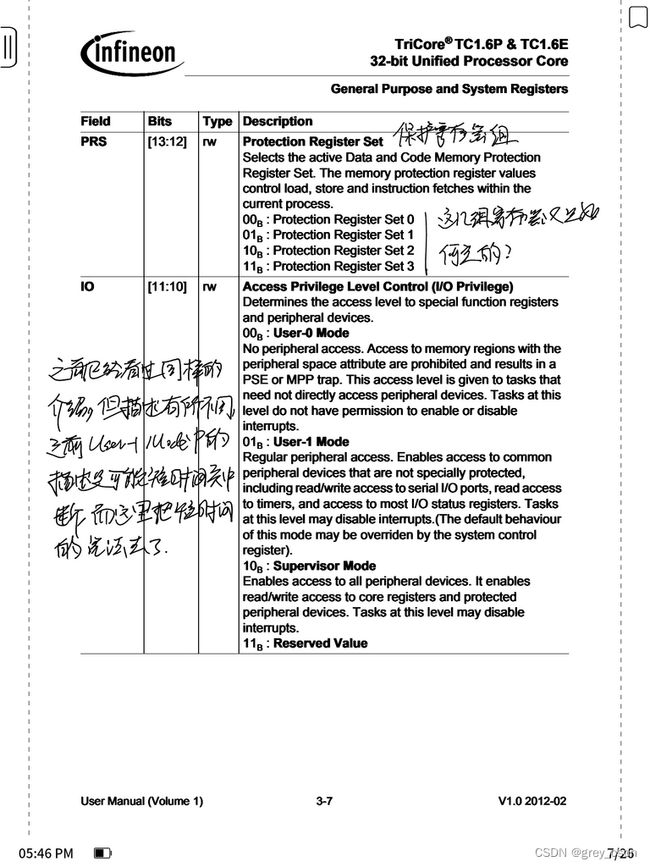

1. 保护寄存器组,没有看明白如何用,那就暂时先保持一个这样的概念。

2. 几种不同的模式之前已经看过了,不过针对User-1的模式,有些地方的描述是不同的。针对中断处理的说明,其实不是关闭,而是短暂关闭。

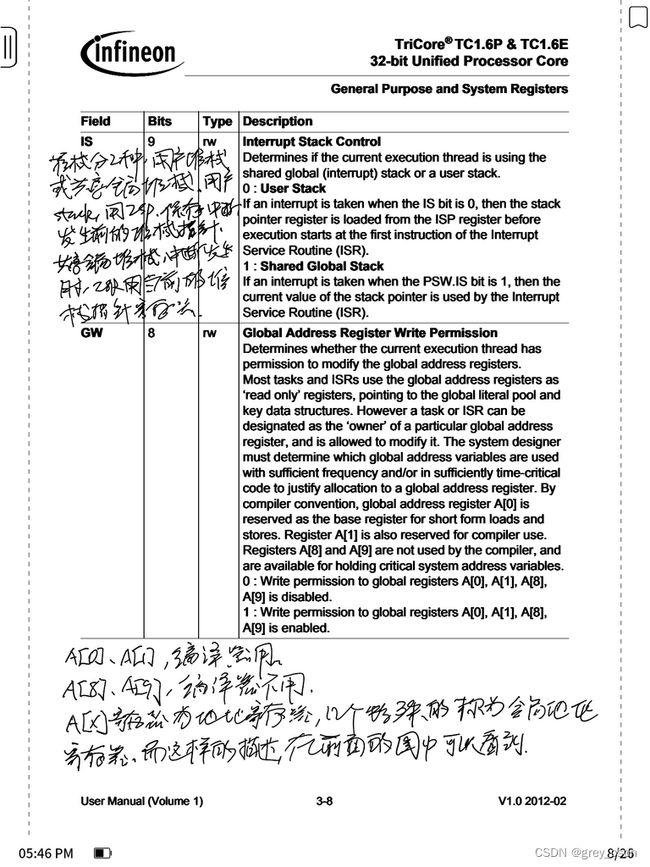

1. IS,前面大概也自己提示预警了一下。这个会用来区分用户堆栈还是共享全局堆栈。前者,会使用ISP的信息作为SP的数值,而后者则是使用当前SP的信息。

2. A0、A1两个寄存器是编译器用的,而A8和A9shi编译器不会用的。

至于哪些寄存器是全局地址寄存器,可以结合这个图来看。

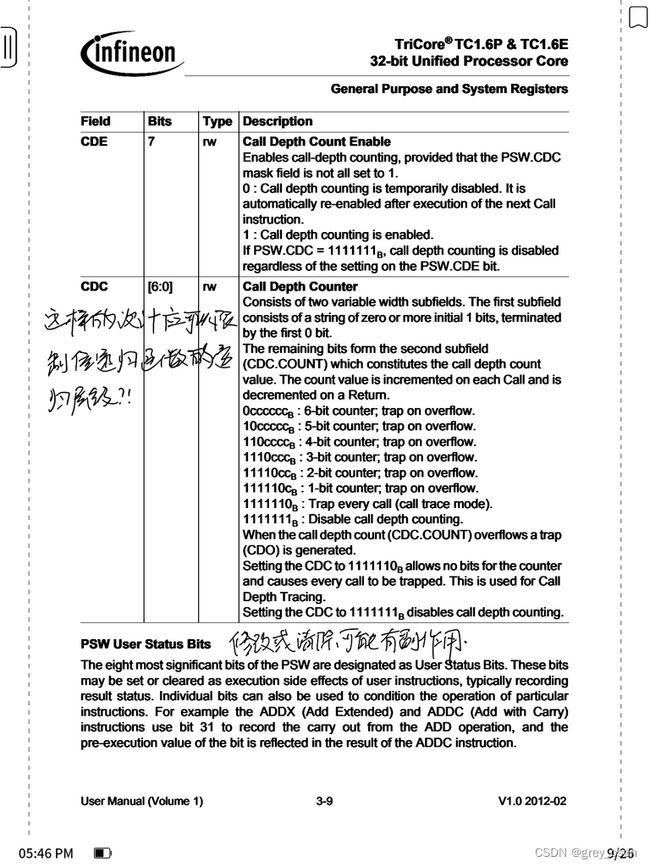

1. 关于调用深度的计数器,感觉上应该是可以用来限制软件递归调用的层级。我现在用的个人计算机应该是有这样的限制的,不知道理解的点是否一致。

2. 程序状态字的用户状态位修改或者清除可能会有副作用。

程序状态寄存器的另外一个作用就是判断是否进位以及溢出等结果发生。

这部分前面其实也有描述的,上下文的切换在这个芯片架构上是硬件来实现的。

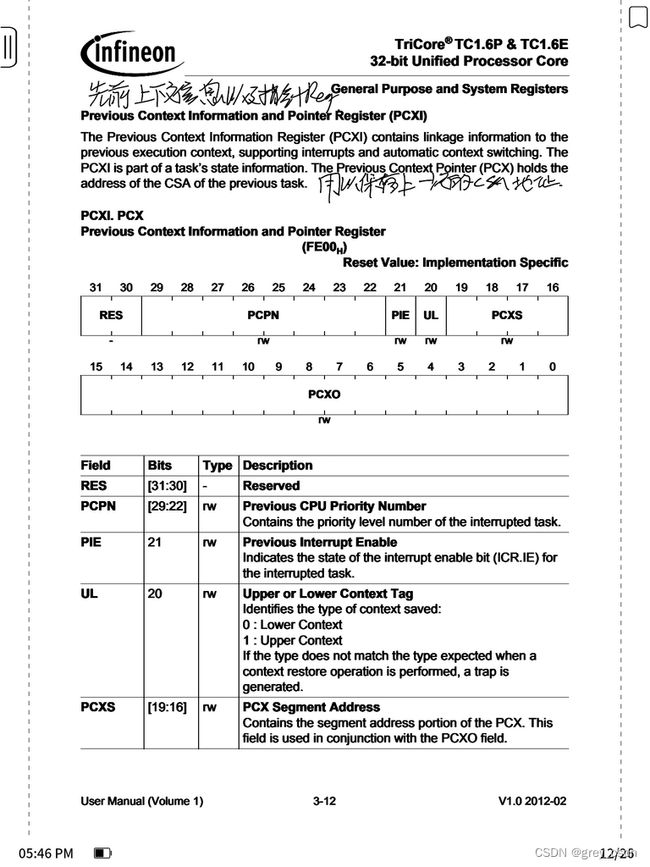

这个寄存器的存储信息是先前的上下文信息以及指针寄存器,其中PCX可以用来存储上一次的CSA的信息。

1. 堆栈管理一般是涉及2种中断以及3个寄存器。两种堆栈是用户堆栈以及中断堆栈,三个寄存器一个是SP一个ISP还有一个PSW。

2. OS用的堆栈SP一般是A[10]。

3. 架构实现了ISP的切换,但是没有实现对SP的切换。

4. 如果task被中断的时候,正在使用中断堆栈,那么SP寄存器不会进行预加载而是继续使用中断寄存器。其实,结合上面的一条可以理解,因为中断堆栈的管理是架构实现的。

5. ISP一般只需要初始化一次,但是后续是可以修改的。没有什么方式可以阻断ISR或者系统服务在私有stack(应该是用户堆栈)上的运行。

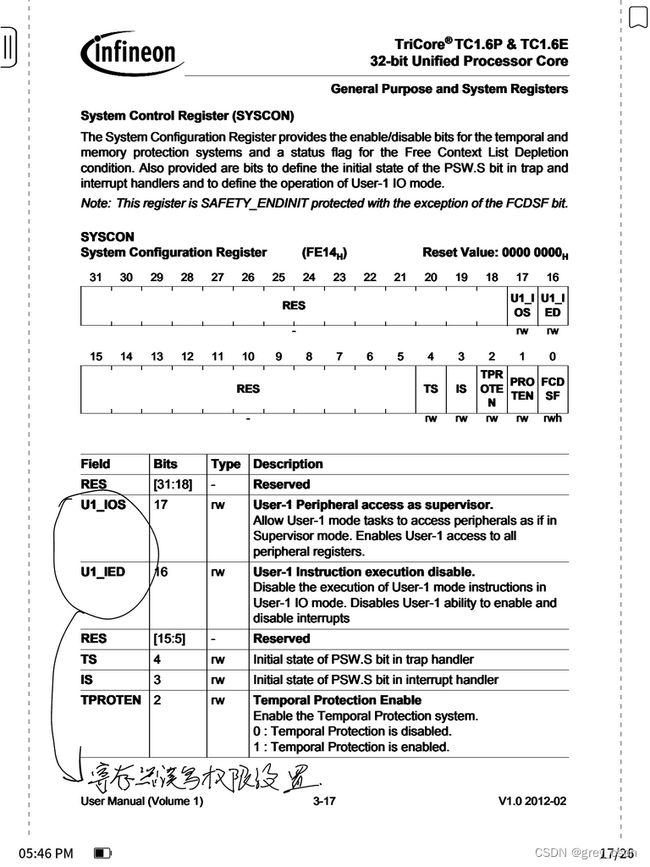

寄存器有一些读写权限的设置来控制软件对外设的访问,这个在一定程度上是可以实现安全访问的。

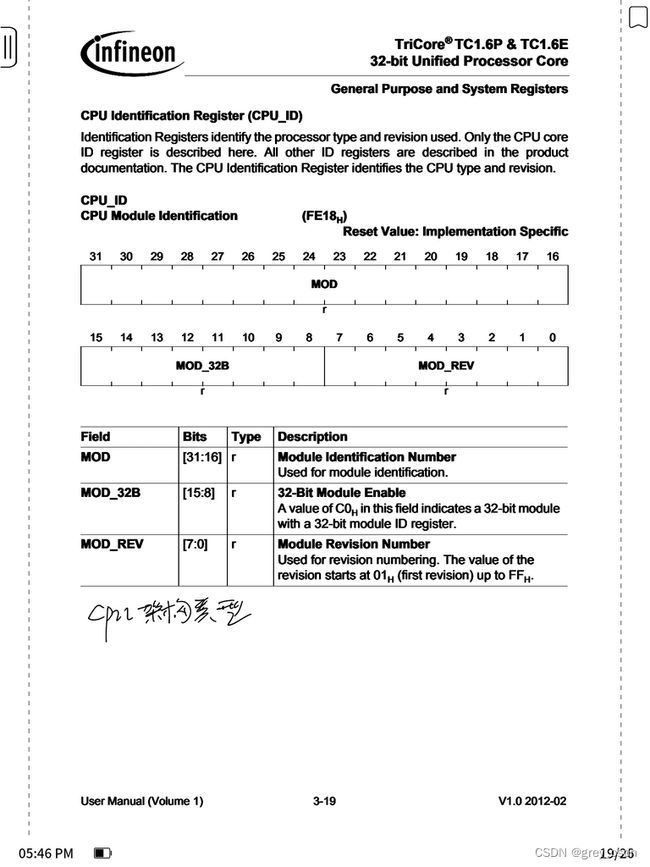

这里获得的应该是CPU的类型以及内核版本等信息。

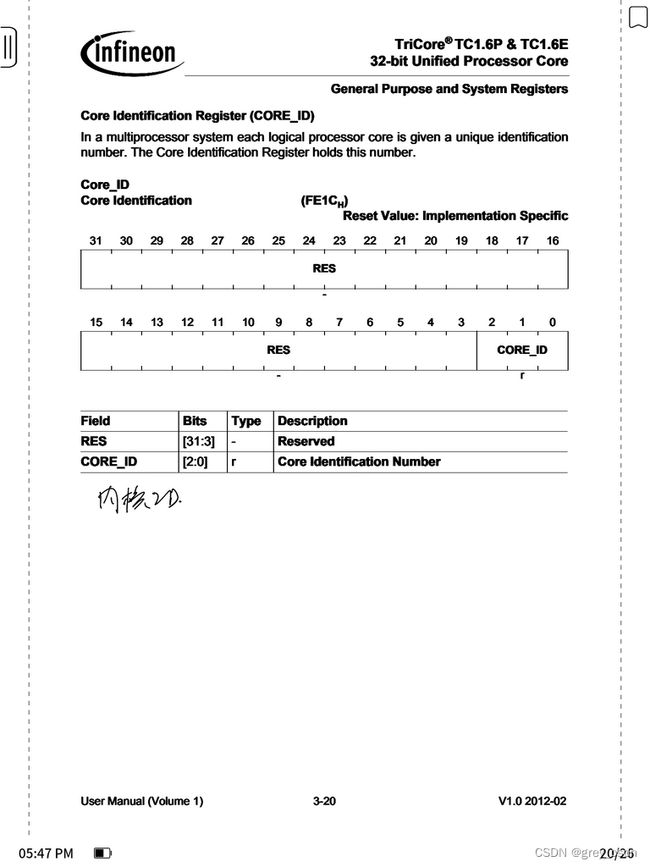

这个应该是我之前在软件中已经看过的内核ID的信息。

1. 中断寄存器可以实现:启停中断、分配优先级编号、连接到可以提供服务的模块上。

2. 存储保护使用的是一个寄存器对儿,可以提供允许访问的存储的上下区间段。

软件自动更新内核特殊功能寄存器的可能性不大。

以上的信息大概就是通用内核寄存器以及系统寄存器的大概内容,这么看下来还是有一定的收获。尤其是对于OS类的调度处理等,有了一定的硬件设计层面的理解框架。