FPGA知识汇集-ASIC移植中的FPGA芯片划分

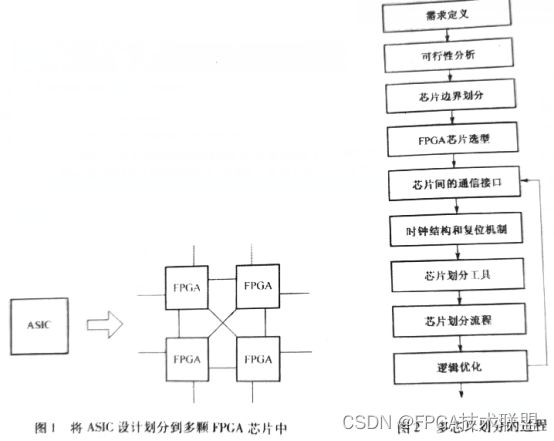

通常,FPGA单芯片难以容纳下整个ASIC设计,因此需要将整个系统划分到多颗FPGA芯片中运行(见图1),工程师往往需要借助原型验证平台来实现这样的目标。多芯片的划分绝不是简单的将不同的模板放置到不同的FPGA中那么简单,整个过程需要考虑到系统的成本、性能、规模,甚至划分的难易程度。这是一项需要反复优化的复杂过程(见图2)。为了更好的规划多芯片策划方案,工程师可以采用业界成熟的开发工具,工具内置的专用算法往往可以把整个设计更好的划分到不同的FPGA芯片中。

多芯片划分的过程大致包括以下的步骤:需求定义,可行性分析,芯片边界划分,FPGA芯片选型、定义芯片间的通信接口,定义时钟结构和复位机制,选择合适的芯片划分工具,定义芯片划分的详细流程。做完芯片划分之后,可以在不同芯片上使用不同的优化策略。

需求定义

需求分为刚性需求和弹性需求两种。诸如系统成本、平台容量、板上存储空间、最小引脚数目及一些特殊的外设(USB,PCle,Ethernet)都是刚性需求,在考虑过程中必须要满足。而像模拟器的运行速度或者FPGA的资源利用率这些都是弹性需求,只要不对平台的功能产生巨大的影响,都可以做一些折中的改变。

可行性分析

可行性分析的目的就是要确定整个设计是否需要划分到多颗FPGA芯片中。如果确实需要,那么是否能够合理地划分到基于FPGA的原型验证平台上。即便对于逻辑资源足够放在单片FPGA内的小型设计,也有可能遇到内部存储单元、信号处理单元、用户可用引脚、时钟资源不够这样的情况,因此仍然需要划分到多颗FPGA芯片中才能够实现。通过可行性分析,能够得到FPGA芯片数目、总体容量和芯片互连结构。多芯片划分过程中需要考虑到逻辑综合和物理实现的问题。复杂的芯片划分方案、芯片中占用过高的资源、不同芯片引脚之间的多路时分复用、可能出现的布线堵塞等,都会带来额外隐藏的问题。

芯片边界划分

由于大部分的ASIC芯片都是采用模块化的设计方式,因此使得多芯片的边界划分更直观和容易。SOC芯片就是很好的例子,芯片内部的功能模块多为多核CPU、高速缓存、内存控制器、外设等,它们通过系统总线进行互连,因此划分的边界也相对清晰。而GPU芯片的复杂的网状互连结构,则没有明显地划分边界,因此常常需要专业的软件工具来辅助。

FPGA芯片选型

FPGA芯片选型的经验法则是尽量选择最大容量、最高速度的芯片,这样能够减少芯之间的互连复杂度和芯片划分本身的难度。在方案的选型中,可以使用不同的芯片和非对称的片间互连结构,芯片可以有不同的容量、不同的系列,甚至来自不同的供应商。

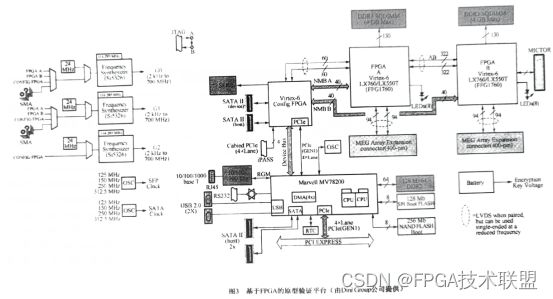

图3展示了Dini Group公司的一个原型验证平台,上面的2颗FPGA芯片采用了非对称的片间互连结构。

定义芯片间的通信接口

当整个设计被划分到多颗FPGA芯片时,设计的引脚数目会大大增加,大致可以用Rent法则(模型)进行描述;

T=t·gp

T是芯片划分后的引脚数目,g是模块的大小,p是Rent幂指数因子(取值在0.5~0. 8), t是常数。

从上述的经验公式可以看出,将整个设计划分到多颗FPGA芯片后将会大大增加其引脚数目。即便降低划分以后的模块数目,其引脚数目并不会降低同样之多。

通常,FPGA芯片之间的可用引脚越多,越利于信号之间的互连,并且减少信号之间的时分复用,从而提高整个系统的运行速度。关于该问题的详细讨论,感兴趣的读者可以持续关注公众号,后续持续更新!

时钟结构

多芯片系统的时钟分配方案非常复杂,因为需要调节不同芯片时钟之间的偏移。时钟偏移的产生来自于PCB走线和FPGA芯片。当一颗FPGA所产生的时钟作为到其他所有芯片的时钟源时,那么由于PCB布线带来的时钟偏移就必须要考虑在内,否则会带来保持时间的问题。有不同的时钟分配方案可以解决这类问题,其中之一就是采用时钟反馈环结构:时钟源从PCB 环回到产生该时钟的FPGA内部,从而平衡每颗FPGA 之间的时钟偏移。另外一种方案则是采用时钟网络复制的方法,从而消除PCB布线带来的时钟偏移。

图4说明了时钟反馈环方案的结构:外部时钟进入FPGA 1的PLL时钟管理器,PLL把生成的时钟同时发送给FPGA 2和FPGA 3、并反馈给FPGA1,这样就能够保证时钟的延迟一致性。

大规模、多时钟域的ASIC设计,可能会存在各种不同的时钟分配方案。完全使用手动的方式对这种大规模设计做多芯片划分、时钟分配方案、时钟域转换,将变得难以实现。因此需要采用自动化的多芯片划分工具来辅助整个工作。

复位机制

一个稳定的复位机制就是要在同一时间让所有FPGA芯片的逻辑达到同一个状态。因此复位延迟必须有一些限制,也会影响到同步或者异步复位机制的选择。

选择芯片划分工具

芯片划分工具可以分成3类:手动划分,自动划分,半自动划分。

对于较小的设计而言,支持手动划分的工具是比较合适的方式,它所带来的灵活性是自动划分工具无法达到的,另外也不需要支付购买工具的昂贵费用。但是手动划分需要编写和维护各种脚本,并且需要对划分后的设计重新验证,这方面的费用有时候甚至超过购买工具本身。

现在的芯片划分工具支持RTL源代码或者EDIF网表这两种方式。使用EDIF网表的优势是具有更加准确的资源评估。另外对于芯片划分工具来说,单一的 EDIF网表也更加容易找到划分的边界。而对于使用脚本而言,则更多的是支持RTL源代码的芯片划分方案。

自动化的芯片划分工具通常具有以下的功能:

-

针对特定原型验证平台的资源估计。

-

对原型验证平台做前期的可行性分析(不需要引脚分配或者FPGA芯片的互连结构)。

-

通过对引脚资源和逻辑资源的需求分析,得到优化的芯片划分方案。

-

同时支持RTL源代码和EDIF 网表作为输入。

-

支持多种第三方或者自定义的原型验证平台。

有些情况下,即便使用专业的工具也很难满足全自动化的芯片划分过程,因为某些ASIC设计的特殊需求必须要手动处理,工具对一些特殊的优化措施也很难处理、通常的做法是先对脚本做一些修改和优化,然后再使用自动化工具进行处理。

芯片划分流程

芯片划分支持‘自顶而下’和‘自底向上’两种不同的设计流程。

在“自顶而下”的划分流程中,整个设计先被综合成打平的EDIF网表,然后自动划分工具针对该EDIF网表进行处理。该流程的优势体现在可以为不同的模块提供边界优化能力,可以使用不同的约束得到不同的优化结果,因此往往可以得到时序和性能都更加优化的芯片划分方案。

在“自底而上”的划分过程中,整个设计先被划分成不同的模块,然后每个模块单独被综合并下载到不同的FPGA芯片。该划分流程更加适合于基于脚本的手动划分,并且由于每个模块对应的EDIF网表规模较小,因此能够显著的降低大型设计的编译时间。

芯片划分算法

几乎每个芯片划分工具所使用到的算法都申请了专利保护,或者是商业公司的核心资产。一个高效的芯片划分算法能够提供更快的编译时间、更高的性能、更低的资源利用率。因此是整个工具的核心。

大部分的算法使用了一个叫做”模拟退火“的方式来寻找优化的划分策略,这种算法用“图”的方式来表达打平的EDIF网表,在速度、容量、引脚数目和其他指标的约束下,工具在搜索空间中寻找最佳的方案。“图”的最佳割集就代表了最终的划分方案。

逻辑优化

完成芯片划分以后,工程师可以对不同芯片的逻辑做不同的优化,进而提高时钟速度,通过重新平衡逻辑资源而降低每颗FPGA芯片的资源利用率,或者降低FPGA的逻辑综合、物理实现时间。在优化的过程中常常会使用到逻辑复制的技术,它可以得到更高的布线成功率和时钟速度。

在所有需要优化的对象中,编译时间显得更加重要。减小编译时间可以更快的验证不同的版本,从而能够更快的发现问题。

更多有趣的话题请看链接:

FPGA知识汇集-FPGA项目开发包含那些任务?

FPGA知识汇集--FPGA结构(1)

FPGA的应用

FPGA知识汇集-在命令行模式下使用Xilinx工具

FPGA知识汇集-ISE的这些有用的工具您知道吗?

FPGA知识汇集-FPGA设计开发需要熟悉哪些EDA工具呢?

FPGA知识汇集-值得收藏的FPGA代码命名规范?

FPGA 知识汇集--Linux下ISE的环境变量设置

FPGA知识汇集-值得收藏的Verilog代码风格1

FPGA知识汇集-值得收藏的Verilog代码风格2

FPGA知识汇集-编写可综合代码(RTL)需要注意的规则总结

FPGA知识汇集-Verilog和VHDL的混合使用

FPGA知识汇集-关于Xilinx 工具报告

FPGA知识汇集-例化与推译

硬件仿真加速器与原型验证平台

FPGA知识汇集-ASIC向FPGA的移植